赛灵思(Xilinx)FPGA用户约束文件的分类和语法说明

fpGa_CPLD设计工具xilinxISE使用详解

1.第一章:FPGA/CPLD简介●FPGA一般是基于SRAM工艺的,其基于可编程逻辑单元通常是由查找表(LUT,look up table)和寄存器(register)组成。

其中内部的查找表通常是4输入的,查找表一般完成纯组合逻辑功能;●Xilinx可编程逻辑单元叫做slice,它由上下两部分组成,每部分都由一个register加上一个LUT组成,被称为LC(logic cell,逻辑单元),两个LC之间有一些共用逻辑,可以完成LC之间的配合工作与级连;●Altera可编程逻辑单元叫做LE(Logic Element,逻辑单元),由一个register加上一个LUT构成;Lattice的底层逻辑单元叫做PFU(programmable Function unit,可编程功能单元),它由8个LUT和9个register组成。

●Ram和dpram/spram/伪双口RAM,CAM(content addressable memory)。

Fpga中其实没有专业的rom硬件资源,实现ROM是对RAM赋初置,并且保存此初值●CAM,即内容地址储存器,在其每个存储单元都包含了一个内嵌的比较逻辑,写入cam的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所以内部数据的地址。

总结:RAM是一种根据地址读/写数据的存储单元;而CAM 和RAM恰恰相反,它返回的是与端口数据相匹配的内部地址。

使用很广,比如路由器中的地址交换表等等●Xilinx块ram大小是4kbit和18kbit两种结构。

Lattice块ram是9kbit●分布式ram适合用于多块小容量的ram的设计;●Dll(delay-locked loop)延迟锁定回环或者pll(phase locked loop)锁相环,可以用以完成时钟的高精度,地抖动的倍频/分频/占空比调整/移相等功能。

Xilinx主要集成的是DLL,叫做CLKDLL,在高端的FPGA中,CLKDLL的增强型模块为DCM (digital clock manager,数字时钟管理模块)。

xdc约束文件语法

xdc约束文件语法

XDC,全称Xilinx Design Constraints,是用于对FPGA设计进行约束和控制的一种常用约束文件类型。

其基本语法主要可以分为三大类:时钟约束、I/O约束以及时序例外约束。

-对于时钟约束,可以通过set_property命令设置属性值,例如设置时钟频率、IO标准等。

在设计中,根据时钟结构和设计要求来创建合适的时钟约束是非常重要的。

-I/O约束和时序例外约束也是XDC约束文件中的重要部分,主要用于规定输入输出端口的标准和处理特殊情况下的时序问题。

值得一提的是,尽管XDC是Xilinx的专有格式,但其基础语法来源于业界统一的约束规范SDC (Synopsys Design Constraints),最早由Synopsys公司提出。

这使得XDC具有很多优势,比如统一了前后端约束格式,便于管理;可以像命令一样实时录入并执行;允许增量设置约束,加速调试效率;覆盖率高,可扩展性好,效率高;业界统一,兼容性好,可移植性强。

XILINX-时序约束使用指南中文

XILINX时序约束使用指南笔记第一章 时序约束介绍第二章 时序约束方法第三章 时序约束原则第四章 在XST中指定时序约束第五章 在Synplify中指定时序约束方法第六章 时序约束分析第一章 时序约束介绍 基本的时序约束包括:“PERIOD Constraints”“OFFSET Constraints”“FROM:TO(Multi‐Cycle)约束”第二章 时序约束方法1,简介:2,基本的约束方法根据覆盖的路径不同,时序要求变成一些不同的全局约束。

最普通的路径类型包括:1,输入路径2,同步元件到同步元件路径3,指定路径4,输出路径XILINX的时序约束与每一种全局约束类型都有关。

最有效的方法就是一开始就指定全局约束然后再加上指定路径的约束。

在很多案例中,只要全局约束就可满足需求。

FPGA器件执行工具都是由指定的时序要求驱动的。

如果时序约束过头的话,就会导致内存使用增加,工具运行时间增加。

更重要的是,过约束还会导致性能下降。

因此,推荐使用实际设计要求的约束值。

3,输入时序约束输入时序约束包括2种“系统同步输入”“源同步输入”输入时钟约束覆盖了输入数据的FPGA外部引脚到获取此数据的寄存器之间的路径。

输入时钟约束经常用”OFFSET IN”约束。

指定输入时钟要求的最好方法,取决于接口的类型(源/系统同步)和接口是SDR还是DDR。

OFFSET IN定义了数据和在FPGA引脚抓取此数据的时钟沿之间的关系。

在分析OFFSET IN 约束时,时序分析工具自动将影响时钟和数据延迟的因素考虑进去。

这些因素包括: 时钟的频率和相位转换时钟的不确定数据延迟调整除了自动调整,还可以在与接口时钟相关的”PERIOD”约束中另外增加时钟不确定。

关于增加”INPUT_JITTER”的更多信息,参见第三章的”PERIOD Constraints”。

“OFFSET IN”与单输入时钟有关,默认情况下,OFFSET IN约束覆盖了从输入pad到内部同步元件之间的所有路径。

赛灵思命名规则

赛灵思命名规则

1.设备名称:设备名称由几个部分组成,包括系列名称、设备类型、芯片大小、速度等信息。

例如,XC7Z010-1CLG400C表示Zynq-7000系列的SoC芯片,大小为10,速度等级为1,封装为CLG400。

2. IP核名称:IP核的名称也包括系列名称、IP类型、版本号等信息。

例如,AXI Interconnect v2.1是一个AXI总线连接器的IP 核,版本号为2.1。

3. 工具名称:赛灵思的工具包括Vivado、ISE等,工具名称也通常包括版本号信息。

4. 文件名称:赛灵思公司的文件名称通常包括系列名称、文件类型、版本号等信息。

例如,xc7z010clg400-1.bit是一个Zynq-7000系列的比特流文件,版本号为1。

总的来说,赛灵思公司的命名规则十分规范化和严谨,为用户提供了方便和清晰的信息。

- 1 -。

赛灵思 Alveo U200 U250 数据中心加速器卡用户指南说明书

Alveo U200 和 U250 数据中心加速器卡用户指南UG1289 (v1.0) 2019 年 2 月 15 日条款中英文版本如有歧义,概以英文本为准。

修订历史修订历史下表列出了本文档的修订历史。

目录修订历史 (2)第 1 章: 引言 (4)原理图 (4)卡功能 (5)卡规格 (6)设计流程 (7)第 2 章: 卡建立与配置 (11)静电放电提示 (11)在服务器机箱中安装 Alveo 数据中心加速器卡 (11)FPGA 配置 (11)第 3 章: 卡组件描述 (13)Virtex UltraScale+ FPGA (13)DDR4 DIMM 存储器 (13)Quad SPI 闪存 (13)USB JTAG 接口 (14)FT4232HQ USB-UART 接口 (14)PCI Express 端点 (14)QSFP28 模块连接器 (14)I2C 总线 (15)状态 LED (15)卡电源系统 (15)附录 A: 赛灵思的约束文件 (16)附录 B: 法规合规信息 (17)CE 指令 (17)CE 标准 (17)合规标识 (18)附录 C: 附加资源与法律提示 (19)赛灵思资源 (19)Documentation Navigator 与设计中心 (19)参考资料 (19)请阅读:重要法律提示 (20)第 1 章引言重要提示! 除非另行说明,本用户指南适用于有源与无源版本的 U200 和 U250 卡。

赛灵思 Alveo™ U200/U250 数据中心加速器卡符合外围部件互联 (PCIe®) Gen3 x16 要求,并采用了赛灵思 Virtex®UltraScale+™技术。

这些卡可加速计算密集型应用,如机器学习、数据分析、视频处理等。

Alveo U200/U250 数据中心加速器卡支持被动散热和主动散热配備。

下图展示的是被动散热型 Alveo U200 ES1 加速器卡。

赛灵思内存使用说明

第三行开始就是数据了,每个数据用逗号","隔开,可以不分行,建议分行写,便于统计个数。

最后一个数据后用分号";"结束。

数据的个数必须和你定义的数据深度相同,否则会出错。

写好这个文件后,保存。

然后在点击LOAD FILE……,选择这个文件,点打开。

如果没有错误,可以点击旁边的show coefficients查看数据。如果数据很多(>512),建议不要使用此功能,可能会因数据太大而无法响应。

再NEXT:

这里可以选择是CLK上升沿读数据还是下降沿读。

继续NEXT:

这里比较关键,要导入ROM的值。

在LOAD INIT FILE项上打勾,点击LOAD FILE……出现下图,要你选择一个文件。

这个文件就是你要放在ROM中的数据,文件的后缀名是.COE。你可以自己建一个空的文本文件,然后把后缀名该为.COE即可。

接下来就可以综合了。

本文仅供参考学习,不得用于商业用途。

赛灵思内存使用说明

FPGA内部有BLOCK RAM和分布式RAM,这些资源都可以作为ROM(ROM只是有初始值的RAM,而且该初始值不能改变)。有些低端的FPGA可能没有BLOCK RAM。本文主要介绍ROM的使用方法,RAM的使用方法类同。

打开XILINX的ISE,NEW SOURCE中选择IP,写好NAME,点击下一步。

现在,可以点击GENERATE,产生代码了。

产生的代码中有个.MIF文件,就是ROM的数据的二进制文件。

其中的.V文件或.VHD就是生成的可综合的代码。

如上图的ROM_COS.XCO,选择它,双击VIEW HDL FUNCTIONAL MODEL

就可查看Verilog代码。

fpga语法知识点总结

fpga语法知识点总结一、Verilog语言Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统级设计。

在FPGA设计中,Verilog语言常常用于描述逻辑功能和时序控制。

Verilog语言包括模块、端口、信号声明、组合逻辑、时序逻辑、行为模拟等部分。

1. 模块:Verilog中的模块是一个最基本的组织单位,它类似于面向对象编程中的类。

每个模块都有自己的输入输出端口和内部逻辑实现。

在FPGA设计中,通常会设计多个模块来实现不同的功能,然后将这些模块连接起来,构成一个完整的系统。

2. 端口:在Verilog中,端口用于定义模块与外部环境的接口。

端口可以被定义为输入端口(input)、输出端口(output)、双向端口(inout)等,用于进行与外部信号的通信。

3. 信号声明:在Verilog中,信号用于传递逻辑信息。

信号可以是单个的位(bit)信号,也可以是多位(bus)信号。

在FPGA设计中,对信号的声明和使用是非常重要的,可以影响到设计的性能和资源占用。

4. 组合逻辑:组合逻辑是一种不含时钟的逻辑电路,其输出仅由输入决定。

在Verilog中,组合逻辑常常使用逻辑运算符和条件语句来描述。

5. 时序逻辑:时序逻辑是一种包含时钟信号的逻辑电路,其输出由时钟信号和输入信号共同决定。

在FPGA设计中,时序逻辑和时序约束非常重要,可以影响到设计的时序性能。

6. 行为模拟:行为模拟是一种用于验证设计功能和性能的技术。

在Verilog中,可以使用行为模拟语句来描述设计的行为,并进行仿真验证。

二、VHDL语言VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述数字电路和系统级设计。

在FPGA设计中,VHDL语言和Verilog语言一样,用于描述逻辑功能和时序控制。

VHDL语言包括实体、端口、信号声明、组合逻辑、时序逻辑、行为模拟等部分。

1. 实体:在VHDL中,实体是描述一个硬件单元的基本描述。

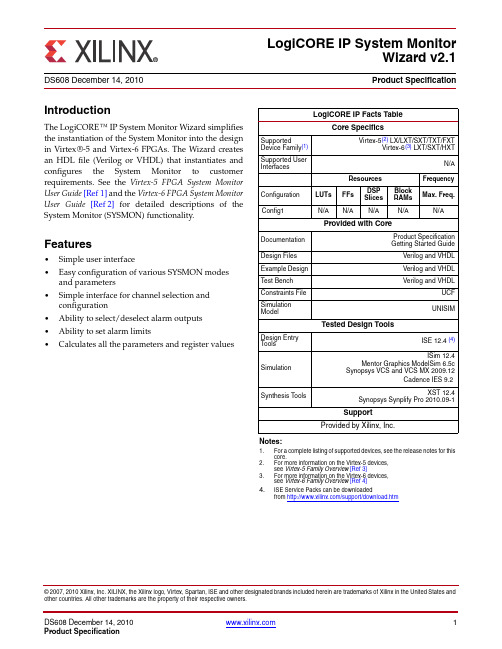

赛灵思(Xilinx)Virtex-5和Virtex-6 FPGA系统监控器向导(LogiCORE

© 2007, 2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.IntroductionThe LogiCORE™ IP System Monitor Wizard simplifies the instantiation of the System Monitor into the design in Virtex®-5 and Virtex-6 FPGAs. The Wizard creates an HDL file (Verilog or VHDL) that instantiates and configures the System Monitor to customer requirements. See the Virtex-5 FPGA System Monitor User Guide [Ref 1] and the Virtex-6 FPGA System Monitor User Gu ide [Ref 2] for detailed descriptions of the System Monitor (SYSMON) functionality.Features•Simple user interface•Easy configuration of various SYSMON modes and parameters•Simple interface for channel selection and configuration•Ability to select/deselect alarm outputs •Ability to set alarm limits•Calculates all the parameters and register valuesLogiCORE IP System MonitorWizard v2.1DS608 December 14, 2010Product SpecificationLogiCORE IP Facts TableCore SpecificsSupportedDevice Family (1)Virtex-5(2) LX/LXT/SXT/TXT/FXTVirtex-6(3) LXT/SXT/HXTSupported User InterfacesN/AResourcesFrequency Configuration LUTs FFs DSP Slices Block RAMs Max. Freq.Config1N/AN/AN/AN/AN/AProvided with CoreDocumentation Product Specification Getting Started GuideDesign Files Verilog and VHDL Example Design Verilog and VHDL Test Bench Verilog and VHDLConstraints File UCF Simulation ModelUNISIMTested Design ToolsDesign Entry ToolsISE 12.4 (4)SimulationISim 12.4Mentor Graphics ModelSim 6.5c Synopsys VCS and VCS MX 2009.12Cadence IES 9.2Synthesis T oolsXST 12.4Synopsys Synplify Pro 2010.09-1SupportProvided by Xilinx, Inc.Notes:1.For a complete listing of supported devices, see the release notes for this core.2.For more information on the Virtex-5 devices, see Virtex-5 Family Overview [Ref 3]3.For more information on the Virtex-6 devices, see Virtex-6 Family Overview [Ref 4]4.ISE Service Packs can be downloadedfrom /support/download.htmLogiCORE IP System Monitor Wizard v2.1Functional DescriptionThe System Monitor Wizard is an interactive graphical user interface (GUI) that instantiates a SYSMONbased design on specific needs. Using the wizard, users can explicitly configure the SYSMON tooperate in the desired mode. The GUI allows the user to select the channels, enable alarms, and set thealarm limits.SYSMON Functional FeaturesMajor functional SYSMON features can be used to determine an appropriate mode of operation. Thesefeatures include:•Analog to digital conversion•FPGA temperature and voltage monitoring•Generate alarms based on user set parametersI/O SignalsTable1 describes the input and output ports provided from the System Monitor Wizard. Availability ofports is controlled by user-selected parameters. For example, when Dynamic Reconfiguration isselected, these ports are exposed to the user. Any port that is not exposed is appropriately tied off orconnected to a signal labeled unused in the delivered source code.Table 1:System Monitor I/O SignalsPort Direction DescriptionDI_IN[15:0]Input Input data bus for the dynamic reconfiguration port (DRP).DO_OUT[15:0]Output Output data bus for the dynamic reconfiguration port.DADDR_IN[6:0]Input Address bus for the dynamic reconfiguration port.DEN_IN Input Enable signal for the dynamic reconfiguration port.DWE_IN Input Write enable for the dynamic reconfiguration port.DCLK_IN Input Clock input for the dynamic reconfiguration port.DRDY_OUT Output Data ready signal for the dynamic reconfiguration port.RESET_IN Input Reset signal for the System Monitor control logic and max / min registers.CONVST_IN Input Convert start input. This input is used to control the sampling instant on the ADC input and is only used in Event Mode Timing (see Event-Driven Sampling in the Virtex-5 and Virtex-6 FPGA System Monitor user guides, [Ref1] and [Ref2]).CONVSTCLK_IN Input Convert start input. This input is connected to a global clock input on the interconnect. Like CONVST, this input is used to control the sampling instant on the ADC inputs and is only used in Event Mode Timing.VP_IN VN_IN InputOne dedicated analog-input pair. The System Monitor has onepair of dedicated analog-input pins that provide a differentialanalog input.LogiCORE IP System Monitor Wizard v2.1VAUXP15[15:0]VAUXN15[15:0]Inputs16 auxiliary analog-input pairs. In addition to the dedicated differential analog-input, the System Monitor uses 16 differential digital-input pairs as low-bandwidth differential analog inputs. These inputs are configured as analog during FPGA configuration.USER_TEMP_ALARM_OUT Output System Monitor temperature-sensor alarm output.VCCINT_ALARM_OUT Output System Monitor V CCINT -sensor alarm output.VCCAUX_ALARM_OUT Output System Monitor V CCAUX -sensor alarm output.OT_OUTOutput Over-T emperature alarm output.CHANNEL_OUT[4:0]OutputsChannel selection outputs. The ADC input MUX channel selection for the current ADC conversion is placed on these outputs at the end of an ADC conversion.EOC_OUT OutputEnd of Conversion signal. This signal transitions to an active-High at the end of an ADC conversion when the measurement result is written to the status registers. For detailed information, see the System Monitor Timing section in the Virtex-5 and Virtex-6 FPGA System Monitor user guides ([Ref 1] and [Ref 2].)EOS_OUT OutputEnd of Sequence. This signal transitions to an active-High when the measurement data from the last channel in the Channel Sequencer is written to the status registers. For detailed information, see the System Monitor Timing section in the Virtex-5 and Virtex-6 FPGA System Monitor user guides ([Ref 1] and [Ref 2]).BUSY_OUT Output ADC busy signal. This signal transitions High during an ADC conversion. This signal transitions High for an extended period during calibration.JTAGLOCKED_OUT Output Used to indicated that DRP port has been locked by the JTAG interface.JTAGMODIFIED_OUT Output Used to indicate that a JTAG write to the DRP has occurred.JTAGBUSY_OUTOutputUsed to indicate that a JTAG DRP transaction is in progress.Table 1:System Monitor I/O Signals (Cont’d)PortDirection DescriptionLogiCORE IP System Monitor Wizard v2.1User AttributesThe System Monitor functionality is configured through the control registers (See the Register File Interface sections in the Virtex-5 and Virtex-6 FPGA System Monitor user guides: [Ref 1] and [Ref 2]).Table 2 lists the attributes associated with these control registers. These control registers can be initialized when the SYSMON primitive is instantiated in the HDL using the attributes listed in Table 2.The control registers can also be initialized through the DRP at run time. The System Monitor Wizard simplifies the initialization of these control registers in the HDL instantiation. The Wizard will generate the correct bit patterns based on user functionality selected through the Wizard GUI.SupportXilinx provides technical support for this LogiCORE product when used as described in the product documentation. Xilinx cannot guarantee timing, functionality, or support of product if implemented in devices that are not defined in the documentation, if customized beyond that allowed in the product documentation, or if changes are made to any section of the design labeled DO NOT MODIFY .Ordering InformationThe System Monitor™ Wizard LogiCORE IP core is provided free of charge under the terms of the Xilinx End User License Agreement . The core can be generated by the Xilinx ISE CORE Generator software, which is a standard component of the Xilinx ISE Design Suite. This version of the core can be generated using the ISE CORE Generator system v12.4. For more information, please visit the Architecture Wizards web page .Table 2:System Monitor AttributesAttribute Name Control Reg Address DescriptionINIT_40Configuration register 040h System Monitor configuration registers. For detailed information, see the Virtex-5 and Virtex-6 FPGA System Monitor user guides ([Ref 1] and [Ref 2])INIT_41Configuration register 141h INIT_42Configuration register 242hINIT_48 to INIT_4FSequence registers48h to 4Fh Sequence registers used to program the Channel Sequencer function in the System Monitor. Fordetailed information, see the Virtex-5 and Virtex-6FPGA System Monitor user guides ([Ref 1] and [Ref 2]).INIT_50 to INIT_57Alarm Limits registers50h to 57hAlarm threshold registers for the System Monitor alarm function. For detailed information, see theVirtex-5 and Virtex-6 FPGA System Monitor user guides ([Ref 1] and [Ref 2]).SIM_MON ITOR_FILE Simulation Analog Entry File -This is the text file that contains the analog input stimulus. This is used for simulation.SIM_DEVICEDevice family-This is used to identify the device family. This is used for simulation.LogiCORE IP System Monitor Wizard v2.1Information about additional Xilinx LogiCORE modules is available at the Xilinx IP Center . For pricing and availability of other Xilinx LogiCORE modules and software, please contact your local Xilinx sales representative .References1.UG192, Virtex-5 FPGA System Monitor User Guide2.UG370, Virtex-6 FPGA System Monitor User Guide3.DS100, Virtex-5 Family Overview4.DS150, Virtex-6 Family Overview5.UG741, System Monitor Wizard Getting Started GuideRevision HistoryThe following table shows the revision history for this document:Notice of DisclaimerXilinx is providing this product documentation, hereinafter “Information,” to you “AS IS” with no warranty of any kind, express or implied. Xilinx makes no representation that the Information, or any particular implementation thereof, is free from any claims of infringement. You are responsible for obtaining any rights you may require for any implementation based on the Information. All specifications are subject to change without notice. XILINX EXPRESSLY DISCLAIMS ANY WARRANTY WHATSOEVER WITH RESPECT TO THE ADEQUACY OF THE INFORMATION OR ANY IMPLEMENTATION BASED THEREON, INCLUDING BUT NOT LIMITED TO ANY WARRANTIES OR REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE FROM CLAIMS OF INFRINGEMENT AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Except as stated herein, none of the Information may be copied, reproduced,distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including,but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx.Date Version Description of Revisions02/15/071.0Initial Xilinx release.04/19/10 2.0LogiCORE IP System Monitor Wizard v2.0 release. Updated tools and version numbers. Expanded supported Virtex-5 devices. Added support for Virtex-5 TXT and FXT sub-families. Added Virtex-6 FPGA support. Added Functional Description , SYSMON Functional Features , I/O Signals , Support , Ordering Information , and References .12/14/10 2.1Updates to the Wizard and tools versions.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

赛灵思(Xilinx)FPGA用户约束文件的分类和语法说明

FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。

3类约束文件的关系为:用户在设计输入阶段编写UCF文件,然后UCF文件和设计综合后生成NCF文件,最后再经过实现后生成PCF 文件。

UCF文件是ASC 2码文件,描述了逻辑设计的约束,可以用文本编辑器和Xilinx约束文件编辑器进行编辑。

NCF约束文件的语法和UCF文件相同,二者的区别在于:UCF文件由用户输入,NCF文件由综合工具自动生成,当二者发生冲突时,以UCF文件为准,这是因为UCF的优先级最高。

PCF文件可以分为两个部分:一部分是映射产生的物理约束,另一部分是用户输入的约束,同样用户约束输入的优先级最高。

一般情况下,用户约束都应在UCF文件中完成,不建议直接修改NCF文件和PCF文件。

约束文件的后缀是.ucf,所以一般也被称为UCF文件。

创建约束文件有两种方法,一种是通过新建方式,另一种则是利用过程管理器来完成。

第一种方法:新建一个源文件,在代码类型中选取ImplementaTIon Constrains File,在File Name中输入约束文件的名称。

单击Next按键进入模块选择对话框,选择要约束的模块,然后单击Next进入下一页,再单击Finish按键完成约束文件的创建。

第二种方法:在工程管理区中,将Source for设置为Synthesis/ImplementaTIon。

Constrains Editor是一个专用的约束文件编辑器,双击过程管理区中User Constrains下的Create TIming Constrains就可以打开Constrains Editor。

需要注意的是,UCF文件是大小敏感的,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样。

但是关键字NET是不区分大小写的。

UCF文件的语法说明:1.语法UCF文件的语法为:{NET|INST|PIN} signal_name Attribute;其中,signal_name是指所约束对象的名字,包含了对象所在层次的描述;Attribute为约束的具体描述;语句必须以分号;结束。

可以用#或添加注释。

需要注意的是:UCF文件是大小写敏感的,信号名必须和设计中保持大小写一致,但约束的关键字可以是大写、小写甚至大小写混合。

例如:NET CLK LOC = P30;CLK就是所约束信号名,LOC = P30;是约束具体的含义,将CLK信号分配到FPGA的P30管脚上。

对于所有的约束文件,使用与。