DC使用教程

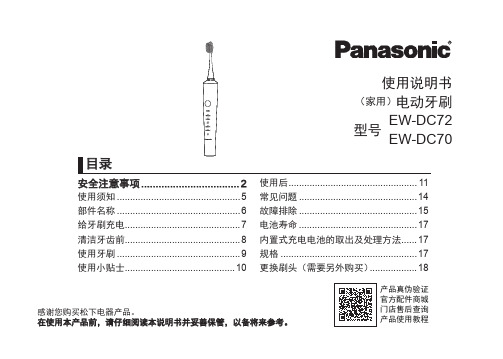

松下 电动牙刷 EW-DC70 EW-DC72 使用说明书

感谢您购买松下电器产品。

在使用本产品前,请仔细阅读本说明书并妥善保管,以备将来参考。

安全注意事项 ..................................2 使用须知 ...............................................5部件名称 ...............................................6给牙刷充电............................................7清洁牙齿前............................................8使用牙刷 ...............................................9使用小贴士 (10)使用后 (11)常见问题 .............................................14故障排除 .............................................15电池寿命 .............................................17内置式充电电池的取出及处理方法......17规格 . (17)更换刷头(需要另外购买)..................18产品真伪验证官方配件商城门店售后查询产品使用教程2警告预防意外事故请勿存放在儿童和婴幼儿的接触范围之内。

此外, 还请勿让他们接触或操作本产品。

‑ 否则可能因为不慎吸入活动部件而引发事故或 受伤。

请妥善处理本产品的包装袋,使其远离婴幼儿。

‑ 否则可能导致婴幼儿窒息等意外发生。

电源请勿用湿手将请勿用湿手将充电线充电线连接到供电电源中,或从连接到供电电源中,或从 供电电源中拔出供电电源中拔出充电线充电线。

‑ 否则可能发生触电或受伤。

请勿将请勿将充电线充电线浸入水中或用水清洗。

DC综合教程

DC操作流程

1.在虚拟机中 打开终端

DC操作流程 2. 创建综合 环境 在终端输入: new_dc xxx

xxx为你想要创 建的文件夹的名 字

DC操作流程

3. 修改环境(参考Readme

文件)

a.修改filelist.tcl 添加通过验证的源代 码

DC操作流程

b.修改synopsys.sdc 添加综合约束

DC 工具简要入门

2012年秋

内容

• 1. 逻辑综合以及综合工具

Design Compile • 2.DC操作流程

• 3.现场演示

逻辑综合

• 将RTL代码转换为门级网表 的过程

逻辑综合

DC工具

• Design Compile是常用的综合 工具,在DC中,共有8中设计 实体 • 1、设计(Design):一种能 完成一定逻辑功能的电路。设 计中可以包含子设计

• 对于DC而言,通常要指定下面4种库 • 1、Target library 工艺库,由代工厂提供的和具体工艺 相关的工艺库 • 2、Link library 指定DC查找时所指定的目标,通常 也就是Target library

DC工具--指定参考库

• Synthetic library DC综合时将转化HDL代码为相应元 件时所参考的IP库。比如符号“+”, 通过IP库查找生成某类加法器。默认 使用自带的加法库。 • Symbol library 使用图形界面时,在原理图上绘制 与非门等标准单元的符号库

DC工具

• 2、单元(Cell):子设计的实例 • 3、参考(Reference):单元的参考对 象,即单元是参考的实例 • 4、端口(Port) • 5、管脚(Pin) • 6、线网(Net) • 7、时钟(Clock) • 8、库(Library):综合时用到的一组基 本单元的集合

Design_compiler经典教程

微电子学实验室实验教程ASIC综合器软件——Design Compiler实验2006-7Design Compiler实验前言Design Compiler(简称DC)是synopsys公司的ASIC综合器产品,它可以完成将硬件描述语言所做的RTL级描述自动转换成优化的门级网表。

DC得到全球60多个半导体厂商、380多个工艺库的支持。

Synopsys的逻辑综合工具DC占据91%的市场份额。

DC是工业界标准的逻辑综合工具,也是Synopsys最核心的产品。

它使IC设计者在最短的时间内最佳的利用硅片完成设计。

它根据设计描述和约束条件并针对特定的工艺库将输入的VHDL或者Verilog的RTL描述自动综合出一个优化的门级电路。

它可以接受多种输入格式,如硬件描述语言、原理图和网表等,并产生多种性能报告,在缩短设计时间的同时提高设计性能。

本实验对DC软件的使用进行简单的介绍,熟悉和掌握综合器软件使用中的基本概念和术语,了解如何对数字电路施加约束,掌握同步数字电路设计、约束和优化的方法,了解时钟的概念,理解同步电路静态时序分析(STA)的方法和时序报告。

西安交通大学微电子学实验室实验1setup和synthesis流程实验准备有两种界面可以运行Design Compiler:1)命令行界面,dc_shell-xg-t;2)图形用户界面(GUI),Design Vision。

本次实验主要运用GUI模式。

图1.1给出了RTL逻辑综合的直观概念和简要流程。

图1.1 RTL逻辑综合的直观概念和简要流程。

在DC中,总共有8种设计对象:z设计(Design):一种能完成一定逻辑功能的电路。

设计中可以包含下一层的子设计。

z单元(Cell):设计中包含的子设计的实例。

z参考(Reference):单元的参考对象,即单元是参考的实例。

z端口(Port):设计的基本输入输出口。

z管脚(Pin):单元的输入输出口。

z连线(Net):端口间及管脚间的互连线。

DC入门实例详细教程

DC入门实例详细教程

1、课程介绍

编程入门使用DC,也称为“DC编程入门”,是一个全面的、实用的

和容易上手的入门课程,旨在帮助初学者快速学习DC和实际编程。

该课

程包括以下内容:基础知识介绍,DC软件开发环境介绍,DC编程语言介绍,DC编程实战,DC程序调试,DC应用开发,深入学习等。

2、编程入门DC基础知识介绍

DC基础知识介绍是了解DC编程的必要基础。

本章将介绍DC的基本

概念、编程环境,并在此基础上,介绍了DC编程的基本技术和工具,包括:编程语言介绍(C、C++、JavaScript、VBScript等)、编程环境设置、编程工具的选择等内容。

3、DC软件开发环境介绍

DC软件开发环境介绍指的是详细介绍DC的硬件和软件环境,这里主

要介绍了DC的系统软件安装、环境配置、编程环境设置、调试工具安装

和使用等内容。

4、DC编程语言介绍

DC编程语言介绍是指详细介绍了DC编程语言C++、JavaScript、VBScript等的基本知识,包括变量、数据类型、控制语句、循环语句、

函数等内容,同时还介绍了开发工具的使用,以及常见的错误分析等内容。

5、DC编程实战

DC编程实战是指在上述基础知识的基础上,对DC各种功能和功能配

置的具体应用。

Acrobat Pro DC基础知识教程

Acrobat Pro DC基础知识教程Adobe Acrobat Pro DC是一款功能强大的PDF编辑和管理工具。

本教程将为您提供关于Acrobat Pro DC的基础知识和使用技巧。

安装和启动安装完成后,您可以在计算机桌面上找到Acrobat Pro DC的快捷方式。

双击快捷方式,即可启动该软件。

基本界面Acrobat Pro DC的界面分为几个主要部分:1. 菜单栏:包含各种功能和操作选项。

2. 工具栏:快速访问常用工具和功能。

3. 侧边栏:提供更多选项和设置,如浏览器视图、缩略图、导航窗格等。

4. 文档窗口:显示当前打开的PDF文档。

打开和编辑文档要打开一个PDF文档,您可以使用菜单栏的“文件”选项,然后选择“打开”。

您还可以直接拖放PDF文件到Acrobat Pro DC中。

一旦打开了文档,您可以进行各种编辑操作,例如:- 添加文本:使用“添加文本”工具,单击文档中的位置,并开始键入。

- 插入图片:选择“插入”选项,然后选择要插入的图片文件。

- 修改文本格式:使用“文字属性”工具,选择文本并更改字体、大小、颜色等属性。

导出和共享文档Acrobat Pro DC还提供了几种导出和共享文档的选项:- 导出为PDF:选择“文件”->“另存为”,选择PDF格式,并指定保存路径。

- 导出为其他格式:选择“文件”->“另存为其他格式”,选择所需的格式,并进行相应设置。

高级功能除了基本编辑功能外,Acrobat Pro DC还具有许多高级功能,例如:- 添加电子签名:选择“工具”->“电子签名”,然后按照提示添加和验证签名。

- 创建表单:使用“表单”工具,将文档中的文本字段转换为可填写表单。

- OCR识别:选择“工具”->“文本识别”,然后选择识别语言并开始识别文本。

总结本教程提供了关于Acrobat Pro DC的基础知识和使用技巧,涵盖了安装和启动、界面介绍、文档打开和编辑、导出和共享文档以及高级功能等方面的内容。

dc使用教程

d c使用教程-CAL-FENGHAI.-(YICAI)-Company One1DC使用说明文件说明:在进行下面的演示时需要用到两个文件,一个是,它是描述一个电路的verilog代码,我们的目标就是用DC综合这个代码得到满足约束条件的电路网表;另一个是,它是综合的脚本文件。

这两个文件都在/home/student1000目录下,大家把它们拷贝到自己的目录下,以备使用。

DC既可使用图形界面,也可不使用图形界面而直接运行脚本来综合电路。

一、DC图形界面的使用。

1.DC图形界面的启动打开一个终端窗口,写入命令 dv –db_mode,敲入回车。

则DC图形界面启动,如下图所示红框处是DC的命令输入框,以下在图形界面上的操作都可以在命令输入框中输入相应的命令来完成。

选择Help-----Man Pages可以查看DC的联机帮助。

相应指令:man。

例:man man表示查看man命令的帮助。

man create_clock表示查看creat_clock命令的帮助。

2.设置库文件选择File----Setup需要设置以下库文件,如下图。

相应指令:set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys \ /tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys]set target_library { }set link_library { }set symbol_library { }点OK,设置完成。

3.读入verilog文件选择File---Read在打开文件对话框中选中要打开的文件,在这里我们选中文件。

在Log框中出现successfully字样表明读入文件成功。

相应命令:read_file点击红色箭头所指的按钮可以查看该电路的symbol图。

4.设置约束条件4.1设置时钟约束在symbol图上选中clk端口选择Attributes-----Specify Clock出来设置时钟约束的对话框,按下图设置,给时钟取名为clock,周期20ns,上升沿0ns,下降沿10ns。

DC系列伺服驱动器使用说明书

DC系列伺服驱动器使用说明书DC s e r i e s ser v o d r i v er u s e n g m a n u a l深圳市欧诺克科技有限公司DC 系列伺服驱动器型号说明备注: 1.驱动器供电电压必须大于或者等于电机额定电压2.驱动器的额定电流必须大于或者等于电机的额定电流DCPC-09012- OP E B系列DC/DE/DE2/BC/BC2/DH/BH制动单元B:带制动单元反馈E:光电增量式A/B 正交C:磁电增量式A/B 正交 A17:光电绝对值17bit C17:磁电绝对值17bit R:旋转变压器 H:数字霍尔 S:模拟量正余弦输入指令P:脉冲Hp:高速脉冲A:模拟量R:RS485 C:CANopen E:EtherCAT特殊功能OP:脉冲输出 OA:模拟量输出R:轮切 F:追剪 Z:攻丝机专用额定电流16:16Amps(11Arms) 50:50Amps(35Arms) 150:150Amps(105Arms)供电电压090:18-90VDC 180:18-180VDC 135:18-135VDC 220:220VAC 380:380VAC A:单相B:三相DC 系列驱动器规格汇总表驱动器型号供电电压连续电流 Amps(Arms) 峰值电流 Amps(Arms)6S 反馈类型外形尺寸重量DCPC-09002-OPE 2A (1.4A ) 6A (4.2A )133*90*32mm0.35kgDCPC-09004-OPE 4A (2.8A ) 8A (5.6A )DCPC-09008-OPE 8A (5.6A ) 24A (16A )DCPC-09016-OPE 16A (11A ) 48A (33A )DCPC-09024-OPE 24A (16A ) 50A (35A )DCPC-09030-OPE 30A (21A ) 60A (42A )167*100*35mm0.45kgDCPC-09040-OPE 40A (28A ) 80A (56A )DCPC-09050-OPE 50A (35A ) 100A (70A )DCPC-09075-OPE 75A (52A ) 150A (105A )200*114*59mm 1.10kg DCPC-090100-OPE 100A (70A ) 200A (140A )DCPC-090125-OPE 125A(88A)250A(177.5A)DCPC-090150-OPE 150A (105A ) 250A (175A )221*140*59mm 1.45kg DCPC-090200-OPE 200A (140A ) 300A (210A )221*140*90mm 1.8kg DCPC-090300-OPE 300A (210A ) 420A (294A )DCPC-090300-OPE(新) 300A (210A ) 420A (294A )265*140*90mm 2kg DCPC-18024-OPE 18~180VDC 24A (16A ) 50A (35A )167*100*35mm 0.45kg DCPC-18050-OPE 50A (35A ) 100A (70A )200*114*59mm 1.10kg 75A (52A ) 150A (105A )DCPC-18075-OPE 100A (70A ) 200A (140A )221*140*59mm 1.45kg DCPC-180100-OPE DCPC-135100-OPE 18~13518~90VDC增量式DC 系列外形尺寸图L L 1WHH 3H2H1W1H4 HW2H4 HW 3W4型号L L 1W W1W2W3W4H H1H2H3H4DC-2A~24A 14113432/ 4.5/15.5895118 4.5134DC-30A~50A 16716035/2-4.5/19.510051224-4.5160DC-75A100A 200190594-5.0/25/1146032.54-4.8190DC-100AF 200190594-5.0/25/1146032.54-4.8190DC-150A 221211595/25/1406045 4.8211DC-150AF 221211595/25/1406045 4.8211DC-200A 221211905/25/140///211DC-300A 221211905/25/140///211DC-300A (新)265255905/25/140///255DC 系列端子定义J3J1 J2 J3S1J4 J5J6 J75 4 3 2 11、产品简介:1. 1 概述DC系列可编程智能伺服驱动器是一款通用、高性能、直流供电、结构紧凑的全数字伺服驱动器。

ubuntu中DC安装详细教程(修改版)

说明:本教程在ubuntu10.04 之后,一直到ubuntu11.10 上验证成功,在之前的版本应该也以。

首先表示歉意。

由于之前发的那个教程在破解的地方少截了一张图,部分人无法找到文件,造成无法破解,对那些已经下载了的朋友造成误导,表示歉意。

为了能使更多的人正确破解并应用这个强大的软件,所以在此重新安装一次,并编写教程,顺便改正上次其他的几个小错误。

1、准备安装文件(setup 文件夹),内容如下图:2、在主目录下建立soft 文件夹,并在soft 文件夹下建立dc2012,在dc2012 下新建dc、scl 文件夹,同时把setup 文件夹也拷贝到soft 文件夹下(本教程中,主目录为lbq 文件夹,在上步骤中,已经把setup 文件夹拷贝到soft 文件夹下了)。

3、由于早期的ubuntu 默认没有安装csh,需要先打开终端,运行sudo apt-get installcsh,11.04版之后的好像都默认安装了。

然后在ubuntu 软件中心中搜索wine,并安装成功(在后面的破解中需要用到wine)。

4、开始安装。

如下图,按照图中所示路径,进入到该文件夹中,右键单击setup.sh,“”点击属性,打开选中允许以程序执行文件(E)”。

权限标签, ““”5、右键单击setup.sh,“”点击打开,如下图6“”、点击运行,如下图:7“、点击Start”,如下图:8、选择所要安装软件dc “的原程序路径。

点击Browse...”,选择路径如下图所示:9“、点击Done”,如下图所示:10“、一路Next”,遇到的几处选择如下几幅图所示,紫色表示选择。

11、直到出现选择所要安装软件dc 的保存路径时,选择安装在dc2012“下的dc”文件夹中,如下图:12“如下图,单击Install ”开始安装。

、点击Next”,“13、dc 安装结束后,不要退出。

出现下图所示内容14“、点击Install Another Product”。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

如何看时序报告:

通过产生的时序报告读出以下信息: 1)是setup time report还是hold time report? 2)时钟频率多少?

确定是setup time report还是hold time report? 看oprating conditions:worst(建立 时间),best(保持时间)。为什么? 看path type:max(建立时间), min(保持时间)。为什么? 时钟频率多少: 通过上升沿和下降沿的时间来确定

Set_load 设置输出负载

估计模块输出的时序——transition time DC默认输出负载为0. 单位由Foundry厂提供,一般是pf.

Set_max_transition 设置最大传 输时间

Transition time 是指改变某线所驱动 的pin所需要的时间,该时间的计算方 法是基于工艺库的。 输出的传输时间是输入传输时间以及输 出负载的函数关系。 DC在优化的过程中就是确保设计的所 有net的对应的传输时间小于所设定的 最大传输时间。

DC时序路径:

时间通路的划分

几个概念

数据传输需要的时间(Data Arrival Time):信号到达时间是指信号到达电 路中某一点的真实时间,一般等于信号 到达时序路径起点的时间加上信号在该 时序路径上传播所用的时间。 要求到达时间(Data Required Time): 指期望信号到达电路中某一点的时间。 时序裕度(slack):指电路中某点处要求 到达时间与实际信号到达时间的差值

起点 终点

1> 所有的基本输入端(Primary Input) 2> 所有时序单元的时钟输入端

1> 所有的基本输出端(Primary Output) 2> 所有时序单元的数据输入端

DC四种时序路径的划分

四种路径: 基本输入到寄存器 触发器到触发器 触发器到输出 基本输入到基本输出

DC的启动:

图形界面:在unix下面输入 dv –db_mode就进入dc的图形界面。 命令行界面: Shell模式:dc_shell Tcl模式:dc_shell-t

Set_operating_conditions 设置 工作条件命令

工作条件包括三方面的内容——温度 、电压以及工艺。 在Foundry提供的工艺库里,它的各个 单元的延时是在一个标准(nominal)条 件下得到的,比如说温度25.0度、工艺 参数1.0和工作电压1.8V。 工作条件一般分为三种:最好情况 (best case)、典型情况(typical case) 以及最差情况(worst case)。

建立时间和保持时间

建立时间(setup time):数据在时钟信号源 到达之前必须要稳定的时间,如果建立时间 不满足,数据不能正确打进时序逻辑单元 保持时间(hold time):数据在时钟信号源 到达之后必须要稳定的时间,如果保持时间 不够,数据被时序逻辑单元正确锁存 基本单元的延时(Tcq):门延时是指信号 通过实际的标准单元所需要的时间.在时序逻 辑单元中,反映为从时钟沿开始,到数据输 出需要的时间 . 线延时:线延时是指由于导线的阻持时间的slacks: 例:建立时间: --------------------------------------------------data required time 31.74 data arrived time -19.80 ----------------------------------------------------slack 11.94 arrived time应比required time提前 ,这样才能保证建立时间不违例。

转译(translation):

DC综合的三个阶段:

Translation 是指用HDL语言描述的电路转化为用 GTECH库元件组成的逻辑电路的过程。GTECH是 Synopsys的通用工艺库,它仅表示了逻辑函数的功 能,并没有映射到具体的厂家工艺库,也就是说独 立于厂家工艺的。 优化(optimization)和映射(mapping) : Optimization是根据设计者对电路设定延时和面积 等约束条件对电路进行优化设计的过程。它通过各 种方法尽量满足设计者对电路的要求。 Mapping把用GTECH库元件构成的电路映射到某 一固定厂家的工艺库上,此时的电路包含了厂家的 工艺参数Library Cells;

Set_max_delay 设置最大延迟

对于异步逻辑来说,异步的置位和清零 信号,并通过锁存器以及寄存器实现的, 因为reset的信号穿过一些BLOCK,因而 需要在顶层约束这个信号,约束方法如 下面的例子. 例如我们现在要设置RESET的最大时延 为5

Set_max_delay 设置最大延 迟

实际的时钟达到各个触发器的时间不是 一样的,它们之间有一个偏差,称为时 钟偏差(Clock Skew)。 为了反映这个偏差,我们在综合的时候 可以用一个命令来模拟它,即 set_clock_uncertainty。

Set_clock_uncertainty 设置时钟 不确定性

Set_false_path 设置虚假路径

例二, 规定一个从EN到RDN的 最小延迟为10的路径,设置步骤 如下: 首先选定EN &RDN两个端口( 用Ctrl键), Attribute--> Optimization Constraints->Timing Constraints… 设置相应的延迟时间点击OK, 完成设置. 对应的脚本命令为: dc_shell> set_max_delay 10 -from EN -to RDN

Set_driving_cell 设置输入驱 动

为了更加准确的估计模块输入的时序, 我们同样需要知道输入端口所接单元的 驱动能力。在默认的情况下,DC认为 驱动输入的单元的驱动能力为无穷大, 也就是说,transition time为0。 按照该单元的输出电阻来计算 transition time,从而计算输入端口到 门单元电路的延迟。

工艺库的格式

DC用到的工艺库是.db或者是.lib格式 的 .lib格式的文件是可读得,通过此文件 可以了解库的详细信息,比如说工作电 压,操作温度,工艺偏差等等。 .db格式的库是二进制的,不可读。.db 格式的库由.lib格式的库通过命令 read_lib生成。

工艺库的分类

逻辑库 物理库

Set_max_fanout设置最大扇出负 载

设置最大扇出负载约束就是指设置了某 线所能驱动的负载数量上限。 如果某线的扇出负载过重,DC可以通 过改变单元的驱动强度来修正该约束违 例的情况。

Set_clock_uncertainty 设置 时钟不确定性

理想、don’t touch

实际

Set_clock_uncertainty 设置时钟 不确定性

Set_wire_load_model设置连线 负载模型

在DC综合的过程中,连线延时是通过 设置连线负载模型(wire load model) 确定的。 连线负载模型基于连线的扇出,估计它 的电阻电容等寄生参数,它是也是由 Foundry提供的。 我们可以让DC自动根据综合出来的模 块的大小选择负载模型,这个选项在默 认下是打开的。

综合的目标

得到一个功能和时序都满足的网表: 面积最小化 功耗最小化 性能最大化

SME 授课教案 2019年2月 12日星期二

如何保证时序满足?

将电路划分为各种时序路径 计算电路中关键路径的setup time 与 hold time是否满足

DC时序通路(timing path)的 划分原理:

首先选定reset端口 ,Attribute-->Optimization Constraints-->Timing Constraints… 点击OK,完成reset的延迟设置 . 相对应的脚本命令是: dc_shell> set_max_delay 5 -from RESET

Set_max_delay 设置最大延 迟

DC的作用

DC的使用流程 DC时序报告

DC在设计流程中的位置

什么是综合

实现在满足设计电路的功能、速度及面积等 限制条件下,将行为级描述转化为指定的技 术库中单元电路的连接。

逻辑设计

约束

逻辑综合

库

门级网表

为什么要进行DC

RTL代码是理想的情况 B. 实际电路

A.

1>门的延时 2>导线的延时 3>信号的转换时间 4>时钟信号到达各个触发器的时间不相等

输入延时

那么,从输入端口经过路径N到触发器 DFF2的输入端所用的时间=时钟周期 -输入延时

输出延时

那么,数据从触发器DFF3的D端到输 出端口所用的时间=时钟周期-输出延 时 这样,整个设计的路径就全部被约束了 。

DC的使用流程

库文件简单说明

目标工艺库(Target_library): 是指将RTL级的HDL描述到门级时所需的标准单元综合库,它 是由芯片制造商(Foundry)提供的,包含了物理信息的单元 模型。 链接库(link_library): 链接库可以是同target_library一样的单元库,或者是已综合 到门级的底层模块设计,其作用如下:在由下而上的综合过程 中,上一层的设计调用底层已综合模块时,将从link_library中 寻找并链接起来。 符号库(symbol_libray): 显示电路时,用于标识器件,单元的符号库。