FM31256的基本结构及原理

带RTC的FC总线铁电存储器FM31256

带 R C的 1 T 2 C息线铁电存储矗 F 3 6 5 M 1 2

■ 中南 大 学 陈 淼 凌 玉 华 廖 力 清

关键词

I 总 线 铁 电体技 术 R MS 4 0 C TC P 3F

F 1 5 是 由 R mt n公 司 推 出的 新 一 代 多 功 能 系 M3 2 6 a r o 统 监 控 和 非 易 失 性 铁 电 存 储 芯 片 。 与 其 他 非 易 失 性 存 储 器 比较 , 具 有 如 下 优 点 :读/ 速 度 快 , 有 写 等 待 时 它 写 没 间 ; 耗 低 , 态 电 流小 于 1mA, 人 电 流 小 于 1 0mA; 功 静 写 5

由 用户 自由选 择 。

A l AO 、 S CL

铁 电存 储 器 ( R F AM) 核 心 技 术 是 铁 电 晶 体 材 料 。 的 这一 特 殊 材 料 使 铁 电 存 储 器 同 时 拥 有 随 机 存 取 存 储 器 ( A 和 非 易 失 性 存 储 的 特 性 。本 文 介 绍 了 F 1 5 R M) M3 2 6 的 主要 功 能 , 具 体 给 出 了基 于 嵌 入 式 C语 言 编 写 的 存 并

用 先 进 的 0 3 m 制 造 工 艺 , 些 功 能 通 过 一 个 通 用 接 口 .5 这

VDD VBAK

事件计数器

开关 电源 f

图 1 F M315 2 6原 理 图

2 F 15 M3 2 6功 能及 使 用 方 法

在 F 15 M32 6中 , 2 个 特 殊 功 能 寄 存 器 ( F ) O 有 5 S R OH

功能。

p e msto. ( 稿 ) ar e ec c投 专用 p@ n. r n n

FM31256在C8051F单片机系统中的应用

FM31256在C8051F单片机系统中的应用李娜1,孙百生2,方卫民11北京邮电大学自动化学院,北京(100876)2北京信息科技大学,北京(100085)E-mail:lina0474@摘要:本文介绍了一种具有I2C接口的高速低功耗、集多功能为一体的铁电存储器FM31256,对器件的基本结构、工作原理和使用方法作了详细的描述,并以C8051F020单片机系统为例介绍了FM31256在C8051F系列单片机中的应用,并给出了部分程序。

关键词:FM31256,C8051F单片机,铁电存储器0.引言FRAM 由于具有非易失性、读写速度快、读写功耗极低等诸多优点使其得到了广泛的应用。

目前FRAM 在中国已经涉足许多应用领域,例如计量领域的称重仪,计量器,汽车电子领域的ABS、车身电子、以及电力能源的监测、通讯领域嵌入式系统、PLC、安全系统报警监控、工业控制,、通讯,金融电子等。

FM31256 是Ramtron 公司推出的一款存储容量为32k×8bits 的FRAM。

它集非易失存储器、实时时钟、低电压复位、掉电检测、看门狗、非易失事件计数器等多种功能于一体, 克服了传统方案采用分立器件造成的电路复杂、成本高等缺点。

可以方便的应用于以单片机、ARM、DSP、FPGA 为核心的电子产品中,尤其适合于电池供电的产品。

1. FM31256FM31256 采用工业标准的I2C 总线,14 脚SOIC 封装,其内部具有256Kb 的串行FRAM,可按字节读写, 读写方式与SRAM 一样,速度快,CLK 的速度达到1MHZ,没有写等待,读写次数无限次,功耗低,静态电流低于1uA,读写电流低于150uA。

片内的实时时钟以BCD 格式提供时间和日期信息,它能通过外部电池或电容供电,供电时钟使用一个32.768 kHz 晶振,可以使用软件校准模式来提供时间记录器的精确性[1] 。

片内包括一个低电压复位模块,当电源电压下降到低于可编程的门限电压时,PRST 被激活并一直保持有效状态,直到VDD 上升到高于正常点后的100ms 。

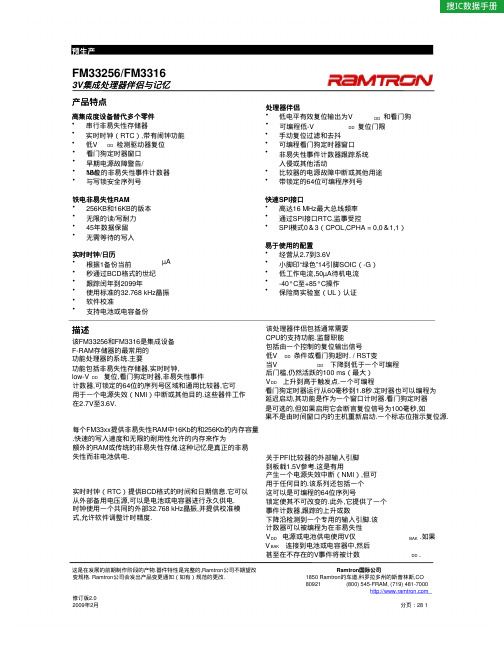

FM33256_FM3316_中文数据手册

串行时钟:所有的I / O活动同步串行时钟.输入锁存的上升沿和输出发生在下降沿.由于该设备是静态 的,时钟频率可以是0和16 MHz之间的任何值,并且可以在任何时间被中断.

串行输入:所有数据输入到该引脚上的设备.该引脚的上升沿采样 SCK的边缘,而在其他时间被忽略.它应该总是被驱动为有效逻辑电平 满足我 DD 规格. SI引脚可以连接到SO为一个单一的数据引脚 接口.

VDD

13

ACS

12

SCK

11

SI

10

PFO

9

RST

8

PFI

FM33256/FM3316 SPI伴侣W / FRAM

引脚名称

/CS SCK

SI SO

PFI PFO CNT

ACS /RST

X1, X2 VDD VBAK

VSS

功能

片选 串行时钟

串行数据输入 串行数据输出

电源故障输入 电源故障输出(NMI) 计数器输入 报警/校准/ SqWave 复位输入/输出 晶体连接 电源电压 电池后备电源

• 无需等待的写入

实时时钟/日历

• 根据1备份当前

µA

• 秒通过BCD格式的世纪

• 跟踪闰年到2099年

• 使用标准的32.768 kHz晶振

• 软件校准

• 支持电池或电容备份

快速SPI接口

• 高达16 MHz最大总线频率

• •

通过SPI接口RTC,监事受控 SPI模式0&3(CPOL,CPHA = 0,0&1,1)

实时时钟(RTC)提供BCD格式的时间和日期信息.它可以 从外部备用电压源,可以是电池或电容器进行永久供电. 时钟使用一个共同的外部32.768 kHz晶振,并提供校准模 式,允许软件调整计时精度.

FM3104 fm3116 fm3164 fm31256 铁电

特性高集成度用于替换多个器件 l 串行非易失性存储器 l 实时时钟 l 低电压复位 l 看门狗记数器l 早期电压失效告警/NMI l 双16位事件记数器 l 串行数字标识 铁电非易失性RAMl 4Kb 、16Kb 、64Kb 、256 Kb 版本 l 无限制的读写次数 l 10年掉电数据保存期 l 无延时写操作 实时时钟/日历l 备用电流低至1UAl 秒至年采用BCD 格式编码 l 自动闰年调整l 使用标准的32.768KHZ 晶振(6PF ) l 时钟软件校准l 支持电池及电容后备处理器辅助功能l 电源及看门狗低有效复位输出 l 可编程低电压复位门限 l 手动复位l 可编程看门狗记数器l 电池后备的双事件记数器用于记录系统干扰或其它事件l 比较器用于电源失效中断或者其它用途 l 带锁定的64位串行数字标识 快速的二线制串行接口l 最高达1M 总线时钟频繁l 支持以前的100K&400K 总线速度 l 器件选择管脚用于最多四只芯片寻址l RTC 、监测控制功能统一通过进行二线制接口操作方便使用的构造l 操作电源范围2.7V-5.5V l 小封装14引脚SOICl 低操作电流,150UA 的静态工作电流 l -40°C 至 +85°C 温度操作范围描述FM31系列产品是一族包含基于处理器系统的通用功能需求的集成器件,主要功能包含各种容量大小的铁电非易性存储器、实时时钟、低电压复位、看门狗记数器、非易失的事件记数器、可锁定的串行数字标识,和一个通用的比较器,用于电源失效中断输出或其它用途,所有器件的操作电压范围为2.7V-5.5V .。

FM31系列器件包含4Kb 、16Kb 、64Kb 、256 Kb 版本,快速的写速度及无限制读写次数,使得此存储器可以像一个外部RAM 或传统的非易失性存储器那样使用,相对于电池后备方式,它是真正的非易失性存储器。

实时时钟以BCD 码的形式提供时间及日期信息,它可以永久地由后备电源供电,后备电源可以是电容,也可以是电池。

FM31256的基本结构及原理

FM31256的基本结构及原理摘要FM31256是一种基于I2C总线、采用铁电体技术的多功能存储芯片。

除了非易失存储器外,该器件还具有实时时钟、低电压复位、看门狗计数器、非易失性事件计数器、可锁定的串行数字标识等多种功能。

文章主要介绍了FM31256的基本功能、原理,并结合实例给出了其在电磁铸轧电源控制装置中的具体应用方法。

关键词I2C总线铁电体技术 RTC MSP430FFM31256是由Ramtron公司推出的新一代多功能系统监控和非易失性铁电存储芯片。

与其他非易失性存储器比较,它具有如下优点:读/写速度快,没有写等待时间;功耗低,静态电流小于1 mA,写入电流小于150 mA;擦写使用寿命长,芯片的擦写次数为100亿次,比一般的EEPROM存储器高10万倍,即使每秒读/写30次,也能用10年;读/写的无限性,芯片擦写次数超过100亿次后,还能和SRAM一样读/写。

铁电存储器(FRAM)的核心技术是铁电晶体材料。

这一特殊材料使铁电存储器同时拥有随机存取存储器(RAM)和非易失性存储的特性。

本文介绍了FM31256的主要功能,并具体给出了基于嵌入式C语言编写的存储器读/写程序。

1 FM31256的基本结构及原理FM31256由256 KB存储器和处理器配套电路(processor companion)两部分组成。

与一般的采用备份电池保存数据不同,FM31256是真正意义上的非易失(truly nonvolatile)存储器,并且用户可以选择对不同的存储区域以软件方式进行写保护。

FM31256 器件将非易失FRAM与实时时钟(RTC)、处理器监控器、非易失性事件计数器、可编程可锁定的64位ID号和通用比较器相结合。

其中,通用比较器可提前在电源故障中断(NMI)时发挥作用或实现其他用途。

采用先进的0.35 μm制造工艺,这些功能通过一个通用接口嵌入到14个引脚的SOIC封装中,从而取代系统板上的多个元件。

超外差收音机原理详细讲解

超外差收音机方框图超外差收音机电路组成方框图如图Z1002所示。

它主要由输入回路、变频级、中放级、检波级、低放级〔前置或推动级〕和功放级与电源等局部组成。

超外差收音机的主要工作特点是:采用了"变频"措施。

输入回路从天线接收到的信号中选出某电台的信号后,送入变频级,将高频已调制信号的载频降低成一固定的中频〔对各电台信号均一样〕,然后经中频放大、检波、低放等一系列处理,最后推动扬声器发出声音。

这一"变频"措施,是超外差收音机性能得以改善的关键,也是分析超外差收音机"重点"。

超外差收音机性能指标收音机质量的上下是用其性能指标来衡量的。

国家标准中规定的指标很多,我们就其重要的几项作一介绍。

1.灵敏度收音机正常工作〔即输出功率和输出信噪比达到额定值〕时,天线上感应的最小信号(场强或电势)称为灵敏度。

它反映收音机接收微弱信号的能力。

使用磁性天线接收信号时,用电场强度来表示,其单位是mV/m,一般中波段收音机的灵敏度应不劣于2mV/m;使用外接天线或拉杆天线时,灵敏度用电势表示,单位是μV。

2.选择性收音机抑制邻近电台信号干扰、选择有用信号的能力称为选择性。

它反映收音机选择电台的能力。

调幅广播电台的中心频率是按9kHz间隔来分布的,故收音机的选择性通常用输入信号失谐±9kHz时,灵敏度的衰减程度来衡量,一般要求收音机的选择性大于20dB。

3.失真度收音机输出波形与输入波形相比失真的程度称为失真度。

收音机中对音质有影响的主要是频率失真和非线性失真。

4.波段覆盖围收音机所能接收的载波频率围。

调幅收音机的中波段频率围为535~1605kHz,而短波围那么为1.6─26MHz,调频收音机的覆盖围为88─108MHz。

LC串联谐振回路LC谐振回路LC谐振回路广泛地用于超外差收音机的选频电路之中,如输入回路、变频电路、中频电路等。

故在分析超外差收音机的工作原理之前,我们先复习一下LC 谐振回路的性能与特点。

调频(FM)无线 对讲机 原理,制作与调试

说明

首页 | 热门导航 | 行业导航 | 学科导航 | 地方导航

当前位置: 首页 > 调频(FM)无线 对讲机 原理,制... 数字中国全站搜索:

0—25kHz范围之间,音频信号的频谱范围则在100—3000Hz之间,我们可以采用一个特殊的滤波器选出这一噪声信号,经检波变成直流分量,再通过一个电子开关电路就可以控制一个电路工作,达到静噪目的,这样在接收机没有收到信号时,喇叭将寂静一片,以消除讨厌的噪声,一旦收到对讲机发来的信号,又能自动打开放大电路进行联络。同时,设置静噪电路还可以达到省电目的。

N3和CRY1,L5等元件组成本机振荡器,L5和相应的回路电容谐振于10.243MHz的三次谐波上,即10.24333x3=30.730MHz,它比发射频率30.275MHz(10.0917的三倍频,即10.0917MHzx3=30.275MHz)高出一个中频455kHz(即30.730—30.275=0.455MHz),本振信号也送到Icl的第1脚,在Icl内部进行混频。

除了提到的这些元件,其他元件选用普通的元件即可,业余条件下完全可以,据笔者经验,那些非主要元件对收信灵敏度影响十分轻微。

因为ICl是专用的窄带调频接收芯片,性能一般都得到保证。质量最优的要算MOTOROLA公司的产品,其次MALAYSIA生产的也不错。值得一提的是笔者拿到了数片Made

in

China的MC3361芯片,通过采用德国的信号发生器(频率在50MHz量程精确到10Hz,。输出分辨率可达0.01uv)等仪器对比实验,国产的产品灵敏度与MOTOROLA公司的产品基本无差别。所以ICl的性能参数完全不必多虑。

7.载频输出功率:2w

FM收音机原理与原理图

AM/FM收音机的安装与调试ξ1概述一、实习目的:1、学习收音机的调试与装配。

2、提高读整机电路图及电路板图的能力。

3、掌握收音机生产工艺流程,提高焊接工艺水平。

二、实习内容:1、收音机电路原理分析。

2、掌握印制电路板的组装及焊接工艺。

3、进行AM、FM中频及统调覆盖的调试及整机测试。

4、故障判断及排除。

三、实习基本要求:1、会检测元器件并判别其质量。

2、独立完成各测试点的测量与整机安装。

3、会排除在调试与装配过程中可能出现的问题与故障。

4、所制作的产品电器性能指标应能满足三级机水平(国标),具体如下:接收频率范围:AM 525~1605KHZ FM72~108MHZ接收灵敏度:AM 达国家C类标准FM优于μV级输出功率:大于100mW供电电源:DC 3V立体声耳机输出阻抗:32Ωξ2收音机的基本工作原理1、收音机的电路结构种类有很多,早期的多为分立元件电路,目前基本上都采用了大规模集成电路为核心的电路。

集成电路收音机的特点是结构比较简单,性能指标优越,体积小等优点。

AM/FM型的收音机电路可用如图1所示的方框图来表示。

收音机通过调谐回路选出所需的电台,送到变频器与本振电路送出的本振信号进行混频,产生中频输出(我国规定的AM中频为465KHZ,FM中频为10.7MHZ),中频信号将检波器检波后输出调制信号,调制信号经低放、功放放大电压和功率,推动喇叭发出声音。

图1 AM/FM型收音机电路方框图2、本实训中的收音机是一种50型的AM/FM二波段的收音机,收音机电路主要由索尼公司生产的专为调频、调幅收音机设计的大规模集成电路CXA1191M/CXC1191P组成。

由于集成电路内部无法制作电感、大电容和大电阻,故外围元件多以电感、电容和电阻为主,组成各种控制、供电、滤波等电路。

50型收音机电路图如图2所示。

图2 50型收音机电路图CXA1191M/CXC1191P的内部方框图如图3所示。

图3 CXA1191M/CXC1191P的内部方框图下面介绍收音机电路图的功能块电路的作用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FM31256的基本结构及原理

摘要FM31256是一种基于I2C总线、采用铁电体技术的多功能存储芯片。

除了非易失存储器外,该器件还具有实时时钟、低电压复位、看门狗计数器、非易失性事件计数器、可锁定的串行数字标识等多种功能。

文章主要介绍了FM31256的基本功能、原理,并结合实例给出了其在电磁铸轧电源控制装置中的具体应用方法。

关键词I2C总线铁电体技术 RTC MSP430F

FM31256是由Ramtron公司推出的新一代多功能系统监控和非易失性铁电存储芯片。

与其他非易失性存储器比较,它具有如下优点:读/写速度快,没有写等待时间;功耗低,静态电流小于1 mA,写入电流小于150 mA;擦写使用寿命长,芯片的擦写次数为100亿次,比一般的EEPROM存储器高10万倍,即使每秒读/写30次,也能用10年;读/写的无限性,芯片擦写次数超过100亿次后,还能和SRAM一样读/写。

铁电存储器(FRAM)的核心技术是铁电晶体材料。

这一特殊材料使铁电存储器同时拥有随机存取存储器(RAM)和非易失性存储的特性。

本文介绍了FM31256的主要功能,并具体给出了基于嵌入式C语言编写的存储器读/写程序。

1 FM31256的基本结构及原理

FM31256由256 KB存储器和处理器配套电路(processor companion)两部分组成。

与一般的采用备份电池保存数据不同,FM31256是真正意义上的非易失(truly nonvolatile)存储器,并且用户可以选择对不同的存储区域以软件方式进行写保护。

FM31256 器件将非易失FRAM与实时时钟(RTC)、处理器监控器、非易失性事件计数器、可编程可锁定的64位ID号和通用比较器相结合。

其中,通用比较器可提前在电源故障中断(NMI)时发挥作用或实现其他用途。

采用先进的0.35 μm制造工艺,这些功能通过一个通用接口嵌入到14个引脚的SOIC封装中,从而取代系统板上的多个元件。

存储器的读/写以及其他控制功能都通过工业标准的I2C总线来实现。

图1为FM31256的原理图。

其中,SDA和SCL引脚用于与CPU进行数据交换和命令写入,数据输出部分均具有施密特触发器,以提高抗干扰性能;同时,SDA 作为二线接口中的双向信号线,集电极开路输出,可与二线总线上其他器件进行“线或”。

A1~A0为器件地址选择信号,即总线上可同时使用4个同类器件。

正常模式下,PFI引脚分别为比较器的输入(不可悬空),CAL/PFO引脚输出PFI 引脚的输入信号与1.2 V参考电压之间的比较结果;校准模式下,CAL/PFO引脚将输出512 Hz的方波用于时钟校准。

CNT2~CNT1是通过备份电池支持的事件计数器的两路输入端,通过边沿触发启动计数器,触发沿由用户自由选择。

X1和X2晶振引脚均为高阻引脚,两引脚之间的距离须小于5 mm;即使信号位于板内层,也不允许信号线靠近X1和X2引脚。

在晶振引脚周围使用接地保护环,内部或板反面使用接地保护敷铜。

3.2 存储区访问程序设计

对FM31256存储器访问操作过程中,微处理器处于主机地位,器件始终处于从机地位。

根据上述对FM31256的分析,可以把所有的通信过程归纳为3种类型:①单脉冲,如Start、Stop、Ack、Nack;②字节发送,如从机地址、目标地址和数据传送;③字节接收,如读操作中的数据传送。

因此只要把这些操作以子程序的形式编写好,所有的通信操作就可通过调用这些子程序来完成。

这里以MSP430F149微处理器的嵌入式C语言编写。

设微处理器端口P6.6为数据线(SDA);P5.4为时钟线(SCL)。

限于篇幅,本文不作详细介绍,只给出模拟I2C总线及字节写入、读出的部分C语言程序:

#defineRTC_SDABIT6

#defineRTC_SCLBIT4

void FM31256_Start(void) {/*FM31256启动程序*/

P6OUT |=RTC_SDA;// SDA=1

P5OUT |=RTC_SCL;// SCL=1

delay(IIC_DELAY);

P6OUT &=~ RTC_SDA;// SDA=0

delay(IIC_DELAY);

P5OUT &=~ RTC_SCL;// SCL=0}

void FM31256_Stop( void ) {/*FM31256停止程序*/

P6OUT &=~ RTC_SDA;// SDA=0

delay(IIC_DELAY);

P5OUT |=RTC_SCL;// SCL=1

delay(IIC_DELAY);

P6OUT |=RTC_SDA;// SDA=1

delay(IIC_DELAY);}

void FM31256_Send_Ack( void ) {/*FM31256应答程序*/

P5OUT &=~ RTC_SCL;// SCL=0

P6OUT &=~ RTC_SDA;// SDA=0

P5OUT |=RTC_SCL;// SCL=1

delay(IIC_DELAY);

P5OUT &=~ RTC_SCL;// SCL=0}

void FM31256_Send_noAck( void ) {/*FM31256不应答程序*/

P5OUT |=RTC_SCL;// SCL=1

delay(IIC_DELAY);

P5OUT &=~ RTC_SCL;// SCL=0}

说明:SCL线是高电平时,SDA线从高电平向低电平切换,表示起始条件;当SCL是高电平时,SDA线由低电平向高电平切换,表示停止条件。

相关的确认时钟脉冲由主机产生,在确认的时钟脉冲器件发送方释放SDA(高电平),在此期间接收方须将SDA拉低。

void FM31256_transfByte_to_IIC( unsigned char tran_byte ) {/* CPU 字节发送程序*/

unsigned char i , current_bit =0x80;

P5OUT &=~ RTC_SCL;

delay(IIC_DELAY);

for( i=0; i <=7; i++ ) {

if ( tran_byte & current_bit )

P6OUT |= RTC_SDA;

else

P6OUT &=~ RTC_SDA;

current_bit >>=1;

delay(IIC_DELAY);

P5OUT |=RTC_SCL;//SCL=1

delay(IIC_DELAY);

P5OUT &=~ RTC_SCL;//SCL=0

delay(IIC_DELAY);

}

}

unsigned char FM31256_receByte_from_IIC( void ){/*CPU字节接收程序*/

unsigned char mvalue, i, rece_data =0;

P6DIR &=~ RTC_SDA;//设置为输入方向

P5OUT &=~ RTC_SCL; //SCL=0

delay(IIC_DELAY);

for(i=0;i

rece_data = rece_data<<1;

P5OUT |=RTC_SCL;//SCL=1

delay(IIC_DELAY);

mvalue = P6IN & RTC_SDA;//当前位的值

if( mvalue )//接收位为高

rece_data = rece_data | 0x01;

else//接收位为低

rece_data = rece_data & 0xFE;

P5OUT &=~ RTC_SCL;//SCL=0

delay(IIC_DELAY);

}

P6DIR |=RTC_SDA;//P6.6输出

return(rece_data);//返回收到的字节。