第8章 有限状态机设计(1)

第八次课-8章状态机精选全文

z<=0;

三、基于状态机的设计要点

1.起始状态的选择

起始状态是指电路复位后所处的状态,选择一 个合理的起始状态将使整个系统简洁高效。有的 EDA软件会自动为基于状态机的设计选择一个最佳 的起始状态。

2.状态转换的描述

一般使用case语句来描述状态之间的转换, 用case语句表述比用if-else语句更清晰明了。

有限状态机类型 有限状态机的Verilog描述 有限状态机的设计要点

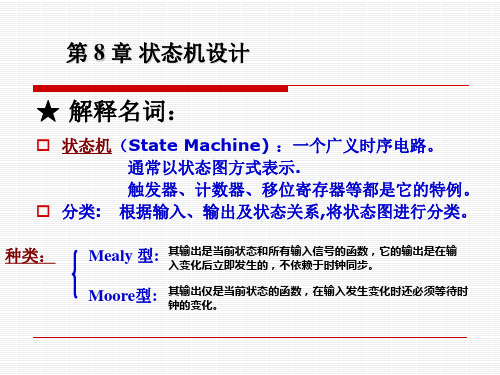

一、两种有限状态机

二、有限状态机的Verilog描述

描述对象:

当前状态、下一状态、输出逻辑

描述方式: 单过程、双过程、三过程

单过程描述方式: 放在一个过程中描述,相当于采用时

钟信号同步,克服输出产生毛刺。但输出 逻辑相对于双过程,要延迟一个时钟周期。

end end

s3: begin if(x==0)

begin state<=s0; z<=0;

end else begin

state<=s4; z<=1; end end

s4: begin if(x==0)

begin state<=s0; end else begin state<=s4; z<=1; end end default:

双过程描述方式: 一个过程 由时钟信号触发的时序过程

(当时钟发生跳变时,状态机状态发生变 化。一般用case语句检查状态机的当前状态; 另一过程是组合过程,对于摩尔型,输出 只与当前状态有关,因此只需用case语句即 可,对米里型,因与当前状态和输入都有 关,因此可用case 语句和 if组合进行描述。

Verilog 有限状态机设计(课堂PPT)

begin

case( state )

state0:

out = 3'b001;

state1:

out = 3'b010;

state2:

out = 3'b100;

state3:

out = 3'b111;

default:

out = 3'b001;

endcase

end

endmodule

11

8.2 有限状态机的Verilog描述

begin if(clr) qout<=0;

//异步复位

else case(qout)

3'b000: qout<=3'b001;

3'b001: qout<=3'b010;

3'b010: qout<=3'b011;

3'b011: qout<=3'b100;

3'b100: qout<=3'b000;

default: qout<=3'b000; /*default语句*/

state2 = 2’b11, state3 = 2’b10; // 格雷码

always @( posedge clk or posedge clr ) begin

if( clr ) state <= state0; // 定义初态 state <= next_state; end

8

always @( state or start or step2 or step3 ) // 状态转换

EDA技术与应用

第八章 有限状态机设计

1

有限状态机设计

实验七有限状态机设计一、实验目的1、掌握利用有限状态机实现一般时序逻辑分析的方法;2、掌握用VHDL或Verilog编写可综合的有限状态机的标准模板;3、掌握用VHDL或Verilog编写序列检测器以及其他复杂逻辑电路的设计;二、实验内容1、用MOORE型状态机设计一个具有双向步进电动机控制实验:该控制电路有三个输入信号:clk时钟信号,clr复位信号,dir方向控制信号。

输出信号为phase[3..0]用来控制步进电机的动作。

当dir=1时要求phase[3..0]按照“0001”,“0010”,“0100”,“1000”的顺序变化;当dir=0时要求phase[3..0]按照“0001”,“1000”,“0100”,“0010”的顺序变化。

2、设计一个简单的状态机,功能是检测一个5位的二进制序列“10010”。

3、设计一个串行数据检测器,要求是:连续4个或4个以上为1时输出为1,其他输入情况为0。

(选做)4、根据状态图,写出对应于结构图b,分别由主控组合进程和主控时序进程组成的VERILOG 有限状态机描述。

(选做)三、实验步骤实验一:1、建立工程2、创建Verilog HDL文件3、输入程序代码并保存module moore1(clk,clr,dir,phase);input clk,clr,dir;output[3:0] phase;reg[3:0] phase;reg[1:0] state;parameter s0='b00,s1='b01,s2='b10,s3='b11;always@(posedge clk)beginif(clr)beginphase<='b0000;state<=s0;endelsebegincase(state)s0:if(dir) beginphase<='b0010;state<=s1;endelsebeginphase<='b1000;state<=s3;ends1:if(dir) beginphase<='b0100;state<=s2;endelse beginphase<='b0001;state<=s0;ends2:if(dir) beginphase<='b1000;state<=s3;endelse beginphase<='b0010;state<=s1;ends3:if(dir) beginphase<='b0001;state<=s0;endelse beginphase<='b0100;state<=s2;endendcaseendendendmodule4、进行综合编译5、新建波形文件6、导入引脚,设置信号源并保存7、功能仿真,结果分析由仿真波形图可以看出当dir=1时,phase[3..0]按照0001,0010,0100,1000的顺序变化,当dir=0时phase[3..0]按照0001,1000,0100,0010的顺序变化。

天津工业大学第08章_状态机设计

能克服纯硬件数字系统顺序方式控制不灵活的缺点 可定义符号化枚举类型的状态 易构成性能良好的同步时序逻辑模块 VHDL表述丰富多样、程序层次分明,易读易懂 巨大的优势在于高速运算和控制方面 高可靠性

8.1.2 数据类型定义语句

8.1 一般有限状态机设计

1) TYPE语句用法: TYPE 数据类型名 IS 数据类型定义 OF 基本数据类型 ;

②自定义新的数据类型:枚举类型、整数类型、数组类型、记录类型、 时间类型、实数类型等多种。

8.1 一般有限状态机设计

3)子类型SUBTYPE定义格式

● 子类型SUBTYPE:是由TYPE所定义原数据类型的一个子集,满足原数据类型 所有的约束条件。

● 格式: SUBTYPE 子类型名 IS 基本数据类型 RANGE 约束范围; 例: SUBTYPE digits IS INTEGER RANGE 0 to 9 ;

--EOC=1表明转换结束

ELSE next_state <= st2; END IF ;

--转换未结束,继续等待

WHEN st3=> ALE<='0';START<='0';LOCK<='0';OE<='1';

next_state <= st4;

--开启OE,输出转换好的数据

WHEN st4=> ALE<='0';START<='0';LOCK<='1';OE<='1'; next_state <= st0;

【例8-2】采样状态机程序---续

EDA复习要点

第1章 EDA技术概述1. EDA:EDA(Electronic Design Automation)电子设计自动化,EDA技术依赖于强大的计算机,在EDA工具软件平台上,对以HDL(Hardware Description Language--硬件描述语言)为系统逻辑描述手段完成的设计文件,自动完成逻辑化简、逻辑分割、逻辑综合、结构综合(布局布线),以及逻辑优化和仿真测试等项功能,直至实现既定性能的电子线路系统功能。

2. EDA的设计输入有:图形输入方式:原理图输入,状态图输入;HDL文本输入:VHDL,Verilog3. 常用缩写FPGA(Field Programable Gate Araay)CPLD(Complex Programmable Logic Device)ASIC(Application Specific Interated Circuit)SOC(System on a Chip)SOPC(System-on-a-Programmable-Chip)HDL(Hardware Description Language)IP(Intellectual Property)CAD(Computer Aided Design)CAM(Computer Aided Manufacturing)CAT(Computer Aided Test)CAE(Computer Aided Engineering)CAA(Computer Aided Analysis)4.综合(Synthesis):将用行为和功能层次表达的系统转换成低层次的便于具体实现的模块组合装配过程。

整个综合过程就是将设计者在EDA平台上编辑输入的HDL文本、原理图或状态图形描述,依据给定的硬件结构组件和约束控制条件进行编译、优化、转换和综合,最终获得门级电路甚至更底层的电路描述网表文件。

5.适配:适配器也称结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件,如JEDEC、Jam格式的文件。

eda技术实用教程-veriloghdl答案

eda技术实用教程-veriloghdl答案【篇一:eda技术与vhdl程序开发基础教程课后答案】eda的英文全称是electronic design automation2.eda系统设计自动化eda阶段三个发展阶段3. eda技术的应用可概括为4.目前比较流行的主流厂家的eda软件有、5.常用的设计输入方式有原理图输入、文本输入、状态机输入6.常用的硬件描述语言有7.逻辑综合后生成的网表文件为 edif8.布局布线主要完成9.10.常用的第三方eda工具软件有synplify/synplify pro、leonardo spectrum1.8.2选择1.eda技术发展历程的正确描述为(a)a cad-cae-edab eda-cad-caec eda-cae-cadd cae-cad-eda2.altera的第四代eda集成开发环境为(c)a modelsimb mux+plus iic quartus iid ise3.下列eda工具中,支持状态图输入方式的是(b)a quartus iib isec ispdesignexpertd syplify pro4.下列几种仿真中考虑了物理模型参数的仿真是(a)a 时序仿真b 功能仿真c 行为仿真d 逻辑仿真5.下列描述eda工程设计流程正确的是(c)a输入-综合-布线-下载-仿真b布线-仿真-下载-输入-综合c输入-综合-布线-仿真-下载d输入-仿真-综合-布线-下载6.下列编程语言中不属于硬件描述语言的是(d)a vhdlb verilogc abeld php1.8.3问答1.结合本章学习的知识,简述什么是eda技术?谈谈自己对eda技术的认识?答:eda(electronic design automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

2.简要介绍eda技术的发展历程?答:现代eda技术是20世纪90年代初从计算机辅助设计、辅助制造和辅助测试等工程概念发展而来的。

EDA技术6-Verilog状态机

i

o

(c)状态输出型 图 1 有限状态机的分类

厦门理工学院通信系 刘虹

6

说明部分:

厦门理工学院通信系 刘虹

7

8.2 Moore型有限状态机的设计

8.2.1 ADC采样控制设计及多过程结构型状态机

厦门理工学院通信系 刘虹

8

厦门理工学院通信系 刘虹

9

厦门理工学院通信系 刘虹

10

厦门理工学院通信系 刘虹

11

厦门理工学院通信系 刘虹

12

厦门理工学院通信系 刘虹

13

厦门理工学院通信系 刘虹

14

8.3 Mealy型有限状态机的设计

8.3.1 序列检测器之状态机设计

厦门理工学院通信系 刘虹

15

厦门理工学院通信系 刘虹

16

程序8-5描述的是一个 Mealy型状态机,实现 的功能为:序列检测器。 检测的输入序列为 DIN1=11110,输出信号 由DIN2控制,并结合 当前状态得到相应的输 出信号Q,具体输出编 码见右表。

当前状态 st0 st1 st2 st3 st4

DIN2 1 0 1 0 1

Q 5’H10 5’H0A 5’H14 5’H17 5’H15

0

1 0 1 0

5’H13

5’H09 5’H1B 5’H1D 5’H0D

厦门理工学院通信系 刘虹

17

Hale Waihona Puke 厦门理工学院通信系 刘虹 3

i

有限状态机的分类 状

组 合 逻 辑 态 寄 存 器

组 合 逻 辑

o

(1)Moore型状态机:输出仅是状态向量的函数, (a)Mealy 型 结构如图(b)所示。

eda技术实用教程-veriloghdl答案

eda技术实用教程-veriloghdl答案【篇一:eda技术与vhdl程序开发基础教程课后答案】eda的英文全称是electronic design automation2.eda系统设计自动化eda阶段三个发展阶段3. eda技术的应用可概括为4.目前比较流行的主流厂家的eda软件有、5.常用的设计输入方式有原理图输入、文本输入、状态机输入6.常用的硬件描述语言有7.逻辑综合后生成的网表文件为 edif8.布局布线主要完成9.10.常用的第三方eda工具软件有synplify/synplify pro、leonardo spectrum1.8.2选择1.eda技术发展历程的正确描述为(a)a cad-cae-edab eda-cad-caec eda-cae-cadd cae-cad-eda2.altera的第四代eda集成开发环境为(c)a modelsimb mux+plus iic quartus iid ise3.下列eda工具中,支持状态图输入方式的是(b)a quartus iib isec ispdesignexpertd syplify pro4.下列几种仿真中考虑了物理模型参数的仿真是(a)a 时序仿真b 功能仿真c 行为仿真d 逻辑仿真5.下列描述eda工程设计流程正确的是(c)a输入-综合-布线-下载-仿真b布线-仿真-下载-输入-综合c输入-综合-布线-仿真-下载d输入-仿真-综合-布线-下载6.下列编程语言中不属于硬件描述语言的是(d)a vhdlb verilogc abeld php1.8.3问答1.结合本章学习的知识,简述什么是eda技术?谈谈自己对eda技术的认识?答:eda(electronic design automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

2.简要介绍eda技术的发展历程?答:现代eda技术是20世纪90年代初从计算机辅助设计、辅助制造和辅助测试等工程概念发展而来的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

加 锁

开 锁

通过 / 加锁

通过传感器

锁执行

控 制

投币传感器 加锁执行

器

声光报警

初始状态 加锁 通过 报警

CLK

投币 锁 投币

加 锁

锁

通过

加锁

一、概述

关于状态机 状态机的特点 状态机的基本结构和功能

关于状态机

状态机就是事物存在状态的一种综合描述。 状态机就是事物存在状态的一种综合描述。 一个单向路口的一盏红绿灯:红灯、 例:一个单向路口的一盏红绿灯:红灯、 黄灯、绿灯。 黄灯、绿灯。 状态机就是对这盏红绿灯的3种状态进行 状态机就是对这盏红绿灯的 种状态进行 综合描述, 综合描述,说明任意两个状态之间的转变 条件。 条件。

Chapter 5 有限状态机

计算机与信息学院 毕春跃

2011.10.25

引子: 引子:

有一自动门,它可以被锁上,也可以开锁。当门 有一自动门,它可以被锁上,也可以开锁。 锁上时,某人可以在它的槽中塞进一枚硬币。这样, 锁上时,某人可以在它的槽中塞进一枚硬币。这样, 门就会自动开锁,转变到开锁的状态;人通过后, 门就会自动开锁,转变到开锁的状态;人通过后, 门就会自动锁上。 门就会自动锁上。

分析设计要求,列出全部可能状态: (1) 分析设计要求,列出全部可能状态:

未收到一个有效位( 未收到一个有效位(0) 收到一个有效位( 收到一个有效位(1) 连续收到两个有效位(11) 连续收到两个有效位(11) 连续收到三个有效位(110) 连续收到三个有效位(110) 连续收到四个有效位(1101) 连续收到四个有效位(1101) :S0 :S1 :S2 :S3 :S4

WHY? 为什么使用状态机 ?

有限状态机克服了纯硬件数字系统顺序方式控制不灵 活的缺点。 活的缺点。 状态机的结构模式相对简单。 状态机的结构模式相对简单。 状态机容易构成性能良好的同步时序逻辑模块。 状态机容易构成性能良好的同步时序逻辑模块。 状态机的VHDL表述丰富多样。 表述丰富多样。 状态机的 表述丰富多样 在高速运算和控制方面,状态机更有其巨大的优势。 在高速运算和控制方面,状态机更有其巨大的优势。 就可靠性而言,状态机的优势也是十分明显的。 就可靠性而言,状态机的优势也是十分明显的。

ARCHITECTURE a OF moore IS 定义状态机 TYPE STATE IS (S0,S1,S2,S3,S4); SIGNAL pstate :STATE; BEGIN PROCESS(clk) 状态转移描述 BEGIN IF (clk’EVENT AND clk=‘1’) THEN CASE pstate is WHEN S0=> IF data=‘1’ THEN pstate<=S1; ELSE pstate<=S0; END IF; WHEN S1=> IF data=‘1’ THEN pstate<=S2; ELSE pstate<=S0; END IF; WHEN S2=> IF data=‘0’ THEN pstate<=S3; ELSE pstate<=S2; END IF; WHEN S3=> IF data=‘1’ THEN pstate<=S4; ELSE pstate<=S0; END IF; WHEN S4=> IF data=‘1’ THEN pstate<=S1; ELSE pstate<=S0; END IF; END CASE; END IF; 输出信号描述 END PROCESS; zo<=‘1’ WHEN pstate=s4 ELSE ‘0’; END a;

例:设计一个序列检测器。要求检测器连续收到 设计一个序列检测器。 串行码{1101} {1101}后 输出检测标志1 否则输出0 串行码{1101}后,输出检测标志1,否则输出0。

状态机设计步骤: 状态机设计步骤: 分析设计要求,列出全部可能状态; ① 分析设计要求,列出全部可能状态; 画出状态转移图; ② 画出状态转移图; VHDL语言描述状态机 语言描述状态机。 ③ 用VHDL语言描述状态机。

Moore型有限状态机的结构图 型有限状态机的结构图

输入 X

组组 电电 状 态 寄 存 器 组组 电电

输出 Y

c1k

Mealy型有限状态机的结构图 型有限状态机的结构图

有限状态机的主要功能: 有限状态机的主要功能:

实现一个数字系统设计中的控制部分。 实现一个数字系统设计中的控制部分。

有限状态机中的每一个状态对应于控制单元的一个 控制步; 控制步; 有限状态机中的次态和输出对应于控制单元中与每 一个控制步有关的转移条件。 一个控制步有关的转移条件。

8421循环计数器

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity autocnt is port(clk:in std_logic; q:out std_logic_vector(3 downto 0)); end autocnt; architecture a of autocnt is type state is (s0,s1,s2,s3); signal st:state; signal n:state; begin process(clk) begin if clk'event and clk='1' then st<=n; end if; end process;

process(st,clr) begin if (clr='0') then t1<='0';t2<='0';t3<='0'; else case st is when s0=> t1<='1';t2<='0';t3<='0'; when s1=> t1<='0';t2<='1';t3<='0'; when s2=> t1<='0';t2<='1';t3<='0'; when s3=> t1<='0';t2<='0';t3<='1'; when s4=> t1<='0';t2<='0';t3<='1'; when s5=> t1<='1';t2<='0';t3<='0'; end case; end if; end process; end rtl;

(2) 状态转移图 ) 状态转移图:

(3)用VHDL语言描述状态机 ) 语言描述状态机 定义状态机— 定义状态机 枚举类型 状态转换描述 输出信号描述

Moore型状态机设计方法 型状态机设计方法

(2) 状态转移图 ) 状态转移图:

Data_INi

0

1101

Si/ZOi

S0/0

0 0 1 0 1 1 1

说明部分:主要是设计者使用 语句定义新的数据类型, 说明部分:主要是设计者使用TYPE语句定义新的数据类型,如: 语句定义新的数据类型 TYPE states IS (st0, st1, st2, st3, st4, st5); SIGNAL present_state, next_state: states;

What? What?什么是状态机

有限状态机(简称状态机 相当于一个控制器 有限状态机 简称状态机)相当于一个控制器, 简称状态机 相当于一个控制器, 它将一项功能的完成分解为若干步, 它将一项功能的完成分解为若干步,每一步对应 于二进制的一个状态, 于二进制的一个状态,通过预先设计的顺序在各 状态之间进行转换, 状态之间进行转换,状态转换的过程就是实现逻 辑功能的过程。 辑功能的过程。

Moore型状态机设计方法 型状态机设计方法 More型状态机输出仅和存储电路的状 型状态机输出仅和存储电路的状 态有关,与外部输入无关, 态有关,与外部输入无关,即: 外部输出是内部状态的函数。 外部输出是内部状态的函数。

状态转移图描述方式: 状态转移图描述方式:

Data_INi

Si/ZOi

Moore型状态机设计方法 型状态机设计方法

二、一般有限状态机的组成

说明部分 说明部分中使用TYPE语句定义新的数据类型,此数据类型 语句定义新的数据类型, 说明部分中使用 语句定义新的数据类型 一般为枚举类型 例如: 例如: TYPE state_type IS (start_state,run_state,error_state); ; SIGNAL state:state_type; ; 说明部分一般放在结构体的ARCHITECTURE和BEGIN之 和 说明部分一般放在结构体的 之 间。

一般有限状态机的VHDL组成 一般有限状态机的VHDL组成 VHDL

主控时序逻辑部分:任务是负责状态机运转和在外部时 主控时序逻辑部分: 钟驱动下实现内部状态转换的进程。 钟驱动下实现内部状态转换的进程。时序进程的实质是 一组触发器,因此, 一组触发器,因此,该进程中往往也包括一些清零或置 位的输入控制信号, 信号。 位的输入控制信号,如Reset信号。 信号 主控组合逻辑部分: 主控组合逻辑部分:任务是根据状态机外部输入的状态 控制信号( 控制信号(包括来自外部的和状态机内部的非进程的信 和当前的状态值current_state来确定下一状态 号)和当前的状态值 来确定下一状态 next_state的取值内容,以及对外部或对内部其他进 的取值内容, 的取值内容 程输出控制信号的内容。 程输出控制信号的内容。 辅助逻辑部分: 辅助逻辑部分:辅助逻辑部分主要是用于配合状态机的 主控组合逻辑和主控时序逻辑进行工作, 主控组合逻辑和主控时序逻辑进行工作,以完善和提高 系统的性能。 系统的性能。