STM8时钟树解析

STM8教程-第八章 STM8S207时钟编程及其实例

第八章STM8S207时钟编程及其实例本章介绍STM8S207 的时钟编程。

STM8S207 时钟控制器功能强大而灵活易用,允许程序运行中将主时钟从一个时钟源切换到另一个时钟源,而且同一个时钟源可以任意更改分频系数。

8.1 STM8 时钟控制简介时钟控制器功能强大而且灵活易用。

其目的在于使用户在获得最好性能的同时,亦能保证消耗的功率最低。

用户可独立地管理各个时钟源,并将它们分配到CPU 或各个外设。

主时钟和CPU 时钟均带有预分频器。

具有安全可靠的无故障时钟切换机制,可在程序运行中将主时钟从一个时钟源切换到另一个时钟源。

抗电磁干扰时钟配置寄存器为了避免由电磁干扰造成的对应用程序误写操作或系统挂起,大多数关键的时钟配置寄存器都有一个互补寄存器与之相对应。

系统将会自动检测这些关键寄存器与其互补寄存器之间是否匹配。

如果不匹配,则产生一个EMS 复位,从而使应用程序恢复到正常操作。

详情请参见时钟寄存器描述。

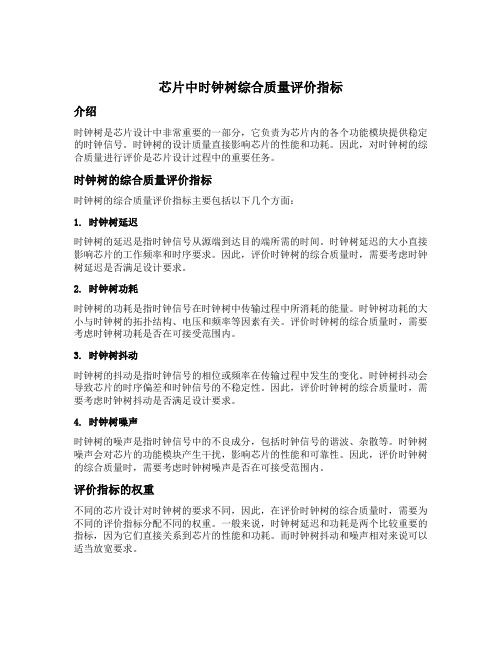

1、主时钟源介绍下面4种时钟源可用做主时钟1、1-24MHz 高速外部晶振(HSE)2、最大24MHz 高速外部时钟信号3、16MHz 高速内部RC 振荡器(HSI)4、128KHz 低速内部RC(LSI)所以总的来说可以分为三种时钟源,HSE、HSI、LSI2、时钟树,如下图所示由上图可以发现,作为f_cpu 的时钟源可以来源于f_hse、f_hsi 经过HSIDIV分频后的时钟、f_lsi 这三个时钟源。

而选择开关在CKM[7:0]中。

由此事实上可以作为f_master 的时钟源频率有:外部HSE 24MHz内部高速HSI 16MHz、2 分频的8MHz、4 分频的4MHz、8 分频的2MHz(复位默认时钟源)内部低速LSI 128KHz上面得到的频率是f_master 的频率,然后f_master 还可以通过CPUDIV 来分频后提供f_cpu 的时钟,CPUDIV 可以为1、2、4、8、16、32、64、128 分频,最终得到是CPU 的时钟频率f_cpu。

STM8学习笔记——时钟和GPIO

STM8学习笔记——时钟和GPIO说起STM8 的时钟,那还真是个杯具,用HSI 没问题,切换到HSE 也没问题,就是切LSI 怎么都不行,然后百思不得其解人,然后上论坛求教,才知道还有个选项字节(OPTION BYTE),数据手册上有这么一段描述:选项字节包括芯片硬件特性的配置和存储器的保护信息,这些字节保存在存储器中一个专用的块内。

除了ROP(读出保护)字节,每个选项字节必须被保存两次,一个是通常的格式(OPTx)和一个用来备份的互补格式(NOPTx)要使用内部低速RC 必须将LSI_EN 置1,就是这个地方让我纠结了半天,然后用IAR 将其置1,方法是:进入调试模式,在上面有个ST-LINK,点击,看到OPTION BYTE,左键点进去,右键单击上面的选项,就可更改了,然后全速运行,就写进去了。

STM8 的时钟分为HSI,HSE,LSI,最常用的是HSI,STMS105S4 内置的是16M 的RC,叫fhsi。

它可以分频输出为fhsidiv=fhsi/hsidiv,如果选择其为主时钟源,那么主时钟fmaster=fhsidiv。

CPU 时钟fcpu=fmaster/cpudiv。

可以通过外设时钟门控寄存器CLK_PCKENR1 和CLK_PCKENR2 选择是否与某个外设连接。

好了上个切换内部时钟的源代码,测试通过void CLK_Init(void){ //切换到内部LSI(!!!需要修改选项字节的LSI_EN 为1)CLK_ICKR|=0x08;//开启内部低速RC 震荡while(CLK_ICKR&0x10==0); //LSI 准备就绪CLK_SWR=0xd2; while(CLK_SWCR&0x08==0); //等待目标时钟源就绪CLK_SWCR|=0x02; //CPU 分频设置CLK_CKDIVR=0;//内部RC 输出。

STM8教程-第八章 STM8S207时钟编程及其实例

第八章STM8S207时钟编程及其实例本章介绍 STM8S207 的时钟编程。

STM8S207 时钟控制器功能强大而灵活易用,允许程序运行中将主时钟从一个时钟源切换到另一个时钟源,而且同一个时钟源可以任意更改分频系数。

STM8 时钟控制简介时钟控制器功能强大而且灵活易用。

其目的在于使用户在获得最好性能的同时,亦能保证消耗的功率最低。

用户可独立地管理各个时钟源,并将它们分配到 CPU 或各个外设。

主时钟和CPU 时钟均带有预分频器。

具有安全可靠的无故障时钟切换机制,可在程序运行中将主时钟从一个时钟源切换到另一个时钟源。

抗电磁干扰时钟配置寄存器为了避免由电磁干扰造成的对应用程序误写操作或系统挂起,大多数关键的时钟配置寄存器都有一个互补寄存器与之相对应。

系统将会自动检测这些关键寄存器与其互补寄存器之间是否匹配。

如果不匹配,则产生一个 EMS 复位,从而使应用程序恢复到正常操作。

详情请参见时钟寄存器描述。

1、主时钟源介绍下面 4种时钟源可用做主时钟1、1-24MHz 高速外部晶振(HSE)2、最大 24MHz 高速外部时钟信号3、16MHz 高速内部 RC 振荡器(HSI)4、128KHz 低速内部 RC(LSI)所以总的来说可以分为三种时钟源,HSE、HSI、LSI2、时钟树,如下图所示由上图可以发现,作为 f_cpu 的时钟源可以来源于 f_hse、f_hsi 经过 HSIDIV分频后的时钟、f_lsi 这三个时钟源。

而选择开关在 CKM[7:0]中。

由此事实上可以作为 f_master 的时钟源频率有:外部 HSE 24MHz内部高速 HSI 16MHz、2 分频的8MHz、4 分频的4MHz、8 分频的2MHz(复位默认时钟源)内部低速 LSI 128KHz上面得到的频率是 f_master 的频率,然后 f_master 还可以通过 CPUDIV 来分频后提供 f_cpu 的时钟,CPUDIV 可以为 1、2、4、8、16、32、64、128 分频,最终得到是 CPU 的时钟频率 f_cpu。

stm8自学l学习笔记

#error directive: "Unsupported Compiler!" STM8编译错误解决方法STM8的库使用很方便,不过初学者下载ST官方的库可能会遇到下面的问题。

原因是因为STM8S的官方库文件发布时,IAR EWSTM8还没有出来,所以在官里面IAR未能被支持,最好是采用IAR自带的头文件,如下图所示:IAR自带的头文件目录,请以你自己的安装目录下查时钟控制STM8的钟控制器功能强大而且灵活易。

现以STM8L101xx单片机的时钟树为例,时钟树如下图所示:HSI 高速接口时钟源LSI 低速接口时钟源从时钟树来看,fCPU 的时钟来源是fMASTER 时钟;fMASTER的时钟源有三个可以选择:fHSI。

fHSI来自于内部的时钟;fHSIDIV来自于内部16MHz RC的时钟源;fLSI来自于内部38KHz RC时钟源。

TIMER2TIM时基单元,如下图所示:计数器使用内部时钟(fMA STER) ,由CK_PSC提供,并经过预分频器分频产生计数器时钟CK_CNT。

计数器时钟频率的计算公式:fCK_CNT = fCK_PSC/2(PSCR[2:0])中断向量表串口uart 学习STM8L101f3p6 有一个串口如图本历程基于库操作不讨论具体寄存器操作有兴趣的同学可以自行参考编程手册下面看一下手册的了解一下特点本人英语是个小白只可意会不可言传了内部结构了由于是基于库函数的所以不做寄存器的分析了库函数的好处就是可以在不了解单片机寄存器的前提下可以快速开发应用下面举个例子波特率 9600 8位字长停止位一位无校验串口模式为收发模式查询发送中断接收在初始化串口之前应该先初始化串口对应的IO口由手册可知串口对应的IO为PC2(USART_RX)和PC3(USART_TX)。

首先宏定义下IO 方便理解和配置#define TXD_GPIO_PORT GPIOC#define RXD_GPIO_PORT GPIOC#define TXD_GPIO_PINS GPIO_Pin_3#define RXD_GPIO_PINS GPIO_Pin_2初始化IOTxD 配置成输出上拉高速模式RxD 配置成输入上拉无中断模式GPIO_Init(TXD_GPIO_PORT, TXD_GPIO_PINS, GPIO_Mode_Out_PP_High_Fast);GPIO_Init(RXD_GPIO_PORT, RXD_GPIO_PINS, GPIO_Mode_In_PU_No_IT);接下来打开串口模块时钟(之前就是忘配置这个功能所以一直不好使)CLK_PeripheralClockConfig(CLK_Peripheral_USART, ENABLE);配置串口详细的功能USART_Init((u32)9600, USART_WordLength_8D, USART_StopBits_1, USART_Parity_No, (USART_Mode_TypeDef)(USART_Mode_Rx | USART_Mode_Tx));开启接收中断USART_ITConfig(USART_IT_RXNE, ENABLE); //开启接收中断打开串口USART_Cmd(ENABLE);最后在开启总中断就可以啦enableInterrupts(); /* 开启总中断 */发个数据UART_SendString("This is a UART Demo \r\n");哈哈好使下面是完整的功能函数/********************************************************************** ********** 名称: Uart_Init* 功能: UART2初始化操作* 形参: 无* 返回: 无* 说明: 无*************************************************************************** ***/void Uart_Init(void){GPIO_Init(TXD_GPIO_PORT, TXD_GPIO_PINS, GPIO_Mode_Out_PP_Low_Fast);GPIO_Init(RXD_GPIO_PORT, RXD_GPIO_PINS, GPIO_Mode_In_PU_No_IT);// GPIO_ExternalPullUpConfig(GPIOC,GPIO_Pin_3|GPIO_Pin_4, ENABLE);CLK_PeripheralClockConfig(CLK_Peripheral_USART, ENABLE);USART_DeInit(); /* 将寄存器的值复位 *//** 将UART2配置为:* 波特率 = 9600* 数据位 = 8* 1位停止位* 无校验位* 使能接收和发送*/USART_Init((u32)9600, USART_WordLength_8D, USART_StopBits_1, \USART_Parity_No, (USART_Mode_TypeDef)(USART_Mode_Rx |USART_Mode_Tx));USART_ITConfig(USART_IT_RXNE, ENABLE); //开启接收中断USART_Cmd(ENABLE);enableInterrupts(); /* 开启总中断 */}11。

STM8CubeMX中文版用户使用手册

3.3.1 运行 STM8CubeMX 作为独立应用 ............................................................9

3.3.2 在命令行模式下运行 STM8CubeMX .........................................................9

2、主要特点 ............................................................................................................................................................................................................4

3.2.3 卸载 STM8CubeMX 独立版本 ....................................................................8

3.3 推出 STM8CubeMX ................................................................................................9

4.3 主界面 ....................................................................................................................19

4.4 工具栏和菜单 ........................................................................................................20

数字电路设计中的时钟树设计原理

数字电路设计中的时钟树设计原理

时钟树设计原理在数字电路设计中起着至关重要的作用,它主要用于在整个芯

片中分配和传递时钟信号,保证整个系统的同步性和稳定性。

时钟信号在数字电路中被广泛应用,它决定了数据的采样时间、触发时间和稳定性,是整个系统中最重要的信号之一。

时钟树设计的主要目的是传送时钟信号到整个芯片的各个部分,并确保各个部

分同时受到相同的时钟信号,避免出现时序偏差和时序冲突。

时钟树设计需要考虑到时钟信号的频率、延迟、功耗、噪声等多方面因素,以确保整个系统的性能和稳定性。

在时钟树设计中,一般会采用层次式的结构,将时钟信号从芯片的输入端传输

到各个功能模块,并通过缓存器、分频器、中继器等组件来进行时钟信号的分配和缓存,最终保证整个系统内部各个部分的同步。

时钟树设计中需要考虑的一个重要因素是时钟分配网络的拓扑结构,不同的拓

扑结构会对时钟信号的传输速度、功耗和稳定性等方面产生影响。

常见的拓扑结构包括二叉树结构、星型结构、环状结构等,根据具体的设计需求和性能指标选择合适的拓扑结构进行时钟树设计。

此外,时钟树设计中还需要考虑时钟信号的布线与布局,以减小时钟信号在传

输过程中的延迟和功耗,提高整个系统的性能。

合理的布线和布局可以降低时钟信号的传输损耗和噪声干扰,确保时钟信号能够准确、稳定地传输到各个功能模块。

总的来说,时钟树设计原理是数字电路设计中至关重要的一环,它直接影响到

整个系统的性能和稳定性。

通过合理的时钟树设计,可以确保系统内部各个功能模块的同步运行,提高系统的可靠性和性能,是数字电路设计中不可或缺的关键步骤。

时钟树综合(1)

时钟树综合(1)时钟树综合学习背景时钟信号是数据传输的基准,他对于同步数字系统的功能、性能、稳定性起决定性作⽤。

时钟信号通常是整个芯⽚中有最⼤扇出、通过最长距离、以最⾼速度运⾏的信号。

时钟信号必须要保证在最差的条件下,关键的时序要求能够满⾜,否则对时钟信号的任何不当的控制都可能导致紊乱情况,将错误的数据信号索存到寄存器,从⽽导致系统功能的错误。

时钟信号怎么产⽣的时钟信号源⼀般是从晶体(⽯英晶体、陶瓷晶体)产⽣的。

IC设计时通常会使⽤晶体振荡器来提供时钟源信号。

⼀般会使⽤PLL加上晶体振荡器来给芯⽚内部电路提供倍频或相位的时钟信号。

时钟信号特征时钟的周期(频率)、时钟延迟、时钟信号的不确定性是时钟的三个主要特征要素。

时钟信号延迟时钟信号延迟(latency)⼜称为插⼊延迟(insertion delay), 包括时钟源插⼊延迟和时钟⽹络插⼊延迟。

时钟源插⼊延迟是来⾃系统到当前芯⽚(当前模块)时钟根节点(clock root pin)之间的延迟,时钟⽹络插⼊延迟是时钟树的延迟。

时钟信号不确定性时钟信号的不确定性主要是有时钟信号抖动引起的,时钟抖动是先天存在的,所以在时钟树综合的时候只能考虑起影响,⽆法消除。

时钟抖动是信号实际时间与理想时间的偏差,抖动中含有确定抖动成分和随机抖动的成分【】。

时钟信号偏差时钟信号偏差是指同⼀时钟达到该时钟域内的不同寄存器之间的时间偏差,也即是skew=max(|t i−t j|)产⽣时钟偏差的原因有多种:时钟源到各个时钟端点的路径长度不同、各个端点负载不同、在时钟⽹中插⼊的缓冲器不同等。

在什么时候做时钟树综合:如下图所⽰,通常在物理设计布局完成之后布线之前进⾏时钟树综合。

在此之前所有的寄存器时钟信号是由同⼀个时钟pin驱动的,具有相同的延时的理想时钟。

已经⽣成了gatelevel 的netlist已经有⼀个初步的版图规划,每个逻辑门包括时序器件都有⼀个具体的位置。

已经基于理想时钟完成了时序优化设计。

芯片中时钟树综合质量评价指标

芯片中时钟树综合质量评价指标介绍时钟树是芯片设计中非常重要的一部分,它负责为芯片内的各个功能模块提供稳定的时钟信号。

时钟树的设计质量直接影响芯片的性能和功耗。

因此,对时钟树的综合质量进行评价是芯片设计过程中的重要任务。

时钟树的综合质量评价指标时钟树的综合质量评价指标主要包括以下几个方面:1. 时钟树延迟时钟树的延迟是指时钟信号从源端到达目的端所需的时间。

时钟树延迟的大小直接影响芯片的工作频率和时序要求。

因此,评价时钟树的综合质量时,需要考虑时钟树延迟是否满足设计要求。

2. 时钟树功耗时钟树的功耗是指时钟信号在时钟树中传输过程中所消耗的能量。

时钟树功耗的大小与时钟树的拓扑结构、电压和频率等因素有关。

评价时钟树的综合质量时,需要考虑时钟树功耗是否在可接受范围内。

3. 时钟树抖动时钟树的抖动是指时钟信号的相位或频率在传输过程中发生的变化。

时钟树抖动会导致芯片的时序偏差和时钟信号的不稳定性。

因此,评价时钟树的综合质量时,需要考虑时钟树抖动是否满足设计要求。

4. 时钟树噪声时钟树的噪声是指时钟信号中的不良成分,包括时钟信号的谐波、杂散等。

时钟树噪声会对芯片的功能模块产生干扰,影响芯片的性能和可靠性。

因此,评价时钟树的综合质量时,需要考虑时钟树噪声是否在可接受范围内。

评价指标的权重不同的芯片设计对时钟树的要求不同,因此,在评价时钟树的综合质量时,需要为不同的评价指标分配不同的权重。

一般来说,时钟树延迟和功耗是两个比较重要的指标,因为它们直接关系到芯片的性能和功耗。

而时钟树抖动和噪声相对来说可以适当放宽要求。

评价方法和工具评价时钟树的综合质量可以采用静态分析和动态仿真的方法。

静态分析是指通过对时钟树的结构和参数进行分析,预测时钟树的性能指标。

动态仿真是指通过模拟时钟信号在时钟树中的传输过程,评估时钟树的实际性能。

评价时钟树的综合质量还可以借助一些专门的工具,如PrimeTime、HSPICE等。

这些工具可以对时钟树进行详细的分析和仿真,提供时钟树的延迟、功耗、抖动和噪声等性能指标。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

STM8库函数学习笔记之时钟树解析STM8库函数学习笔记之时钟管理相关函数:void CLK_DeInit(void);void CLK_HSEC md(FunctionalState NewState);void CLK_HSIC md(FunctionalState N ewState);void CLK_LSICmd(FunctionalState NewState);void CLK_CCOCmd(FunctionalState NewState);void CLK_ClockSwitchC md(FunctionalState NewState);void CLK_FastHaltWakeUpCmd(FunctionalState N ewState);void CLK_SlowActiveHaltWakeUpCmd(FunctionalState NewState);void CLK_PeripheralC lockConfig(CLK_Peripher al_TypeDef CLK_Peripheral, FunctionalState NewState);ErrorStatus CLK_C lockSwitchConfig(CLK_SwitchMode_TypeDef CLK_Sw itchMode, C LK_Source_TypeDef CLK_NewClock, FunctionalStateITState, CLK_CurrentClockState_TypeDef CLK_CurrentClockState);void CLK_HSIPr escalerConfig(CLK_Prescaler_TypeDef HSIPrescaler);void CLK_CCOConfig(CLK_Output_TypeD ef CLK_CCO);void CLK_ITConfig(CLK_IT_TypeDef CLK_IT, FunctionalState NewState);void CLK_SYSCLKC onfig(CLK_Pr escaler_TypeDef CLK_Prescaler);void CLK_SWIMConfig(CLK_SWIMD ivider_TypeDef CLK_SWIMDivider);void CLK_CANConfig(CLK_C ANDivider_TypeD ef CLK_CANDivider);void CLK_ClockSecuritySystemEnable(void);void CLK_SYSCLKEmergencyClear(void);void CLK_AdjustHSICalibrationValue(CLK_HSITrimValue_TypeDef CLK_HSIC alibrationValue);u32 CLK_GetC lockFreq(void);CLK_Source_TypeD ef CLK_GetSYSCLKSource(void);FlagStatus CLK_GetFlagStatus(CLK_Flag_TypeDef C LK_FLAG);ITStatus CLK_GetITStatus(CLK_IT_TypeDef CLK_IT);void CLK_ClearITPendingBit(CLK_IT_TypeDef CLK_IT);//-----------------------------------------------------------------------------------------void CLK_DeInit(void);恢复相关的时钟寄存器到默认值参数:无返回值:无注意:当要复位CCOR寄存器时,如果CCOEN位被置位,则需要先复位CCOEN位,然后再复位CCOSEL位,复位CCOEN位和复位CCOSEL位的操作必须连续。

这个理解不知对不对,是根据库函数的帮助来理解的,但测试结果,无论CCOEN是否置位,调用后都能恢复CCOR寄存器。

//-----------------------------------------------------------------------------------------void CLK_HSEC md(FunctionalState NewState);启用或禁用外部高速振荡器(HSE)参数:NewState: 新的状态值DISABLE 禁用ENABLE 启用返回值:无//-----------------------------------------------------------------------------------------void CLK_HSIC md(FunctionalState N ewState);启用或禁用内部高速振荡器(HSI 16MHz)参数:NewState: 新的状态值DISABLE 禁用ENABLE 启用返回值:无//-----------------------------------------------------------------------------------------void CLK_LSICmd(FunctionalState NewState);启用或禁用内部低速振荡器(LSI 128KHz)参数:NewState: 新的状态值DISABLE 禁用ENABLE 启用返回值:无//-----------------------------------------------------------------------------------------void CLK_CCOCmd(FunctionalState NewState);启用或禁用可配置的时钟输出功能参数:NewState: 新的状态值DISABLE 禁用ENABLE 启用返回值:无//-----------------------------------------------------------------------------------------void CLK_ClockSwitchC md(FunctionalState NewState);手动启动或关闭时钟切换参数:NewState: 新的状态值DISABLE 禁用ENABLE 启用返回值:无//-----------------------------------------------------------------------------------------void CLK_FastHaltWakeUpCmd(FunctionalState N ewState);使能或禁止从停机模式(Halt)或活跃停机模式(Active Halt)中快速唤醒。

停机模式(Halt):CPU和片上设备完全停止工作,定时唤醒单元AWU也停止,仅由外部中断及复位唤醒。

活跃停机模式(Active Halt):保留一个定时唤醒单元AWU工作,CPU和片上设备全停止工作,AWU和外部中断及复位均可唤醒使能后内部高速振荡器(HSI)会自动打开,且作为主时钟源(fMASTER)(CKM=SWI=HSI),然后从停机模式(Halt)或活跃停机模式(Active Halt)中快速唤醒。

返回值:无//-----------------------------------------------------------------------------------------void CLK_SlowActiveHaltWakeUpCmd(FunctionalState NewState);启用或禁止活跃停机模式下的电压调节器但是这个函数并没有字面上的唤醒功能。

但是跟自动唤醒(AWU)功能有关。

一旦MCU进入活跃停机模式时,主电压调节器将默认关闭(DISABLE),从而唤醒时间将比较长,所以这个函数就为了在快速唤醒与低功耗之间选择。

参数:NewState: 新的状态值DISABLE 禁用ENABLE 启用返回值:无如果为了能快速从活跃停机模式中唤醒,进入活跃停机前则调用CLK_SlowActiveH altWakeUpCmd(ENABLE);但功耗较大。

如果进入活跃停机模式前没有调用CLK_SlowActiveHaltWakeUpCmd(ENABLE);或调用了CLK_SlowActiveHaltWakeUpCmd(DISABLE);即默认的情况下,唤醒时间比较长,但功耗较低。

关于AWU(自动唤醒功能的详细说明请查看手册)//-----------------------------------------------------------------------------------------void CLK_PeripheralC lockConfig(CLK_Peripher al_TypeDef CLK_Peripheral, FunctionalState NewState);启用或禁用指定的外设时钟,默认所有的外设时钟都是启用的。

参数:CLK_Peripher al 外设类型可选值:CLK_PERIPHERAL_I2CCLK_PERIPHERAL_SPICLK_PERIPHERAL_UAR T1CLK_PERIPHERAL_UAR T2CLK_PERIPHERAL_UAR T3CLK_PERIPHERAL_TIMER6CLK_PERIPHERAL_TIMER4CLK_PERIPHERAL_TIMER5CLK_PERIPHERAL_TIMER2CLK_PERIPHERAL_TIMER3CLK_PERIPHERAL_TIMER1CLK_PERIPHERAL_AWUCLK_PERIPHERAL_ADCCLK_PERIPHERAL_CANNewState: 新的状态值DISABLE 禁用ENABLE 启用返回值:无//-----------------------------------------------------------------------------------------ErrorStatus CLK_C lockSwitchConfig(CLK_SwitchMode_TypeDef CLK_Sw itchMode, C LK_Source_TypeDef CLK_NewClock, FunctionalStateITState, CLK_CurrentClockState_TypeDef CLK_CurrentClockState);系统时钟切换配置参数:CLK_Sw itchMode, 切换模式可选值:CLK_SWITCHMODE_MANUAL 手动切换CLK_SWITCHMODE_AU TO 自动切换CLK_NewC lock,新的时钟源可选值:CLK_SOURCE_HSI 内部16MH z高速振荡器CLK_SOURCE_LSI 内部128KHz低速振荡器CLK_SOURCE_HSE 外部时钟ITState,启用或禁用时钟切换中断可选值:DISABLE 禁用ENABLE 启用CLK_CurrentClockState,当前使用的时钟源在切换到新的时钟源后关闭或继续开启。