高手带你理解STM32系统时钟和分频

stm32时钟详细说明

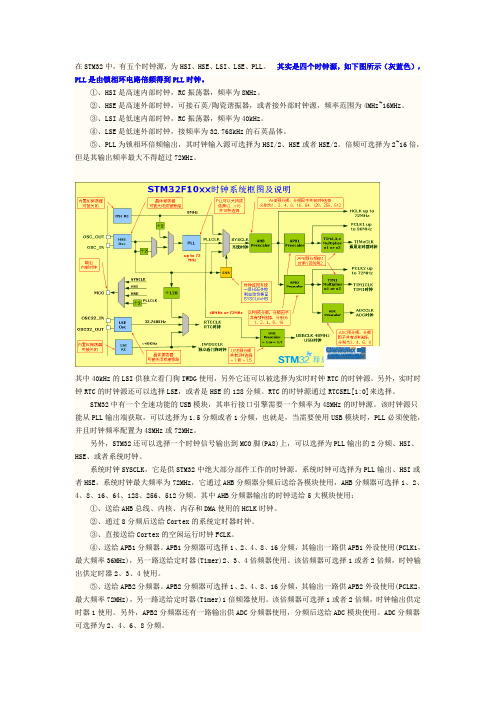

在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

其实是四个时钟源,如下图所示(灰蓝色),PLL是由锁相环电路倍频得到PLL时钟。

①、HSI是高速内部时钟,RC振荡器,频率为8MHz。

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

③、LSI是低速内部时钟,RC振荡器,频率为40kHz。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

⑤、PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。

倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

其中40kHz的LSI供独立看门狗IWDG使用,另外它还可以被选择为实时时钟RTC的时钟源。

另外,实时时钟RTC的时钟源还可以选择LSE,或者是HSE的128分频。

RTC的时钟源通过RTCSEL[1:0]来选择。

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。

该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

另外,STM32还可以选择一个时钟信号输出到MCO脚(PA8)上,可以选择为PLL输出的2分频、HSI、HSE、或者系统时钟。

系统时钟SYSCLK,它是供STM32中绝大部分部件工作的时钟源。

系统时钟可选择为PLL输出、HSI或者HSE。

系统时钟最大频率为72MHz,它通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。

其中AHB分频器输出的时钟送给5大模块使用:①、送给AHB总线、内核、内存和DMA使用的HCLK时钟。

②、通过8分频后送给Cortex的系统定时器时钟。

③、直接送给Cortex的空闲运行时钟FCLK。

④、送给APB1分频器。

STM32入门教程--系统时钟配置

STM32 系统时钟配置一、STM32的时钟系统时钟是什么?时钟通常是振荡器(如晶振)产生的特定频率的方波信号,时钟周期是时钟频率的倒数,时钟频率1MHz时钟周期为1/1000000=1us。

时钟周期是MCU处理指令的最小时间单元,每个程序指令都需要若干个时钟周期,MCU的时钟频率越快,完成一个指令的时间就越短,速度就越快。

时钟是MCU运行的基础,好比MCU的脉搏,是MCU性能的重要参数。

每个MCU 都是在某个特定的时钟频率下进行工作的,如C51单片机时钟频率为12MHz,而STM32F103 的系统时钟频率是72MHz。

STM32的时钟系统STM32时钟频率较高,时钟越快功耗越大,同时抗电磁干扰能力也会越弱。

而且STM32外设非常多,而通常外设是不需要像系统时钟那么高的频率的,比如看门狗和RTC 只需要几十K的时钟即可。

另外实际使用的时候通常只会用到有限的几个外设,STM32可以只给需要启动的外设分配时钟,以此来降低功耗。

由此可看出STM32 的时钟系统较为复杂,它采用了多个时钟源的方法来解决这些问题。

STM32 有4个独立时钟源:HSI、HSE、LSI、LSE。

①、HSI是高速内部时钟,RC振荡器,频率为8MHz,精度不高。

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

③、LSI是低速内部时钟,RC振荡器,频率为40kHz,提供低功耗时钟。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

其中LSI是作为IWDGCLK(独立看门狗)时钟源和RTC时钟源而独立使用,HSI高速内部时钟 HSE高速外部时钟 PLL锁相环时钟这三个经过分频或者倍频作为系统时钟来使用基本时钟源(图中绿色箭头指出):(1)HSI高速内部时钟,RC振荡器,8MHz。

(2)HSE高速外部时钟,石英/陶瓷谐振器,8MHz。

(3)LSI低速内部时钟,RC振荡器,40kHz。

STM32时钟要先倍频N倍再分频的原因是什么?

STM32时钟要先倍频N倍再分频的原因是什么?

有些朋友不理解为什么STM32时钟要先倍频N倍,再分频?你会担心这个值太大吗?

1写在前面

STM32时钟的功能,可以说是越来越强大了。

从各个系列的时钟树可以看得出来,最早F1系列的时钟功能相对比较简单,到这后面H7、G0的时钟越来越丰富。

今天讲述一下其中的PLL环节。

2关于PLL

什么是PLL?

PLL:Phase Locked Loop锁相环。

PLL用于振荡器中的反馈技术,通常需要外部的输入信号与内部的振荡信号同步。

一般的晶振由于工艺与成本原因,做不到很高的频率,而在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路就可以实现稳定且高频的时钟信号。

每一块STM32处理器至少都有一个PLL,有的甚至有好几个PLL。

比如,F4有两个PLL:

F7有三个PLL:

当然,每个MCU型号不同,其PLL数量,及功能也有差异,具体需要看相应手册。

3STM32CubeMX配置时钟树

STM32CubeMX配置时钟不用担心出错。

原因很简单,这个工具配置时钟树,如果出错,会有红色警告。

如下图:。

stm32分频原理

stm32分频原理

STM32微控制器的分频原理涉及到时钟树结构和各种时钟源的

分频设置。

在STM32微控制器中,时钟源包括内部RC振荡器、内部

晶体振荡器、外部晶体振荡器等,这些时钟源可以通过各种分频器

进行分频,以得到不同频率的时钟信号用于驱动不同的模块。

首先,STM32微控制器的时钟树结构包括主时钟源(HSI、HSE、PLL等)和各种外设时钟源(AHB、APB1、APB2等)。

主时钟源可以

通过PLL进行倍频,得到高频时钟用于驱动CPU和其他模块;外设

时钟源则可以通过预分频器进行分频,得到适合外设工作的时钟频率。

其次,分频原理涉及到寄存器的设置。

在STM32中,通过对时

钟控制寄存器(RCC寄存器)进行配置,可以实现对时钟源的选择

和分频设置。

比如,可以通过设置PLL寄存器来配置PLL倍频系数,通过设置AHB分频寄存器来配置AHB总线的分频系数,通过设置

APB分频寄存器来配置APB总线的分频系数等。

另外,需要注意的是,分频设置需要考虑时钟频率的稳定性和

功耗的控制。

过高或过低的时钟频率都可能导致系统不稳定,而且

过高的频率会增加功耗,过低的频率则可能影响系统性能。

总的来说,STM32微控制器的分频原理涉及到时钟树结构、时钟源的选择和分频设置,通过对相关寄存器进行配置,可以实现对时钟信号的灵活控制,以满足不同外设的工作需求。

同时,合理的分频设置也可以帮助优化系统的功耗和性能。

stm32时钟概念

stm32时钟概念STMicroelectronics的STM32系列是一系列基于ARM Cortex-M 内核的微控制器(MCU)。

时钟系统在STM32芯片中是一个关键的概念,因为它驱动了芯片内部的各种功能模块,包括CPU、外设、总线等。

以下是与STM32时钟相关的一些基本概念:1. 系统时钟(SYSCLK): SYSCLK是STM32中的主时钟,它驱动CPU和内存等核心模块。

其频率由时钟源和分频器的组合决定。

2. 时钟源: STM32芯片通常支持多个时钟源,包括内部RC振荡器、外部晶体振荡器、PLL(相位锁定环)等。

选择适当的时钟源取决于应用的要求,例如需要更高的稳定性或更低的功耗。

3. PLL(Phase-Locked Loop):PLL是一种用于产生高稳定性时钟信号的电路。

通过将一个参考时钟信号与一个可调节的倍频器相锁定,PLL可以生成一个高频率的时钟信号。

4. AHB、APB总线:在STM32中,系统总线被分为高性能总线(AHB)和低速外设总线(APB)。

这两个总线有各自的时钟域,因此可以独立配置时钟。

这种分级的结构有助于提高系统的性能和灵活性。

5. 时钟树:时钟树描述了时钟系统的层次结构,显示了时钟源如何通过PLL和分频器传递到各个模块。

了解时钟树结构对于调整系统时钟和解决时钟相关问题非常有用。

6. 时钟配置寄存器: STM32芯片具有一系列寄存器,允许程序员配置时钟系统。

这些寄存器包括RCC寄存器(RCC,Reset and Clock Control)等,通过编程这些寄存器,可以设置各种时钟参数。

7. 低功耗模式时钟: STM32芯片支持不同的低功耗模式,如停机模式、待机模式等。

在这些模式下,可以降低系统的功耗,因此时钟系统在这些模式下的配置也需要考虑。

时钟配置通常是在启动代码或初始化过程中完成的,程序员可以通过修改相应的寄存器来调整时钟设置以满足应用的需求。

对于具体的时钟配置和使用,建议查阅STMicroelectronics提供的芯片手册和相关文档。

STM32单片机的5个时钟源解析

a。HSI

b。HSE

c。PLL

3. RTC的时钟来源

a。LSE

b。LSI

c。LSE的128分频

4.独立看门狗IWDGCLK的时钟来源

LSI

B的时钟USBCLK的来源

最大频率为48MHz

PLL经过预分频器产生1或1.5分频

6.内部时钟输出MCO,为STM32芯片的一个引脚PA8

a。SYSCLK

b。HSI

c。HSE

d。PLL时钟的2分频

7. APB1总线的时钟,最大到36M

8. APB2总线的时钟,最大到72M

APB,APB1,APB2为外设提供时钟

所有时钟都有时钟使能,只有时钟打开时外设才能使用。

对于时钟的配置

见《STM32中文参考手册》

三。系统时钟系统初始化重要函数

SystemInit();

STM32单片机的5个时钟源解析

一。时钟系统框图讲解

1. STM32的5个时钟源

a。高速内部时钟HSI,大约为8MHz

b。高速外部时钟HSE,晶振取值范围在4M--16M,一般采用8M晶振

c。低速外部时钟LSE,32.768k晶振,可以作为RTC的时钟源

d。低速内部时钟LSI,大约为40KHz

e。PLL锁相环时钟

四。系统时钟配置调用函数

RCC_HSE_Configuration();

注意:在使能任何一个时钟的时候,要等待时钟稳定后才能继续。

BLX R0

LDR R0,=__main //再执行main()函数

BX R0

ENDP

该函数默认定义系统时钟为72MHz

#defineSYSCLK_FREQ_72MHz 72000000

STM32系统时钟配置

STM32系统时钟配置STM32 在使用不同时钟晶振时,需要对系统时钟进行配置。

下面以16MHz晶振产生72MHz时钟为例进行说明。

由于STM32可进行整数倍倍频,及可选是否2分频。

因而选用16MHz 晶振时,先2分频,再倍频9倍,即可倍频为72MHz。

①查找SystemInit() 函数,即系统时钟设置:图1②进入 SetSysClockTo72() 函数,如果要设置其他频率,进入对应的频率即可,如SetSysClockTo48()。

③参考 STM32中文参考手册的6.3.2时钟配置寄存器(RCC_CFGR)。

如“位17PLLXTPRE ” 所述:HSE分频器作为PLL输入(HSE divider for PLL entry)由软件置’1’或清’0’来分频HSE后作为PLL输入时钟。

只能在关闭PLL时才能写入此位。

0:HSE不分频1:HSE 2分频因而,RCC_CFGR 寄存器的位17 应置“1”。

④如图2红色框中所示,RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL));RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL9|RCC_CFGR_PLLXTPRE);添加红色字部分即可完成2分频,则可将16MHz的时钟分频为8MHz。

其实,查找RCC_CFGR_PLLXTPRE宏定义可知:#define RCC_CFGR_PLLXTPRE ((uint32_t)0x00020000)实际上就是将位 17置1。

而RCC_CFGR_PLLMULL9中的9即是倍频倍数。

(8*9=72 MHz)图2⑤如图3所示,全局查找72000000(按住Ctrl+Shift+F,输入72000000),找到SYSCLK_FREQ_72MHz 的宏定义,将其注释取消。

STM32时钟分频因子

STM32时钟分频因子就是定时器频率的分频数值。

不过预分频是时钟输入定时器之前分频,分频则是使用输出时候分频。

不做精确的PPG和步进电机控制的话,区别不大都是分频用的预分频是时钟输入定时器之前分频,分频则是使用输出时候分频时钟分频因子,配置死区时间时用到 .无关的话:关于TIM的时钟分频因子Clock division 是什么,他的作用是什么。

网上找了很多解释,说的人更加一头雾水!于是自己研究,先看其定义时钟分频因子的定义:官方参考手册P377页TIM1和TIM8的时钟控制寄存器(TIMX_CR1)的第9:8位是这样定义的This bit-field indicates the division ratio between the timer clock (CK_INT) frequency and the dead-time and sampling clock (tDTS)used by the dead-time generators and the digital filters (ETR, TIx),00: tDTS=tCK_INT01: tDTS=2*tCK_INT10: tDTS=4*tCK_INT11: Reserved, do not program this value翻译过来就是:这两个位指示(设定)了分割比率(分频率)在:定时器时钟频率,死区,用于死区发生器的采样时钟,数字滤波器之间。

定义的理解:*简单的说就是分频因子是通过对CK_INT的分割来确定tDTS的!*分频因子只是分频的手段,它的目的就是得到tDTS!*而tDTS主要用于,死区用于死区发生器的采样时钟和数字滤波器,也就是它要作用于这三个东西上。

*我们再来看它的结果(就是设定了这两位引发的结果),只有一个就是给出了tDTS的值。

好多人不理解就出在这个问题上,tDTS是什么呢,它其实就是一个时间值,这个值会用于下面说的三个地方。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCLK1:0x2255100 //36000000, 36MHz PCLK2:0x44aa200 //72000000, 72MHz ADCCLK:0x2255100 //36000000,36MHz RCC->CFGR:0x001D040A //PLL 输出作为系统时钟 可推测几个预分频值为 AHB prescaler = 1 APB1 prescaler = 2 APB2 prescaler = 1 ADC prescaler = 2 根据读取 RCC->CFGR 寄存器值为:0x001D040A,上面推测完全正确。 CFGR 寄存器的 SWS 段也说明:PLL 输出作为系统时钟。 TIM2 使用 PCLK1,但注意时钟树里有这一段 见附图

高手带你理解 STM32 系统时钟和分频

首先来手册里的一段话。 三种不同的时钟源可被用来驱动系统时钟 (SYSCLK) - HSI 振荡器时钟 - HSE 振荡器时钟 - PLL 时钟 一般用的是 PLL 时钟,后面有证据。 我们可以通过库函数获取各时钟值 void RCC_GetClocksFreq(RCC_ClocksTypeDef* RCC_Clocks) 在我的系统里,把时钟值打印信息如下: SYSCLK:0x44aa200 //72000000, 72MHz HCLK:0x44aa200 //72000000, 72MHz

已知 APB1 prescaler=2,故 TIM2CLK = PCLK1*2 = 72MHz. 所以被 TIM2 分频的时钟大小是 72MHz。 我的程序也证明了这点 TIM_TimeBaseInitTypeDef tim2_InitStruct; TIM_DeInit(TIM2); RCC_APB1PeriphClockCmd(RCC_APB1Periph_TIM2, ENABLE);//Enable Timer2 clock. NVIC_ConfigurationForTimer2(); // PCLK1=36MHz, PSC=36000-1, CK_CNT=36MHz/(PSC+1)=1000 // ARR=2000, 1s/1000 * 2000 = 2s.

tim2_InitStruct.TIM_Prescaler = 36000-1; tim2_InitStruct.TIM_Period = 2000-1; tim2_InitStruct.TIM_CounterMode = TIM_CounterMode_Up; tim2_InitStruct.TIM_ClockDivision = TIM_CKD_DIV1; tim2_InitStruct.TIM_RepetitionCounter = 0; TIM_TimeBaseInit(TIM2, &tim2_InitStruct); TIM_ClearFlag(TIM2, TIM_FLAG_Update); TIM_ITConfig(TIM2, TIM_IT_Update, ENABLE);//Enables the specified TIM interrupts. 这段配置原本以为定时时间是 2s,实际只有 1s。看了手册才理解原因。