51系列单片机P0端口具体讲解

51单片机程序引脚定义规则

51单片机程序引脚定义规则

51单片机(通常指的是8051系列单片机)是一种非常常见的微控制器,广泛应用于各种嵌入式系统。

它的程序引脚定义规则是固定的,通常由单片机的制造商提供。

以下是一个简化的51单片机引脚定义规则:

1. P0口:通常作为低8位I/O端口使用。

在访问外部存储器时,P0口也作为低8位地址/数据总线使用。

2. P1口:通常作为8位I/O端口使用。

3. P2口:通常作为高8位地址/数据总线使用,或作为辅助I/O端口。

4. P3口:除了标准的I/O功能外,P3口还有额外的功能,如中断、串行通信等。

5. P4口:在一些扩展型的51单片机中存在,通常作为附加的I/O端口或地址总线。

6. P5口:在一些扩展型的51单片机中存在,通常作为附加的I/O端口或地址总线。

7. P6口:在一些扩展型的51单片机中存在,通常作为附加的I/O端口或地址总线。

8. P7口:在一些扩展型的51单片机中存在,通常作为附加的I/O端口或地址总线。

以上只是一种通用的描述,具体的引脚定义可能会因不同的51单片机型号而有所不同。

为了获得准确的引脚定义,你应该查阅你所使用的单片机的数据手册或参考手册。

51单片机的IO口

51单片机的I O口.2P0口作为普通I/O口:①输出时,CPU发出控制电平"0"封锁"与"门,将输出上拉场效应管T1截止,同时使多路开关MUX把锁存器与输出驱动场效应管T2栅极接通。

故内部总线与P0口同相。

由于输出驱动级是漏极开路电路,若驱动NMOS或其它拉流负载时,需要外接上拉电阻。

P0的输出级可驱动8个LSTTL负载。

②输入时--分读引脚或读锁存器读引脚:由传送指令(MOV)实现;下面一个缓冲器用于读端口引脚数据,当执行一条由端口输入的指令时,读脉冲把该三态缓冲器打开,这样端口引脚上的数据经过缓冲器读入到内部总线。

读锁存器:有些指令如:ANLP0,A称为"读-改-写"指令,需要读锁存器。

上面一个缓冲器用于读端口锁存器数据。

*原因:如果此时该端口的负载恰是一个晶体管基极,且原端口输出值为1,那么导通了的PN结会把端口引脚高电平拉低;若此时直接读端口引脚信号,将会把原输出的"1"电平误读为"0"电平。

现采用读输出锁存器代替读引脚,图中,上面的三态缓冲器就为读锁存器Q端信号而设,读输出锁存器可避免上述可能发生的错误。

*说明:nP0口必须接上拉电阻;n在读信号之前数据之前,先要向相应的锁存器做写1操作的I/O口称为准双向口;n三态输入缓冲器的作用:n(ANLP0,A)准双向口:从图中可以看出,在读入端口数据时,由于输出驱动FET并接在引脚上,如果T2导通,就会将输入的高电平拉成低电平,产生误读。

所以在端口进行输入操作前,应先向端口锁存器写"1",使T2截止,引脚处于悬浮状态,变为高阻抗输入。

这就是所谓的准双向口。

2、P0作为地址/数据总线在系统扩展时,P0端口作为地址/数据总线使用时,分为:(1)P0引脚输出地址/数据信息:CPU发出控制电平"1",打开"与"门,又使多路开关MUX把CPU的地址/数据总线与T2栅极反相接通,输出地址或数据。

单片机IO端口工作原理(P0端口,漏极开路,推挽,上拉电阻,准双向口)

单片机IO端口工作原理(P0端口,漏极开路,推挽,上拉电阻,准双向口)一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:输入缓冲器:在P0口中,有两个三态的缓冲器,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态。

图中有一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

图中另一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

图中的锁存器,D 端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q 非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为‘地址/数据’总线使用。

那么这个多路选择开关就是用于选择是做为普通I/O口使用还是作为‘数据/地址’总线使用的选择开关了。

51单片机各引脚

51单片机各引脚51单片机是一种广泛应用于嵌入式系统中的微控制器。

它具有多种功能引脚,这些引脚在不同的电路和项目中起着不同的作用。

本文将对51单片机的各引脚进行介绍和解释。

引脚P0: P0口是51单片机最常用的I/O口之一。

P0口具有8个引脚,可以通过设置它们的电平来进行数据输入/输出。

它通常用于连接外部设备,如LED灯、按键、数码管等。

P0口可以配置为输入端口或输出端口,可以通过程序对其进行控制和操作。

引脚P1: P1口也是51单片机的一个I/O口。

P1口同样具有8个引脚,与P0口相比,P1口的输入输出能力更强。

它通常用于连接外部设备,如LCD液晶显示屏、继电器、蜂鸣器等。

P1口同样可以配置为输入端口或输出端口,通过程序可以对其进行高低电平的控制。

引脚P2: P2口是51单片机的另一个I/O口。

P2口也具有8个引脚,它通常用于连接外部设备,如ADC(模数转换器)、数码管、EEPROM(电可擦程存储器)等。

P2口同样可以配置为输入端口或输出端口,并能通过程序进行控制。

引脚P3: P3口是51单片机最后一个I/O口。

P3口也具有8个引脚,它通常用于连接外部设备,如定时器、串口通信、中断控制等。

与其他I/O口不同的是,P3口的引脚具有特殊功能,比如RXD(接收数据)、TXD(发送数据)等。

P3口同样可以配置为输入端口或输出端口,并能通过程序进行相应的操作。

除了I/O口之外,51单片机还具有一些其他的引脚,如电源引脚、晶振引脚、复位引脚等。

这些引脚对于单片机的正常工作至关重要。

电源引脚: 51单片机通常需要接受电源供电才能工作,因此具有供电引脚。

根据具体型号的不同,51单片机的电源引脚可以是VCC (正电源)、GND(地线)、AVCC(模拟电源)等。

晶振引脚: 51单片机需要外部晶振来提供时钟信号,以保证其正常工作。

因此,51单片机具有晶振引脚,一般为两个引脚:XTAL1(晶体振荡器输入端,接入外部晶振的输入端)和XTAL2(晶体振荡器输出端,接入外部晶振的输出端)。

单片机P0端口的结构及工作原理

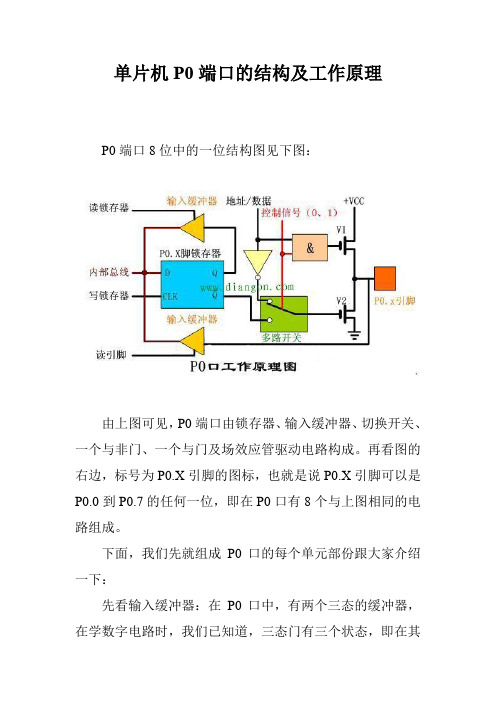

单片机P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X 引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为‘地址/数据’总线使用。

MCS-51单片机IO口详解

单片机IO口结构及上拉电阻MCS-51有4组8位I/O口:P0、P1、P2和P3口,P1、P2和P3为准双向口,P0口则为双向三态输入输出口,下面我们分别介绍这几个口线。

一、P0口和P2口图1和图2为P0口和P2口其中一位的电路图。

由图可见,电路中包含一个数据输出锁存器(D触发器)和两个三态数据输入缓冲器,另外还有一个数据输出的驱动(T1和T2)和控制电路。

这两组口线用来作为CPU与外部数据存储器、外部程序存储器和I/O扩展口,而不能象P1、P3直接用作输出口。

它们一起可以作为外部地址总线,P0口身兼两职,既可作为地址总线,也可作为数据总线。

图1 单片机P0口内部一位结构图图2 单片机P0口内部一位结构图P2口作为外部数据存储器或程序存储器的地址总线的高8位输出口AB8-AB15,P0口由ALE选通作为地址总线的低8位输出口AB0-AB7。

外部的程序存储器由PSEN信号选通,数据存储器则由WR和RD读写信号选通,因为2^16=64k,所以MCS-51最大可外接64kB的程序存储器和数据存储器。

二、P1口图3为P1口其中一位的电路图,P1口为8位准双向口,每一位均可单独定义为输入或输出口,当作为输入口时,1写入锁存器,Q(非)=0,T2截止,内上拉电阻将电位拉至"1",此时该口输出为1,当0写入锁存器,Q(非)=1,T2导通,输出则为0。

图3 单片机P2口内部一位结构图作为输入口时,锁存器置1,Q(非)=0,T2截止,此时该位既可以把外部电路拉成低电平,也可由内部上拉电阻拉成高电平,正因为这个原因,所以P1口常称为准双向口。

需要说明的是,作为输入口使用时,有两种情况:1.首先是读锁存器的内容,进行处理后再写到锁存器中,这种操作即读—修改—写操作,象JBC(逻辑判断)、CPL(取反)、INC(递增)、DEC(递减)、ANL(与逻辑)和ORL(逻辑或)指令均属于这类操作。

2.读P1口线状态时,打开三态门G2,将外部状态读入CPU。

8051单片机p0端口工作原理

8051单片机p0端口工作原理一、前言8051单片机是一种广泛应用于嵌入式系统中的微控制器,其具有成本低、易于使用和可靠性高等优点。

P0端口是8051单片机的一个重要端口,它通常用于控制外部设备和与其他设备进行通信。

本文将详细介绍8051单片机P0端口的工作原理。

二、8051单片机概述8051单片机是由Intel公司在1980年推出的一款8位微控制器,它采用了Harvard结构,并且具有4K字节的ROM、128字节的RAM 和32个I/O端口等特点。

其主要特点如下:1. 8位CPU:具有12个寄存器,可以直接访问内部和外部数据。

2. 存储器:包括4K字节ROM和128字节RAM。

3. I/O端口:包括32个I/O端口,其中P0、P1、P2、P3四个端口是最常用的。

4. 定时器/计数器:具有两个16位定时器/计数器。

5. 中断系统:支持5种不同类型的中断源。

6. 串行通信接口:支持UART模式和SPI模式。

7. 其他功能:包括PWM输出、ADC输入等。

三、P0端口概述P0端口是8051单片机的一个8位双向I/O端口,它的引脚编号为P0.0~P0.7。

在默认情况下,P0端口的所有引脚都被配置为输入状态,并且具有上拉电阻。

当需要使用P0端口时,需要将其相应的引脚配置为输出状态,并且需要关闭上拉电阻。

四、P0端口工作原理1. P0端口寄存器P0端口是通过一个8位寄存器来控制的,该寄存器的地址为80H。

当写入数据到该寄存器时,数据会被输出到对应的引脚上。

当从该寄存器读取数据时,会返回当前引脚上的输入数据。

2. P0端口模式设置P0端口可以通过特定的位掩码来配置其模式。

其中,每个引脚都有两个对应的位用于控制其模式:- P0Mx:用于选择引脚是否为输入或输出。

- P0Px:用于选择是否启用内部上拉电阻。

其中,x表示对应引脚编号(例如:P0M1表示P0.1引脚的模式选择位)。

3. P0端口输入输出控制在将某个引脚配置为输出状态后,可以通过向相应位写入逻辑高或逻辑低来控制该引脚的输出电平。

51单片机的P1、P2、P3口的工作原理

基于proteus的51单片机仿真实例五十、51单片机的P1、P2、P 3口的工作原理1、P1口某一位的内部电路结构如下图所示,在51单片机的P0,P1,P2,P3口中,P1口的结构最简单,用途也最单一。

仅仅只作为普通的数据输入/输出(I/O)端口使用。

从图中可以看出,P0口与P1口的主要差别在于:P1端口用内部上拉电阻代替了P0端口的场效应管,并且输出的信息只有内部总线的信息,没有了数据/地址总线的复用。

1)P1口用作输入端口如果P1口用作输入端口,即Q=0,/Q=1;则场效应管导通,引脚被直接连到电源的地GND上,即使引脚输入的是高电平,被直接拉低为“0“,所以,与P0端口一样,在将数据输入P1端口之前,先要通过内部总线向锁存器写”1“,这样/Q=0,场效应管截止,P1端口输入的“1”才可以送到三态缓冲器的输入端,此时再给三态门的读引脚送一个读控制信号,引脚上的“1”就可以通过三态缓冲器送到内部总线。

具有这种操作特点的输入/输出端口,一般称之为准双向I/O口,51单片机的P1,P2,P3口都是准双向口。

而P0端口由于输出具有三态功能(输出端口的三态是指:高电平,低电平,高阻态这三态),所以在作为输入端口时,无需先写“1”然后再进行读操作。

2)P1口用作输出端口如果P1口用作输出端口,应给锁存器的写锁存CP端输入写脉冲信号,内部总线送来的数据就可以通过D端进入锁存器并从Q和/Q端输出,如果D端输入“1”,则/Q=0,场效应管截止,由于上拉电阻的作用,在P1.X引脚输出高电平“1”,反之,如果D端输入“0”,则/Q =1,场效应管导通, P1.X引脚连到地线上,从而在引脚输出“0”。

2、P2口的内部电路结构如下图所示,可以看出P2口既有片内上拉电阻,又有切换开关MUX,所以P2口在功能上兼有P0和P1端口的特点,这主要体现在输出功能上,当切换开关向下接通时,从内部总线输出的一位数据经反相器和场效应管反相后,输出在端口引脚线上;当多路开关向上时,输出的一位地址信号也经反相器和场效应管反相后,输出在端口引脚线上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

有关单片机P0口具体讲解

图1

(一)在我们讲解P0端口之前我们首先梳理一下各个端口有什

么不同之处:

P0口有三个功能:

1、外部扩展存储器时,当做数据(Data)总线(如图1中的D0~D7为数据总线接口)

2、外部扩展存储器时,当作地址(Address)总线(如图1中的A0~A7为地址总线接口)

3、不扩展时,可做一般的I/O使用,但内部无上拉电阻,作为输入或输出时应在外部接上拉电阻(后面将详细介绍)。

P1口只做I/O口使用:其内部有上拉电阻。

P2口有两个功能:

1、扩展外部存储器时,当作地址总线使用(如图1中的A8~A15为地址总线接口)

2、做一般I/O口使用,其内部有上拉电阻;

P3口有两个功能:

除了作为I/O使用外(其内部有上拉电阻),还有一些特殊功能,由特殊寄存器来设置,具体功能请参考我们后面的引脚说明。

图2(注:该图只是P0口的一位,也就是说P0口有8个相同的这样的结构)

图3

(二)由图2可以看出每个P0口都有这些元件:

一个锁存器,两个三态输入缓冲器和一个输出驱动电路组成

在访问外部存储器时,P0是一个真正的双向口,当P0输出地址/数据信息时,CPU内部法控制电平“1”来打开上面的与门,又使模拟开关MUX把地址/数据信息经过反相器和T1接通(我们称上面的场效应晶体管FET为T1,下面的场效应管FET为T2);

输出的地址/数据信息既通过与门去驱动T1,又通过反相器去驱动T2,是两个FET构成推拉输出电路;

1.当P0口作为外部扩展存储器的数据地址总线时:

●若地址数据信息为“0”,那么这个信号就使得T1截止,使T2导通(经过反反相器作

用使得T2接收到的信号为“1”,根据场效应晶体管的特性,T2导通),若T2导通,那么T2的上下两个N极就导通,而发射极(下面的N极)接地信号则为“0”,这样P0口就相当于接收到了“0”信号;

●若地址数据信息输入“1”,则该信号使T2截止,使T1导通,在T1导通情况下,T1

的上下N极导通,使得VCC与P0相同,从而输出高电平,即“1”信号;

●若从P0口输入信号,信号从引脚通过输入缓冲器进入内部总线;

2.当P0口作为一般I/O口使用时:

●CPU内部发布控制信号“0”,封锁与门,使得T1截止,同时使模拟开关MUX把锁存

器的非Q端与T2端的栅极接通;

●在P0口作为输出时,由于非Q端和T2的倒相作用,那么内部总线上的信息与到达P0

口上的信息是同相的,只要写脉冲加到锁存器的CL端,内部总线上的信息就会P0的引脚上;

●但是由于此时T2为漏极开路输出,所以要外接上拉电阻。

当P0作为输入时,由于该信号既加到T2又加到下面的三态缓冲器。

现在我们假设我们刚刚输出的信号为“0”,也就是输入锁存器的数据为“0”,经过非Q达到T2使T2导通,这样P0引脚上的信号就被T2钳在“0”电平上,这样就使输入的“1”无法读入。

那么我们就必须在输入信号前,应该先向锁存器Q端写“1”,非Q就为“0”,使T2截止,这就是所谓的“准双向口”的解释。

但是在访问片外存储器时,CPU会自动向锁存器Q写入“1”,所以对用户而言P0口作为数据/地址总线时,是一个真正的双向口。