方波信号发生器设计

方波三角波发生器设计

方波三角波发生器设计设计思路:方波和三角波都是周期信号,因此我们可以使用周期信号发生器的原理来设计方波三角波发生器。

具体的设计思路如下:1.方波发生器设计:方波信号由高电平和低电平组成,所以我们需要设计一个产生高电平和低电平的电路。

可以使用一个三极管作为开关来实现方波的产生。

当输入信号为高电平时,三极管导通,输出高电平;当输入信号为低电平时,三极管截止,输出低电平。

2.三角波发生器设计:三角波信号是一个连续上升和下降的斜线信号,所以我们需要设计一个连续改变输出电压的电路。

可以使用一个集成电路比如操作放大器(OP-Amp)作为三角波发生器的核心组件。

使用一个电容和两个电阻来控制输出电压的上升和下降。

设计步骤:1.方波发生器设计:(1)选择一个适当的三极管,根据其参数确定电路中的电阻值。

(2)使用电阻和电源电压来确定三极管的偏置电压。

(3)将输入信号与三极管的基极相连。

(4)根据输入信号的高低电平改变三极管的导通和截止状态,从而实现方波的产生。

2.三角波发生器设计:(1)选择一个合适的操作放大器,根据其参数确定电路中的电阻值。

(2)使用电阻和电源电压来确定操作放大器的工作点。

(3)使用一个电容和两个电阻来控制操作放大器的输出电压的上升和下降。

(4)将操作放大器的输出电压与输入信号相连,并通过电容和电阻控制输出波形。

测试与调节:完成方波和三角波发生器的设计后,可以进行测试和调节,以确保输出信号的准确性和稳定性。

可以使用示波器来观察和测量输出波形,并通过调节电路中的电阻和电容来调节输出波形的频率和幅度。

此外,还可以根据需要进行性能优化和稳定性测试,以确保方波三角波发生器的正常工作。

总结:本文介绍了方波三角波发生器的设计思路和步骤。

方波三角波发生器的设计涉及了电路设计、参数选择、测试和调节等方面的知识,需要对电路原理和信号处理有一定的了解和掌握。

通过设计方波三角波发生器,我们可以产生方波和三角波信号,为实际应用提供了便利。

DSP课程设计——信号发生器(方波)

成绩评定表课程设计任务书目录1 绪论 (1)1.1 设计背景 (1)1.2 设计目的 (2)1.3 设计任务 (2)2 设计过程 (3)2.1 设计原理 (3)2.2 XF引脚周期性变化 (3)2.3 子程序的调用 (4)3 程序代码 (5)3.1 源程序 (5)3.2SDRAM初始化程序 (7)3.3 方波程序连接命令文件 (9)4 调试仿真运行结果分析 (10)4.1 寄存器仿真结果 (10)4.2 模拟输出仿真 (12)5.设计总结 (13)参考文献 (13)信号发生器(方波)1 绪论1.1 设计背景数字信号处理是20世纪60年代,随着信息学科和计算机学科的高速发展而迅速发展起来的一门新兴学科。

它的重要性日益在各个领域的应用中表现出来。

其主要标志是两项重大进展,即快速傅里叶变换(FFT)算法的提出和数字滤波器设计方法的完善。

数字信号处理是把信号用数字或符号表示成序列,通过计算机或通用(专用)信号处理设备,用数值计算方法进行各种处理,达到提取有用信息便于应用的目的。

例如:滤波、检测、变换、增强、估计、识别、参数提取、频谱分析等。

数字信号处理的目的是对真实世界的连续模拟信号进行测量或滤波。

因此在进行数字信号处理之前需要将信号从模拟域转换到数字域,这通常通过模数转换器实现。

而数字信号处理的输出经常也要变换到模拟域,这是通过数模转换器实现的。

数字信号处理的算法需要利用计算机或专用处理设备如数字信号处理器(DSP)和专用集成电路(ASIC)等。

数字信号处理的研究方向应该更加广泛、更加深入.特别是对于谱分析的本质研究,对于非平稳和非高斯随机信号的研究,对于多维信号处理的研究等,都具有广阔前景。

数字信号处理技术发展很快、应用很广、成果很多。

多数科学和工程中遇到的是模拟信号。

以前都是研究模拟信号处理的理论和实现。

模拟信号处理缺点:难以做到高精度,受环境影响较大,可靠性差,且不灵活等。

数字系统的优点:体积小、功耗低、精度高、可靠性高、灵活性大、易于大规模集成、可进行二维与多维处理。

555芯片设计占空比可调的方波信号发生器

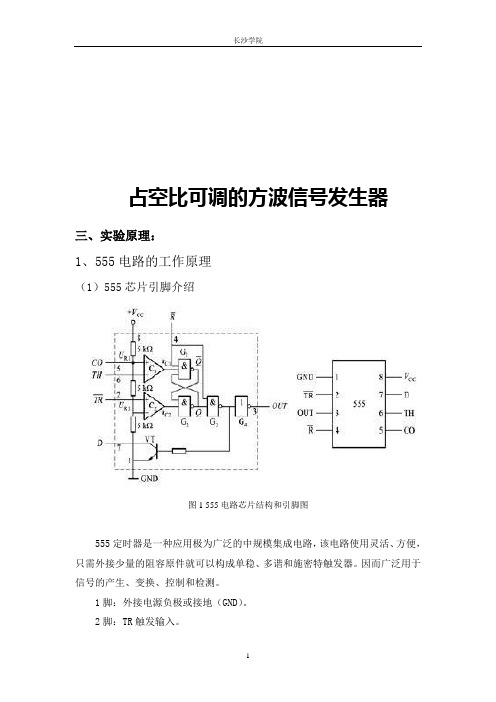

占空比可调的方波信号发生器三、实验原理:1、555电路的工作原理(1)555芯片引脚介绍图1 555电路芯片结构和引脚图555定时器是一种应用极为广泛的中规模集成电路,该电路使用灵活、方便,只需外接少量的阻容原件就可以构成单稳、多谐和施密特触发器。

因而广泛用于信号的产生、变换、控制和检测。

1脚:外接电源负极或接地(GND)。

2脚:TR触发输入。

3脚:输出端(OUT或Vo)。

4脚:RD复位端,移步清零且低电平有效,当接低电平时,不管TR、TH输入什么,电路总是输出“0”。

要想使电路正常工作,则4脚应与电源相连。

5脚:控制电压端CO(或VC)。

若此端外接电压,则可改变内部两个比较器的基准电压,当该端不用时,应将该端串入一只0.01μF 电容接地,以防引入干扰。

6脚:TH 高触发端(阈值输入)。

7脚:放电端。

8脚:外接电源VCC (VDD )。

(2)555功能介绍555定时器的功能主要是由两个比较器C1和C2的工作状况决定的。

由图1可知,当V6>VA 、V2>VB 时,比较器C1的输出VC1=0、比较器C2的输出VC2=1,基本RS 触发器被置0,TD 导通,同时VO 为低电平。

当V6<VA 、V2>VB 时,VC1=1、VC2=1,触发器的状态保持不变,因而TD 和输出的状态也维持不变。

当V6<VA 、V2<VB 时,VC1=1、VC2=0,故触发器被置1,VO 为高电平,同时TD 截止。

这样我们就得到了表1 555定时器的功能表。

2、占空比可调的方波信号发生器(1)占空比可调的方波信号发生器电路图放电管状态T D表1 555定时器的功能表输 入 <V A 阈值输入V 6 输 出触发输入V 2输出V O复位D R× 不变截止 导通 0 0 0 1 1 1 1× >V A <V A<V B >V B >V B不变导通图2 利用555定时器设计方波电路原理图(2)占空比可调的方波信号发生器分析如图2所示,电路只要一加上电压VDD ,振荡器便起振。

(完整)两路相位可调方波信号发生器(最终版)

目录1、设计原理与方法 (2)1.1、单片机系统概述 (2)1.2、80C51内部结构与引脚说明 (2)1.3、设计原理 (4)2、系统硬件线路设计图 (6)3、程序框图 (7)4、资源分配表 (8)5、源程序 (8)6、仿真结果 (12)7、性能分析 (14)8、总结与心得 (15)9、参考文献 (16)1、设计原理与方法1。

1、单片机系统概述单片机也被称为微控制器(Microcontroller Unit),常用英文字母的缩写MCU表示单片机,它最早是被用在工业控制领域。

单片机由芯片内仅有CPU的专用处理器发展而来。

最早的设计理念是通过将大量外围设备和CPU集成在一个芯片中,使计算机系统更小,更容易集成进复杂的而对体积要求严格的控制设备当中。

INTEL的Z80是最早按照这种思想设计出的处理器,从此以后,单片机和专用处理器的发展便分道扬镳。

单片机比专用处理器更适合应用于嵌入式系统,因此它得到了最多的应用。

事实上单片机是世界上数量最多的计算机.现代人类生活中所用的几乎每件电子和机械产品中都会集成有单片机。

手机、电话、计算器、家用电器、电子玩具、掌上电脑以及鼠标等电脑配件中都配有1—2部单片机。

而个人电脑中也会有为数不少的单片机在工作.汽车上一般配备40多部单片机,复杂的工业控制系统上甚至可能有数百台单片机在同时工作!单片机的数量不仅远超过PC机和其他计算的总和,甚至比人类的数量还要多. 单片机又称单片微控制器,它不是完成某一个逻辑功能的芯片,而是把一个计算机系统集成到一个芯片上.相当于一个微型的计算机,和计算机相比,单片机只缺少了I/O设备。

概括的讲:一块芯片就成了一台计算机。

它的体积小、质量轻、价格便宜、为学习、应用和开发提供了便利条件。

同时,学习使用单片机是了解计算机原理与结构的最佳选择。

1。

2、80C51内部结构与引脚说明8051的CPU包含以下功能部件:(1)8位CPU。

(2)布尔代数处理器,具有位寻址能力。

频率可调的方波信号发生器

由32号、17号、27号制作

目录目录目录

一、课程设计总体流程 二、课程设计目的

三、硬件设计

四、软件设计

五、总结

设计的总体流程及

设计的目的和功能

设计目的:设计一种频率范围限定且使蜂鸣器 产生不同频率的声音,方波信号可通过 示波器显示出来,用Proteus仿真软件来 模拟显示方波。

三、硬件设计

3.1最小系统电路图设计

最小系统包括复位电路和晶振发生电路如图:

三、硬件设计

3.2按键电路设计

按键电路采用独立键盘设计如图:

三、硬件设计

3.3 蜂鸣器电路设计

三、硬件设计

3.4数码管驱动显示电路 采用四位数码管,故需要驱动电路,这里用mc74h573 芯片来驱动,具体电路设计如图

取反输出方波

第三次按下,设 初值2khz

……

第十次按下, 设初值6khz

四、软件设计

4.2按键检测流程图

四、软件设计

4.3数码管显示流程图

五、总结

经过制作设计的这段时间的努力终于将本设计方案要求基 本实现。由于时间、水平和经验有限,设计的作品还存在着

一些的不足之处。

对于这次设计来说既是一次机遇,又是一次挑战。在这次 的设计过程中,本人学到了很多东西,通过自己的实践,增 强了动手能力。通过实际工程的设计也使我了解到书本知识 和实际应用的差别。在实际应用中遇到很多的问题,这都需

要我对问题进行具体的分析,并一步一步地去解决它。

四、软件设计

4.1软件设计基本思想及程序框图

软件设计基本思想: 2个按键开关次数判断,1个七段四位数码管的动态显示,方波发生器方波 的输出(仿真调试),蜂鸣器放映方波频率改变

方波信号发生器

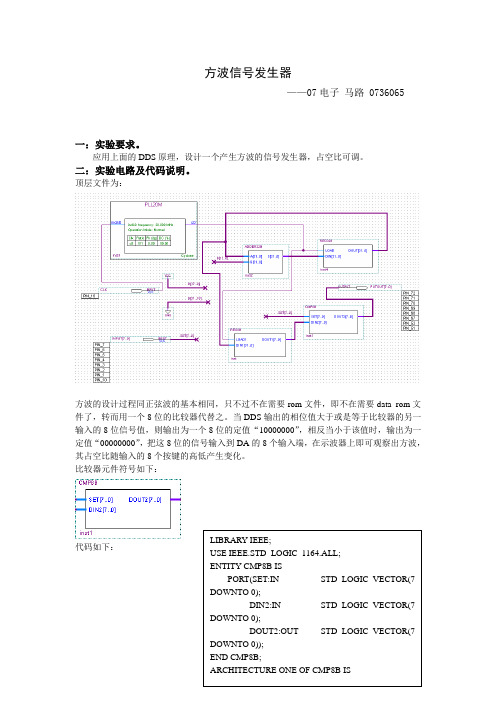

方波信号发生器——07电子马路 0736065一:实验要求。

应用上面的DDS原理,设计一个产生方波的信号发生器,占空比可调。

二:实验电路及代码说明。

顶层文件为:方波的设计过程同正弦波的基本相同,只不过不在需要rom文件,即不在需要data_rom文件了,转而用一个8位的比较器代替之。

当DDS输出的相位值大于或是等于比较器的另一输入的8位信号值,则输出为一个8位的定值“10000000”,相反当小于该值时,输出为一定值“00000000”,把这8位的信号输入到DA的8个输入端,在示波器上即可观察出方波,其占空比随输入的8个按键的高低产生变化。

比较器元件符号如下:代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CMP8B ISPORT(SET:IN STD_LOGIC_VECTOR(7 DOWNTO 0);DIN2:IN STD_LOGIC_VECTOR(7 DOWNTO 0);DOUT2:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END CMP8B;ARCHITECTURE ONE OF CMP8B IS为了便于观察方波的变化,这里把DDS 设置为固定频率,即相位输出为定值。

32位的高位:31~18位全零,低位:17~0位为全1。

占空比通过SET[7..0]信号调节。

时钟信号clk 用的是FPGA 芯片上的固有频率20M 。

三:仿真。

仿真时,为了提高仿真的效率,可以不加锁相环。

如下:仿真波形设置:仿真后的波形:BEGIN PROCESS(SET,DIN2) BEGIN IF DIN2>SET THEN DOUT2<="10000000"; ELSIF DIN2=SET THEN DOUT2<="10000000"; ELSE DOUT2<="00000000"; END IF; END PROCESS; END ONE;由仿真结果可知,产生了方波。

设计能产生方波、三角波、正弦波的函数信号发生器电路

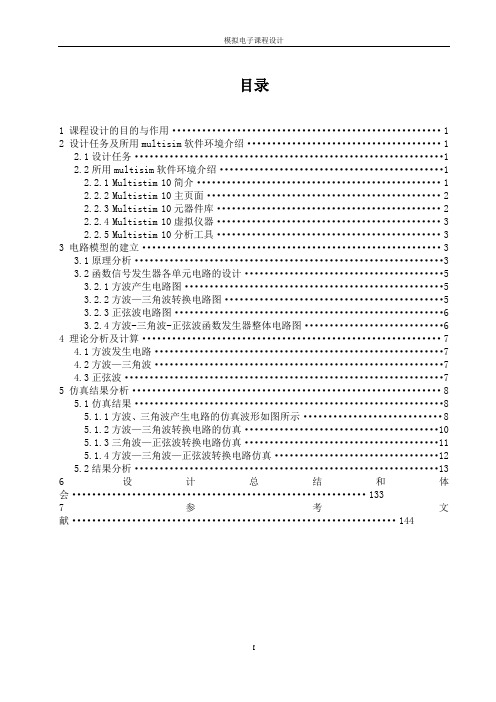

目录1 课程设计的目的与作用 (1)2 设计任务及所用multisim软件环境介绍 (1)2.1设计任务 (1)2.2所用multisim软件环境介绍 (1)2.2.1 Multistim 10简介 (1)2.2.2 Multistim 10主页面 (2)2.2.3 Multistim 10元器件库 (2)2.2.4 Multistim 10虚拟仪器 (3)2.2.5 Multistim 10分析工具 (3)3 电路模型的建立 (3)3.1原理分析 (3)3.2函数信号发生器各单元电路的设计 (5)3.2.1方波产生电路图 (5)3.2.2方波—三角波转换电路图 (5)3.2.3正弦波电路图 (6)3.2.4方波-三角波-正弦波函数发生器整体电路图 (6)4 理论分析及计算 (7)4.1方波发生电路 (7)4.2方波—三角波 (7)4.3正弦波 (7)5 仿真结果分析 (8)5.1仿真结果 (8)5.1.1方波、三角波产生电路的仿真波形如图所示 (8)5.1.2方波—三角波转换电路的仿真 (10)5.1.3三角波—正弦波转换电路仿真 (11)5.1.4方波—三角波—正弦波转换电路仿真 (12)5.2结果分析 (13)6 设计总结和体会 (133)7 参考文献 (144)I1 课程设计的目的与作用1.巩固和加深对电子电路基本知识的理解,提高综合运用本课程所学知识的能力。

2.培养根据课题需要选学参考书籍,查阅手册、图表和文献资料的自学能力。

通过独立思考,深入钻研有关问题,学会自己分析并解决问题的方法。

3.通过电路方案的分析、论证和比较,设计计算和选取元器件;初步掌握简单实用电路的分析方法和工程设计方法。

4.了解与课题有关的电子电路以及元器件的工程技术规范,能按设计任务书的要求,完成设计任务,编写设计说明书,正确地反映设计与实验的成果,正确地绘制电路图等。

5.培养严肃、认真的工作作风和科学态度2 设计任务及所用multisim软件环境介绍2.1 设计任务设计能产生方波、三角波、正弦波的函数信号发生器电路1)输出各种波形工作频率范围:10—100Hz,100—1KHz,1K—10KHz。

信号发生器设计(正弦,方波,三角,多用信号发生器)

模拟电路课程设计报告设计课题:信号发生器设计班级:10通信工程三班学生姓名:陶冬波学号:2010550921指导教师:设计时间:目录一、信号发生器摘要--------------------3二、设计目的---------------------3三、设计内容和要求四、设计方案------------------------------------------34.1 RC桥式正弦波产生电路--------------------------------------3 4.2方波产生电路----------------------------------------------------6 4.3三角波产生电路-------------------------------------------------84.4多用信号发生器-------------------------------------------------9五、组装调试及元件清单---------------------------105.1 测试仪器---------------------------------------------------------10 5.2信号发生器元件清单-----------------------------------------------115.3调试中出现的故障、原因及排除方法----------------------11六、总结设计电路,改进措施----------------------116.1 正弦波产生电路改进措施--------------------------------------116.2多用信号发生器改进措施---------------------------------------11七、收获和体会-----------------------------------------12八、参考文献--------------------------------------------12信号发生器设计一、信号发生器设计摘要:本设计介绍了波形发生器的制作和设计过程,并根据输出波形特性研究该电路的可行性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

方波信号发生器设计

一.实验目的:

1.进一步熟悉QuartusII及其LPM_ROM与FPGA硬件资源的使用方法。

2.加深对电路理论概念的理解

3.进一步熟悉常用仪器的使用及调试

4.加深计算机辅助分析及设计的概念

5.了解及初步掌握对电路进行计算机辅助分析的过程

6.培养学生发现问题、分析问题的创新能力

7.锻炼学生搜集资料、分析综合资料的能力

二.实验原理:

方波波信号发生器由四部分组成:

计数器或地址发生器(这里选择6位)。

方波信号数据ROM(6位地址线、8位数据线),含有64个8位数据(一个周期)。

VHDL顶层设计。

8位D/A(实验中用DAC0832代替)。

图1所示的信号发生器结构框图中,顶层文件singt.vhd在FPGA中实现,包含两个部分:ROM的地址信号发生器,由6位计数器担任;一个方波数据ROM,由LPM_ROM模块构成。

LPM_ROM底层是FPGA中的EAB、ESB或M4K等模块。

地址发生器的时钟CLK的输入频率f0与每周期的波形数据点数(在此选择64点),以及D/A输出的频率f的关系是:f = f0/64。

图1 方波信号发生器结构框图

三.实验内容:

1.新建一个文件夹。

利用资源管理器,新建一个文件夹,如:e : \SIN_GNT 。

注意,文件夹

名不能用中文。

2.输入源程序。

打开QuartusII,选择菜单“File”“New”,在New 窗中的“Device Design Files”

中选择编译文件的语言类型,这里选“VHDL Files”。

然后在VHDL 文本编译窗中键入VHDL 程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity square is

port(clk,clr:in std_logic;

q:out integer range 0 to 255

);

end entity;

architecture behav of square is

signal a:bit;

begin

process(clk,clr) --计数分频

variable cnt:integer range 0 to 32; begin

if(clr='0') then

a<='0';

elsif clk'event and clk='1' then

if cnt<31 then --进行32分频

cnt:=cnt+1;

else

cnt:=0;

a<=not a;

end if;

end if;

end process;

process(clk,a) --信号输出

begin

if clk'event and clk='1' then

if a='1' then

q<=255;

else

q<=0;

end if;

end if;

end process;

end behav;

3. 建立.mif格式文件

首先选择ROM 数据文件编辑窗,即在File 菜单中选择“New”,并在New 窗中选择“Other files”项,并“Memory Initialization File”(图3-11),点击OK 后产生ROM 数据文件大小选择窗。

这里采用64 点8位数据的情况,可选ROM 的数据数Number 为64,数据宽Word size 取8 位。

点击“OK”,将出现空的mif数据表格,表格中的数据为10 进制表达方式,任一数据(如第三行的99)对应的地址为左列于顶行数之和。

将波形数据填入此表中,完成后在File 菜单中点击“Save as”,保存此数据文件,在这里不妨取名为romd.mif

4.定制ROM元件

利用Mega Wizard Plug-In Manager 定制方波数据ROM 步骤如下:

设置Mega Wizard Plug-In Manager 初始对话框。

在Tools 菜单中选择“Mega Wizard Plug-In Manager”,产生图3-14的界面,选择“Create a new custom…”项,即定制一个新的模块。

点击“Next”后,产生图3-15 对话框,在左栏选择“Storage”项下的LPM_ROM,再选“Cyclone”器件和VHDL 语言方式,最后键入ROM 文件存放的路径和文件名,点击“Next”。

5.创建.bdf文件,连接引脚,如图:

6.编译

7.仿真

(1)打开波形编辑器。

选择菜单File 中的New 项,在New 窗中选“Other Files”中的“Vector Waveform File”,点击OK,即出现空白的波形编辑器(图3-21)。

(2)设置仿真时间区域。

为了使仿真时间轴设置在一个合理的时间区域上,在Edit 菜单中选择“End Time”项,在弹出的窗中的“Time”窗中键入100,单位选“ms”,即整个仿真域的时间即设定为100毫秒,点击OK,结束设置。

(3)存盘波形文件。

选择File 中的“Save as”。

(4)编辑输入波形(输入激励信号)。

点击时钟名CLK,使之变兰色,再点击左列的时钟设置键,在Clock 窗中设置CLK 的周期为10ns(图3-22);所示的Clock 窗中的“Duty

cycle”是占空比,可选50,即50%占空比,再对文件存盘

(5)编译仿真波形如图:

四.实验体会:

通过实验,激发了我们学习EDA的兴趣,也对这门课程有了更深的理解,对EDA 设计软件Quarter Ⅱ的使用也更加熟练。

在老师给我们的材料中,我们分析了方波信号发生器在整个运行过程中的状态,并参考资料写出了状态图,然后根据状态图用有限状态机来实现了各个状态之间的转换,进而实现了产生方波信号。

我想我们对EDA的学习只能算是个入门,这个领域的发展空间非常大,应用范围也非常广泛,而且我相信在将来还会有更加广阔的应用前景。

因此在以后的学习过程中,我们不能因为课程学习的结束而结束了对这个领域的探索,相反我们应更加努力的去学习它。

感谢老师孜孜不倦的教诲,让我们不仅学到了知识,也学到了做人做事的一些道理,为我们提供了很多帮助。

在接下来的学习生涯中,我们会继续努力,努力扎实地学习专业知识,实现自己的理想。