信号波形合成实验

第五组--信号波形合成电路实验(2010年电子竞赛C题论文)2

高,在高压、高频、大功率的场合不适用。 综合以上的分析,由 TI 公司生产的宽带低失真单位增益稳定的电压反馈运算放

大器 OPA842 组成的滤波电路满足本次设计的要求,因此选择方案二。 1.1.3 移相电路

方案一:用双极性运算放大器 OP07 组成的移相电路,由于 OP07 具有非常低的 输入失调电压,所以在很多应用场合不需要额外的调零措施。OP07 是一种低噪声, 非斩波稳零的双极性运算放大器,由它组成的移相电路具有电路简单、工作可靠、成 本低、波形好、适应性强,而且可以提供 180°的相移。

表一:信号编码表

A0

A1

X

1

0

0

1

0

波形 正弦波 方波 三角波

A0、A1 表示波形设定端;X 表示任意状态;1 为高电平;0 为低电平。 74LS14 非门对输出的信号进行整形,使输出的波形更加的理想。 3.1.2 分频电路 分频电路如附录图 3 所示,由 74LS90、74LS00、CD4013 三片芯片组成。先将 300KHz 的方波信号进行 3 分频、5 分频、15 分频,再通过 D 触发器二分频,最终得到 50KHz、 30KHz、10KHz 的正弦波信号。 74LS90 不仅可以用于计数,还能用于分频,一片 74LS90 可构成最大进制计数器 是十进制,若分频数大于 10,则要用两片或多片级联,级联后高位的周期即为分频 后的周期,但占空比并非 50%,这就需要用 D 触发器对分频后的方波进行整形。74LS00 是四集成与非门,在电路中起缓冲隔离的作用。CD4013 是由两个相同的、相互独立 的数据型触发器构成。每个触发器有独立的数据、置位、复位、时钟输入和 Q 及 Q

方案三:用 MAX038 精密、高频波形发生器来产生方波信号,电路结构简单,能产 生 0.1Hz~20MHz 的方波信号,波形的频率和占空比可以由电流、电压或电阻控制 。 MAX038 构成的电路低失真、低漂移、外围元件少、可靠性和稳定性好,但相对于上 面的方案而言,价格会稍高一点。

信号波形合成实验电路

信号波形合成实验电路摘要:本设计通过ICL8038产生300K方波信号,再通过计数器CD4518及74LS161与D 触发器分频成多个不同频率的方波信号,并将这些信号经过巴特沃斯低通滤波器、反相比例运放电路、 型滤波电路、跟随器,将其转换为10K、30K、50K正弦信号,再经RC移相电路之后,利用同相输入求和加法器将峰峰值分别为6V、2V、1.2V的正弦波合成为近似方波及其他信号。

Abstract:This design can produce 300KHz square-wave signals by ICL8038, then spilt frequency through CD4518 counter with D flip-flop 74LS161 , and will put these signals through butterworth low-pass filter, opposite proportion amp circuit, filter circuit and follower circuit,and will produce 10KHz,30KHz and 50KHz sine signals, then by using RC phase-shifting circuit with these signals and same-phase sum adder,it can compound 6V、2V、1.2V sine signals to produce approximate sine signals and other signals.一、系统方案与论证1.1高频方波产生电路的比较方案一:采用555定时器,555 定时器成本低,性能可靠,只需要外接几个电阻、电容就可以产生方波。

缺点是本电路需要产生高频方波,而用555定时器产生的高频方波不稳定。

方案二:采用ICL8038精密压控函数发生器,ICL8038是一种具有多种波形输出的精密振荡集成电路,只需要个别的外部元件就能产生从0.001Hz~1M Hz的正弦波、三角波、矩形波等脉冲信号。

信号的分解与合成

实验十三 信号分解及合成一、 实验目的1、 了解和熟悉波形分解与合成原理。

2、 了解和掌握用傅里叶级数进行谐波分析的方法。

二、 实验仪器1、 双踪示波器2、 数字万用表3、 信号源及频率计模块S24、 数字信号处理模块S4三、 实验原理(一)信号的频谱与测量信号的时域特性和频域特性是对信号的两种不同的描述方式。

对于一个时域的周期信号()f t ,只要满足狄利克菜(Dirichlet)条件,就可以将其展开成三角形式或指数形式的傅里叶级数。

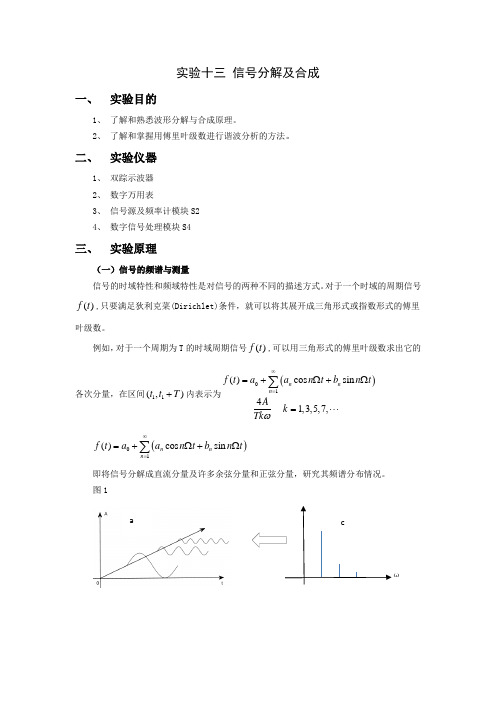

例如,对于一个周期为T 的时域周期信号()f t ,可以用三角形式的傅里叶级数求出它的各次分量,在区间11(,)t t T +内表示为()01()cos sin 41,3,5,7,n n n f t a a n t b n t Ak Tk ω∞==+Ω+Ω=⋅⋅⋅∑()01()cos sin n n n f t a a n t b n t ∞==+Ω+Ω∑即将信号分解成直流分量及许多余弦分量和正弦分量,研究其频谱分布情况。

图1ωca信号的时域特性和频域特性信号的时域特性与频域特性之间有着密切的内在联系,这种联系可以用图13-1来形象地表示。

其中图(a)是信号在幅度—时间—频率三维坐标系统中的图形;图(b)是信号在幅度一时间坐标系统中的图形即波形图:把周期信号分解得到的各次谐波分量按频率的高低排列,就可以得到频谱图。

反映各频率分量幅度的频谱称为振幅频谱。

图(c)是信号在幅度—频率坐标系统中的图形即振幅频谱图。

反映各分量相位的频谱称为相位频谱。

在本实验中只研究信号振幅频谱。

周期信号的振幅频谱有三个性质:离散性、谐波性、收敛性。

测量时利用了这些性质。

从振幅频谱图上,可以直观地看出各频率分量所占的比重。

测量方法有同时分析法和顺序分析法。

同时分析法的基本工作原理是利用多个滤波器,把它们的中心频率分别调到被测信号的各个频率分量上。

当被测信号同时加到所有滤波器上,中心频率与信号所包含的某次谐波分景频率-致的滤波器便有输出。

信号波形合成实验电路的设计与制作

图 7 峰 值 检 波 电路

【 3 】 MSP 4 3 O x 1 x x F a m I v Us e r 。 s Gu i d e E r r a t a , T e x a s I n s t —

r u me n t s . US A.

幅值检 测显 示 电路

2 9 7

1所 示 。

表 ) 实际频 率( H )峰 峰值 ( V) 测量值( V) 测量误差

图 6 加 法 电路

参考文献 :

【 1 慷 华光. 《 电子技术基础——模 拟部分》 , 高等教育出版社 , 2 0 0 6

1.

【 2 ] SL AUO 4 9 D, MSP 4 3 0 x1 x x F a mj l v Us e r ‘ s Gu i d e , T e x a s I n s t —

图 5 移 相 电 路

移 相 电路如 图 5所 示 , 由两 级 运放 组 成 , 本 设计 中采 用L F 3 5 3, 第一 级运 放 与 C1 7 、 R 2 3构 成 有源微 分网络 , 第 图8 MS P 4 3 0 F 1 4 9幅 值测 量 显 示 电路 二级 运放 与 R 2 4 、 C 1 9组 成有 源积 分 网络。 当输 入正 弦 交 其 中 MS P 4 3 0 F 1 4 9是 T I 公司 1 6位 超 低 功 耗 单 片 流信 号 时 , 第 一 级 运放 输 出超 前 相 位信 号 , 第 二级 运 放输 机。由 2个 1 6位定 时器 、 8路 快速 1 2位 A / D 转换器 、 2个 出一 滞 后相 位信 号 ,通过 调 节 R 2 4可 使输 出信 号 与 输入 通用 串行 同步 / 异步 通信 信 号 接 口和 1 8个 I / O 引脚 等构 信 号相 位 发生 变化 。 成 的微 控 制器 。 其特 点是 电源 电压 范 围为 1 . 8 V 一 3 . 6 V , 超低 加 法 电路 功耗 , 内部 集成 看 门狗定 时器 。 加 法 电路 如 图 6所 示 ,本 设计 采 用 同相 输 入 加 法 电 通过 F 1 4 9单 片 机 的 P 1 . 0 、 P 1 . 1和 P 1 . 2口分 别进 行 路。输出 U 。 = ( 1 + R 2 5 , R 2 7 ) ( U1 + U 2 + U 3 】 。当 R 2 5 = R 2 7 时, U 。 = 2 AD采样 ,得 到 1 O K H Z 、 3 0 K H Z和 5 0 K H Z正 弦波 的幅值 , ( U + U 2 + U 。 ) , 此时 实现输 入信 号 叠加 。 通 过 按键 S W1 、 S W2 、 S W 3切 换 在 1 2 8 6 4液 晶 上 显 示 各 自峰值。 2 测试 结果 在 测试 阶段 , 我 们 对得 到 的正 弦波 进 行 了频 率 、 峰 峰 值 的测 量并计 算 了峰峰值 测 量误差 。 测试 得 到 的数 据如 表

方波信号合成电路

摘要:信号波形合成实验电路主要由120KHz的方波发生电路、分频电路、滤波电路、调理电路、加法电路等模块组成。

120KHz的方波信号通过30分频、10分频、6分频产生4KHz、12KHz、20KHz的方波信号。

经滤波电路和调理电路得到正弦波信号,通过加法电路将信号合成近似方波信号。

关键词:信号波形合成;30分频;10分频;6分频一、方案比较与论证(一)、项目总体方案分析(二)1.方波信号产生电路方案一:用555定时器接成的多谐振荡器,能使产生的方波占空比可调,即高电平持续时间与低电平持续时间的比值可调;占空比10%~90%。

产生频率约为1.5KHZ的矩形波,矩形的电压峰峰值为电源电压+5V。

该频率难达到150KHz。

方案二:用TLC083芯片,它是一种迟滞比较器,具有开环特性,压摆率可达到19V/us,带宽10MHz。

通过以上比较分析,我们选用方案二。

2.分频器:方案一:采用可编程逻辑控制器方案二:采用74LS161对120KHZ的方波信号进行分频可得占空比为50%的12K.20KHZ的信号,它的电路构成比较简单,成本较低3.滤波电路方案一:采用RC滤波电路,由于电阻R与频率变化无关,RC低通滤波器在器件选材方面要简单,但不适合大功率输出,仅可作为弱信号处理与微小功率应用。

方案二:采用TLC04芯片,四阶低通滤波器。

TLC04的截止频率的稳定性只与时钟频率稳定性相关,截止频率时钟可调,其时钟一截止频率比为50:1,因而设计截止频率为1/1.69×RF1×CF1×50=251.8Hz,满足了振动时效和振动焊接工艺的要求。

通过以上方案比较,我们选用方案二。

4.调整电路方案一:同相比例运算电路,它是深度电压串联负反馈电路,调节反馈电阻和反相输入电阻比值可调节比例系数,且比例系数大于或等于一方案二:反相比例运算电路,它是深度电压并联负反馈电路,可作为反相放大器,调节反馈电阻和反相输入电阻比值即可调节比例系数,比例系数既可大于一也可小于一,但它不可去处直流分量方案三:在反相比例运算电路的基础上将反相比例运算电路的正向输入端电阻改成可调电阻,并在可调电阻的另两端接上+、-5V 。

【原创】信号波形合成实验电路

信号波形合成实验电路摘要:本文介绍了一个信号波形合成的电路方案。

该电路能产生多个不同频率的正弦信号,并将这些信号再合成为近似方波和三角波。

该电路用运放构成的迟滞比较器并结合RC震荡电路产生了方波,产生的方波再经滤波电路进行分频产生出不同频率的正弦波,这些不同频率的正弦波经移相电路形成不同相位的正弦波,再经由运放构成的加法器电路最终产生合成信号。

此外,该电路还以LM3s811为主控制器对产生的信号的幅度和频率进行测量和数字显示。

所有指标都达到题目要求。

关键词:方波电路分频与滤波移相电路加法器电路Abstract:This article describes a signal waveform synthesis circuit scheme. The circuit can produce several different frequency sinusoidal signal, and these signals and then to an approximate square wave synthesis and other signals. The circuit amplifier consisting of comparator with hysteresis RC oscillation circuit produced a square wave, square wave generated by the filter circuit for frequency division produces different frequency sine wave, these different frequency sine wave and then via the formation phase-shift circuit different phase sine wave, then through the amplifier consisting of Adder the resulting composite signal. In addition, this circuit is also the main controller LM3s811 circuit on the amplitude of the signal measurement and digital display. All indicators have reached the required title.Key words::The shock wave circuit, frequency division and filtration, phase-shifting circuit, adder circuit一、作品简介根据题目要求,此波形发生器的设计主要包括四个部分:方波振荡电路、分频与滤波电路、移相电路、加法器电路。

信号波形合成

课程设计报告设计课题:信号波形合成实验专业班级:学生姓名:指导教师:设计时间:目录一、课程设计目的 (1)二、课程设计题目描述和要求 (1)1.基本要求 (1)2.发挥部分 (2)三、系统分析与设计 (2)1、方案设计 (2)方波振荡部分 (2)分频部分 (2)滤波部分 (2)移相、放大部分 (3)波形合成部分 (3)2、硬件实现 (3)方波振荡器 (3)分频器 (4)滤波器 (5)移向、放大器 (5)波形合成器 (6)四、系统调试过程中出现的主要问题 (7)五、系统运行报告与结论 (7)六、总结 (9)七、参考书目 (9)八、附录 (10)信号波形合成实验一、课程设计目的设计制作一个电路,能够产生多个不同频率的正弦信号,并将这些信号再合成为近似方波和其他信号。

电路示意图如图1所示:图1 电路示意图二、课程设计题目描述和要求1.基本要求(1)方波振荡器的信号经分频与滤波处理,同时产生频率为10kHz和30kHz 的正弦波信号,这两种信号应具有确定的相位关系;(2)产生的信号波形无明显失真,幅度峰峰值分别为6V和2V;(3)制作一个由移相器和加法器构成的信号合成电路,将产生的10kHz和30kHz正弦波信号,作为基波和3次谐波,合成一个近似方波,波形幅度为5V,合成波形的形状如图2所示。

图2 利用基波和3次谐波合成的近似方波2.发挥部分(1)再产生50kHz的正弦信号作为5次谐波,参与信号合成,使合成的波形更接近于方波;(2)根据三角波谐波的组成关系,设计一个新的信号合成电路,将产生的10kHz、30kHz等各个正弦信号,合成一个近似的三角波形;(3)其他。

三、系统分析与设计1、方案设计方波振荡部分方波振荡电路采用555定时器组成多谐振荡器,调节至300kHz 左右方波,由于之后的分频电路具有调节占空比功能,所以方波产生电路暂时不需要调节占空比。

分频部分分频部分实现将产生的方波通过分频产生10kHz 、30kHz 和50kHz 的新的方波。

8信号波形合成实验电路

简易波形合成电路的设计与实现李灿,王成跃,杨卫南京医科大学生物医学工程系,南京210029摘要本文主要设计一个能够合成指定波形的信号波形发生电路,该电路基于傅里叶合成,能够产生不同频率的正弦信号,将这些信号处理后送入加法电路可合成所需信号,主要由方波产生模块产生方波,分频与滤波模块对所得方波分频并滤成正弦波,放大模块对所得正弦波幅值进行放大,移相模块调整各频率正弦波相位,信号合成模块合成所需波形。

关键词:波形合成;分频滤波;移相The Design and Implementation of Simple Waveform Synthesis Circuit Li Can, WangChengyue, Yang Wei,Zhu Songsheng,Wang Wei*Department ofBiomedical Engineering, NanjingMedicalUniversity,Nanjing210029,China Abstract This paper mainly designs a signal waveform generating circuit that can synthesize designated waveform.Based on Fourier, it can produce various frequency sine signals. After processing, these sine signals can be synthesized designatedsignal through addition circuit. Among the circuit,the square wavegenerating module produces square-wave, and thesquare-wave is divided frequency and filtered into sine wave though frequency separating and filtering modules. After that, the amplifier module magnify the amplitude of the sine wave obtained. Then p hase shifting module adjusts the amplification of each frequency sine wave. Finally the signal waveform synthesis module synthesizes designated waveform with processed sine waves. Keywords waveform synthesis,frequency separating and filtering, phase shifting filter display1引言在电子测仪器中.信号发生器有着非常重要的地位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

信号波形合成实验电路实验报告组员:于兴家、俞宝智、黄艳霞指导教师:赵娟老师目录一、系统设计................................................................ . (2)1、设计任务 (2)2、基本要求 (2)3、发挥部分 (2)二、方案论证 (3)1、信号发生器电路 (4)2、分频电路 (4)3、滤波电路 (4)4、移相电路.............. . (4)5、加法电路 (5)三、整体设计 (5)原理图:整体方案设计 (5)1、方波发生器的设计与实现 (5)2、分频电路的设计与实现 (5)3、电压跟随器 (6)4、滤波电路的设计与实现 (7)5、移向电路的设计与实现 (7)6、合成电路的设计与实现 (8)7、合成电路的设计与实现 (9)四. 实验测试与结果分析 (10)1、测试仪器与设备 (10)2、整机标准 (10)3、系统试验结果与分析 (10)五、实物图片 (10)一、系统设计1、任务设计制作一个电路,能够产生多个不同频率的正弦信号,并将这些信号再合成为近似方波和其他信号。

电路示意图如图1所示:图1 电路示意图2、要求1.基本要求(1)方波振荡器的信号经分频与滤波处理,同时产生频率为10kHz和30kHz的正弦波信号,这两种信号应具有确定的相位关系;(2)产生的信号波形无明显失真,幅度峰峰值分别为6V和2V;(3)制作一个由移相器和加法器构成的信号合成电路,将产生的10kHz和30kHz正弦波信号,作为基波和3次谐波,合成一个近似方波,波形幅度为5V,合成波形的形状如图2所示。

图2 利用基波和3次谐波合成的近似方波2.发挥部分(1)再产生50kHz的正弦信号作为5次谐波,参与信号合成,使合成的波形更接近于方波;(2)根据三角波谐波的组成关系,设计一个新的信号合成电路,将产生的10kHz、30kHz等各个正弦信号,合成一个近似的三角波形;(3)设计制作一个能对各个正弦信号的幅度进行测量和数字显示的电路,测量误差不大于±5%;(4)其他。

二、系统方案论证1.1 方波发生电路方案方案一:采用分立元件实现非稳态的多谐振振荡器,然后根据需要加入积分电路等构成正弦、矩形、三角等波形发生器。

这种信号发生器输出频率范围窄,而且电路参数设定较繁琐,相位也不一致,其频率大小的测量往往需要通过硬件电路的切换来实现,操作不方便。

方案二:采用555振荡电路或函数信号发生器ICL8038集成模拟芯片,它是一种可以同时产生方波、三角波、正弦波的专用集成电路。

波形的频率可以通过调节555定时器电路的外接滑动变阻器来进行调节。

该电路具有成本低廉,频率可调,电路灵活方便,结构简单,低功耗,输入阻抗高,上升沿陡等的特点,不用依靠单片机。

但是经试验验证,555振荡产生的失真较大,所以放弃此方案。

方案三:由UA741集成运算放大器构成的方波信号发生器具有结构简单,调试方便,但它产生方波信号的可靠性差,易失真,稳定性差。

方案四:由CD4046芯片(CMOS锁相环电路)具有电源电压范围宽(3v至18v),输入阻抗高(为100M欧姆),动态功耗小,属微功耗器件等特点,构成的方波信号发生器,根据所接改变阻值大小即可改变方波输出范围。

故采用此种方案,方便简单。

由CD4046构成的方波发生器方案五:采用二级非门与晶振组合成形成正反馈电路产生正反振荡,其中采用的 6MHZ 的晶振是起滤波作用。

只有 6MHZ 频率的脉冲信号容易通过该正反馈电路,其它频率的信号被抑制。

故电路表现为只有 6MHZ 的方波信号。

该电路输出稳定,容易搭建。

1.2 分频电路设计方案方案一:利用数字电路设计分频电路。

通过计数器计数来实现,由待分频的时钟边沿触发集成计数器计数,当计数器到规定值时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去。

这种方法可以实现任意的整数分频电路,因操作方便,原理简单,选择方案一作为系统的分频方案。

此次试验采用的为74LS161芯片。

方案二:使用编程方法实现分频电路。

其原理与利用集成计数器相同,实现起来也十分简单,但分频得到的时钟可能会出现毛刺或不稳定的因素,适用于时钟要求不高的基本设计,且对于整数分频可以很容易地用计数器来实现,故不采用此方案。

方案三:采用CD4017(5位johnson计数器)与CD4013进行计数,计数器在时钟上升时进行计数。

1.3 滤波电路设计方案由分频电路产生的单极性方波需要经过窄带通滤波电路形成正弦波。

其带通的范围很窄,要与各次谐波的频率接近。

方案一:使用由LC网络组成的无源高阶巴特沃斯滤波器。

其通带内相应最为平坦,衰减特性和相位特性都很好,对器件的要求也不高。

但其在低频范围内有体积重量大,价格昂贵和衰减大等缺点。

方案二:采用实时DSP数字滤波技术,数字信号灵活性大,可以在不增加硬件成本的基础上对信号进行有效的滤波,但要进行滤波,需要A/D、D/A既有较高的转换速率,处理器具有较高的运算速度,成本高。

方案三:以集成运放LM318为核心的有源滤波电路,结构简单,所需元件少,成本低,且电路输入阻抗高、输出阻抗低,但需要有专门的设计软件,所以不选择此方案。

方案四:运用RC滤波电路与同相比例放大电路构成的有源低通滤波器构成10k频率、30k频率的滤波。

采用由RC滤波器与同相比例放大电路组成的低通滤波器与高通滤波器构成的有源带通滤波器构成50k频率滤波。

因操作简单,所用元件简单容易获得,故采用此种方法。

1.4 移相电路设计方案方案一:利用RC移相电路。

RC移相电路主要是由电容的电流超前电压90度这一特性。

RC滞后移相电路是电阻在前面,电容在后面。

输入信号从电阻进入,输出信号是从电容上输出,其与电容并联,电压相等,所以输出电路的电压也滞后电流。

同理,RC超前移相电路是电容器在前面,电阻在后面。

可通过改变RC的值来改变移相的度数,相移在0°—90°之间变化。

由它组成的移相电路具有电路简单、工作可靠、成本低、波形好、适应性强,所以选用此方法。

方案二:使用双运放LM318做移相电路。

此电路主要也运用了电容的电流超前电压90度这一特性。

但其不是单纯的无源电路而是结合了集成运放的有源电路,其体积小、性能稳定,输入阻抗高,输出阻抗低,而且可以提供180°的相移。

方案三:使用数字移相技术实现。

主要分为两类:一类为是运用直接数字式频率合成技术DDS;一类是利用单片机计数延时的方法实现;一类是先将模拟信号或移相角数字化,经移相后再还原成模拟信号。

DDS技术的实现电路较为复杂;以D/A转换方式实现的移相,虽然所用元件少,但输出信号的频率难以细调,特别是移相的最小单位太大,只适合于对频率要求不高,且移相角度固定的场合;以延时输出方波的方式实现的移相,输出信号的频率以参考信号的频率为准,而参考信号的频率则可以精确给定,可用于对频率要求高,且需无级移相的场合,但其硬件电路比较复杂。

1.5 信号合成电路设计方案方波信号经过波形变换和移相后,其输出幅度将有不同程度的衰减,合成前需要将各成分的信号幅度调整到规定比例,才能合成为新的合成信号。

本课题采用反向比例运算电路实现幅度调整,采用反向加法运算实现信号合成。

三、总体方案的设计与实现1、原理图:整体方案设计+2、方波发生器的设计与实现周期信号是由一个或几个、乃至无穷多个不同频率的谐波叠加而成的,因此周期信号可以分解成多个乃至无穷多个谐波信号。

方波信号的傅里叶分解函数:() ⎪⎭⎫⎝⎛⋯+++=t t t Ud t f ωωωπ11115sin 513sin 31sin 4 (2-1)在理想情况下,方波的偶次谐波应该无输出信号,始终为零电平,奇次谐波中的一、三、五次谐波的幅度比为1:(1/3):(1/5)。

信号源输出300KHz 的方波信号经过分频滤波电路后可以得到10KHz 、30KHz 、50KHz 的方波,其计算公式表示如下:()()()()⋯+⨯⨯+⨯⨯+⨯⨯=t 10502sin 6.0t 10302sin t 10102sin 33331πππt f (2-2)频率为10KHz 的正弦波信号的峰峰值为6V ;、频率为30KHz 的正弦波信号的峰峰值为2V ;频率为50KHz 的正弦波信号的峰峰值为1.2V 。

本课题的方波发生器部分采用芯片CD4046设计,通过制作后实测的效果看,调节电位器,所产生的频率稳定可靠。

振荡器的充放电容C1接在6脚和7脚之间,调节R1阻值即可调节振荡器振荡频率。

振荡方波从4脚输出。

3、分频电路的设计与实现分频电路采用逻辑元件 74LS161、74LS00、71HC20、CD4013 搭建而成。

分频电路实现将某方波通过分频产生10KHz 、30 KHz 和50 KHz 的新的方波。

根据题意要求,在某特定频率的方波上要产生几个其他频率方波,可按照这些频率的最小公倍数×2为原则,题目要求的三个频率为10KHz 、30KHz 和50KHz ,其公倍数为150KHz ,再乘以2,则上述方波发生器为300KHz 。

验证一下:300KHz 频率30分频得10KHz ,10分频30KHz ,6分频50KHz 。

采用74LS161配合D 触发器CD4013实现分频为上述3个频率的方波,对于CD4013,所起的作用是将分频后非50%占空比调节为50%。

电路如图所示:振荡电路所产生的频率为 300kHz 的方波送到 74HC161与74HC00电路中分别构成 3、5分频电路,输出频率分别为为 100KHz 、60KHz 的方波,送入74HC161与74HC20电路中构成15分频,输出频率为20KHz 的方波。

频率为 100KHz 、60KHz 、20KHz 的方波的方波再经 CD4013D 触发器构成 2分频,由 13 脚输出频率分别为 50KHz 、30KHz 、10KHz 占空比 50%的方波。

D03Q014D14Q113D25Q212D36Q311RCO15ENP 7ENT10CLK 2LOAD 9MR 1U174HC161+5V123U2:A74HC00U1(CLK)D 5Q1CLK3Q2R4S6U3:A4013D03Q014D14Q113D25Q212D36Q311RCO15ENP 7ENT 10CLK 2LOAD 9MR 1U474HC161456U2:B74HC00D 9Q13CLK11Q12R10S8U3:B4013+5VD03Q014D14Q113D25Q212D36Q311RCO15ENP 7ENT 10CLK 2LOAD 9MR 1U574HC161D 5Q1CLK3Q2R 4S6U6:A4013AB C D12456U7:A74LS204、电压跟随电路电压跟随器具有输入阻抗高和输出阻抗低之特点,在电路中起阻抗匹配的作用,为了消除负载对分频电路造成的影响,遂在滤波电路与分频电路间加电压跟随器消除影响,减少纹波。