VHDL语言描述语句报告

第19讲VHDL顺序描述语句

END rsff; ARCHITECTURE rtl OF rsff IS BEGIN

PROCESS(s,r) VARIABLE last_state :BIT;

BEGIN ASSERT(NOT(s =‘1’AND r =‘1’)) REPORT “Both s and r equal to‘1’.” SEVERITY ERROR; IF(s =‘0’AND r =‘0’)THEN last_state := last_state; ELSIF(s =‘0’AND r =‘1’)THEN last_state := 0; ELSE last_state := 1; END IF; q <= last_state; qb <= not(last_state);

q <= tmp2;

END PROCESS;

END rtl;

上例是一个取三个输入位矢量最大值的功能描述, 它在结构体中的进程语句中使用了两个过程调用语 句。

B. 函数调用语句

函数调用与过程调用是十分相似的,不同之处是, 调用函数将返还一个指定数据类型的值,函数的参 量只能是输入值。

函数语句分为两个部分,函数首和函数体。 (1)函数首的格式为: FUNCTION 函数名称(参数列表) RETURN 数据类型名; (2)函数体的格式为: FUNCTION 函数名称(参数列表) RETURN 数据类型名 IS

RETURN语句是一段子程序结束后,返回主程序的控制 语句。它只能用于函数与过程体内,并用来结束当前最内层 函数或过程体的执行。

RETURN语句的书写格式为:

RETURN; RETURN 表达式;

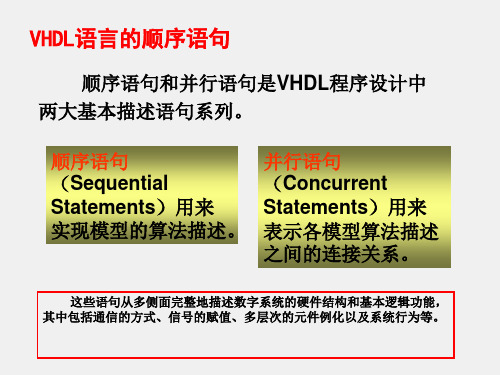

VHDL语言的主要描述语句

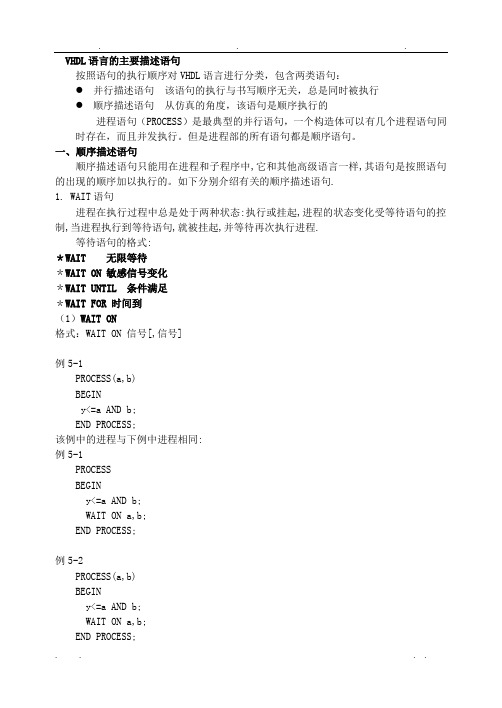

VHDL语言的主要描述语句按照语句的执行顺序对VHDL语言进行分类,包含两类语句:●并行描述语句该语句的执行与书写顺序无关,总是同时被执行●顺序描述语句从仿真的角度,该语句是顺序执行的进程语句(PROCESS)是最典型的并行语句,一个构造体可以有几个进程语句同时存在,而且并发执行。

但是进程部的所有语句都是顺序语句。

一、顺序描述语句顺序描述语句只能用在进程和子程序中,它和其他高级语言一样,其语句是按照语句的出现的顺序加以执行的。

如下分别介绍有关的顺序描述语句.1.WAIT语句进程在执行过程中总是处于两种状态:执行或挂起,进程的状态变化受等待语句的控制,当进程执行到等待语句,就被挂起,并等待再次执行进程.等待语句的格式:*WAIT 无限等待*WAIT ON 敏感信号变化*WAIT UNTIL 条件满足*WAIT FOR 时间到(1)WAIT ON格式:WAIT ON 信号[,信号]例5-1PROCESS(a,b)BEGINy<=a AND b;END PROCESS;该例中的进程与下例中进程相同:例5-1PROCESSBEGINy<=a AND b;WAIT ON a,b;END PROCESS;例5-2PROCESS(a,b)BEGINy<=a AND b;WAIT ON a,b;END PROCESS;(2)WAIT UNTIL 直到条件满足格式: WAIT UNTIL 布尔表达式当进程执行到该语句时,被挂起;若布尔表达式为真时,进程将被启动.例: WAIT UNTIL ((x*10)<100)(3)WAIT FOR 等到时间到格式: WAIT FOR 时间表达式当进程执行到该语句时,被挂起;等待一定的时间后,进程将被启动.例: WAIT FOR 20 ns;WAIT FOR (a*(b+c);(4)多条件WAIT 语句例: WAIT ON nmi,interrupt UNTIL ((nmi=TRUE) OR (interrupt=TRUE)) FOR 5 us 该等待有三个条件:第一,信号nmi和interrupt 任何一个有一次刷新动作第二, 信号nmi和interrupt 任何一个为真第三, 已等待5 us只要一个以上的条件被满足,进程就被启动.*注意:多条件等待时,表达式的值至少应包含一个信号量的值。

vhdl实验报告

vhdl实验报告VHDL实验报告引言:VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和仿真。

本篇实验报告将介绍我在VHDL实验中的学习和实践经验,包括实验目的、实验过程、实验结果以及对VHDL的理解和展望。

一、实验目的VHDL实验的主要目的是让我们掌握VHDL语言的基本语法和使用方法,能够利用VHDL描述数字电路,并通过仿真和综合工具进行验证和实现。

通过这些实验,我们可以深入了解数字电路的原理和设计方法,提高我们的逻辑设计能力和工程实践能力。

二、实验过程在实验过程中,我们首先学习了VHDL的基本语法,包括实体声明、端口声明、信号声明等。

然后,我们通过实例学习了VHDL的建模方法,包括组合逻辑电路的建模和时序逻辑电路的建模。

在组合逻辑电路的建模中,我们学习了使用逻辑运算符和条件语句描述电路的功能;在时序逻辑电路的建模中,我们学习了使用过程语句和时钟信号描述电路的状态转换。

在学习了VHDL的基础知识后,我们开始进行实验设计。

我们选择了一个简单的数字电路,如4位加法器,来进行实验验证。

首先,我们通过VHDL语言描述了加法器的功能和结构,包括输入端口、输出端口和中间信号。

然后,我们使用仿真工具进行了功能仿真,验证了加法器的正确性。

接着,我们使用综合工具将VHDL代码综合成门级电路,并进行了时序仿真和时序优化,验证了加法器的时序正确性和性能。

三、实验结果通过实验,我们成功地实现了4位加法器的功能,并验证了其正确性和性能。

在功能仿真中,我们输入了不同的测试数据,观察了输出结果,发现加法器能够正确地进行加法运算,并得到了正确的结果。

在时序仿真中,我们观察了电路的时序行为,包括输入信号的变化、输出信号的响应和中间信号的传播延迟等,发现加法器能够在时序上满足要求,并且具有较好的性能。

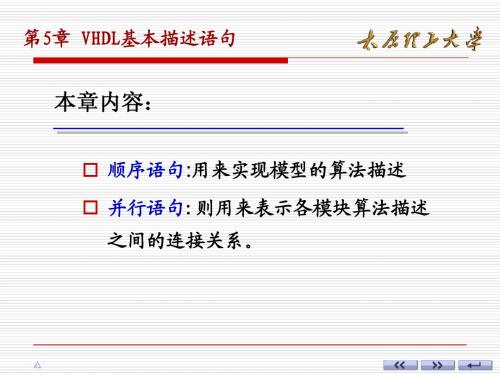

第5章VHDL基本描述语句

多个赋值源

SVEC(0) <= V1; --将V1在上面的赋值1,赋给SVEC(0)

SVEC(1) <= V2;

SVEC(2) <= S1; SVEC(3) <= S2;

--将V2在上面的赋值1,赋给SVEC(1)

--将S1在上面的赋值1,赋给SVEC(2) --将最下面的赋予S2的值‘0’,赋给SVEC(3)

FOR LOOP循环主要用在规定数目的重复情况;

WHILE LOOP则根据控制条件执行循环直到条件为

FALSE。

FOR LOOP语句

FOR LOOP格式:

[标号:] FOR 循环变量 IN 循环次数范围 LOOP

顺序处理语句;

END LOOP [标号];

循环变量:属于LOOP语句的局部变量,不需要事先定义,也不能 被赋值,它的值从循环次数范围的初值开始,执行一次顺序语句 自动加一,当其值超出循环次数范围时,则退出循环语句。

5.1.1赋值语句

语句格式: 变量赋值目标:= 赋值源;

信号赋值目标<= 赋值源;

比较: (1)信号赋值有一定的延时,在时序电路中,在时 钟信号触发下的信号赋值,目标信号要比源信号延迟 一个时钟周期;变量赋值语句立即执行,没有延时。 (2)进程中同一变量多次赋值时按顺序立即执行, 而信号多次赋值时,只有进程结束前最后一个赋值被 执行。

不完整IF语句

作用:形成锁存,用于构成时序电路,而组合电路只能

使用完整的IF语句。

例5-6: IF (clk’event and clk=’1’) then

Q<=d;

End if;

二选一IF语句

语句格式:

IF 条件 THEN 顺序执行语句1;

第五VHDL语言的主要描述语句剖析

wait on 所起作用与进程的敏感信号量表相同, 两者不能同时存在。

2020/11/11

15

2. wait until 语句

1) 书写格式 wait until 布尔表达式;

❖ 利生变化时,就自动检测

布尔表达式是否为真; ❖ 如果为真,则进程脱离等待状态,执行后续语句;

assert语句检查一个布尔表达式为真或假,如果值 是真,则该语句任何事都不做,如果值是假,断言 语句将输出一用户规定的字符串到标准输出终端。

2020/11/11

10

设计者所写的文 字串,通常是说 明错误的原因, 文字串应用双引 号括起来。

错误严重程度的级别,

分为4级别:failure, error,waring,

如:在一个信号值维持期间,如果存在任何毛刺、脉 冲等周期小于器件本身的惯性延时的情况,输出信号 的值将不变,否则将引起信号的变化。

2020/11/11

5

惯性延时举例

假设某门电路的惯性延 时为20 ns

b<=inertial a after 20 ns;

10ns

所有器件都存在惯性延时, 在代入语句中加上惯性延 时时间,可以仿真硬件电 路实际工作情况,如:

2020/11/11

2

5.1.1 信号代入语句

1) 书写格式

目的信号量<= 敏感信号量表达式;

2) 举例

处于构造体中的信号代入语句 z <= a or (b nand c);

有3 个敏感量 a、b、 c,无论哪一个敏感量发生 变化,该代入语句将被执行。

2020/11/11

3

a <= b after 5 ns; --表示当b发生新的变化5ns后,才被代入到信

VHDL程序的主要描述语句

端口方向(端口类型)

结构体的语法格式:

• architecture 结构体名称 of 实体 名称 is • 说明语句 • 内部信号、常数、数据类型、子程序 (函数、过程)、元件等的说明; • begin • 功能描述语句; • end [architecture] 结构体名称;

vhdl中的主要描述语句分为两 类:描述行为和描述结构。

• (1)赋值情况:当被选择的信号发生变化时, 启动执行,满足哪一个条件,就将其对应的表 达式代入目标信号。 • (2)选择型语句中各行结尾均未“,”,只 有最后一行用“;”,不能有重叠的条件分支, 最后条件可为 others,若最后条件不为 others,则其它条件必须包含表达式的所有 可能值。 • (3)执行:选择型信号赋值语句无优先级顺 序,与进程中的 case 语句等价。

例:用选择型语句设计一个四 选一的数据选择器

例:用选择型语句设计一个四 选一的数据选择器

练习:用选择型语句设计一个 八选一的数据选择器

三种并行信号赋值语句的共同特点:

• (1)赋值目标必须时信号,与其他并行 语句同时执行,与书写顺序无关; • (2)每一个信号赋值语句等效于一个进 程语句,所有输入信号的变化都将启动 该语句的执行。 • c<= a xor b;

(1)基本型

• • • • • • 格式: 信号名<=敏感信号量表达式 after 时间表达式 例:s<=x xor y; sum<=s xor cin after 1ns; 说明:若未注明延时表示延时很小,δ延时。 延时可分为两类:传输延时与惯性延时

• 传输延时:模拟信号在连线(或传输线) 上的延时。 • 格式:b<=transport a after 20ns;

第2-4讲 VHDL语言主要描述语言

能否定 义为信 号?

VHDL顺序语句

5、LOOP语句—WHILE循环(P45) 格式: 标号:WHILE 循环控制条件 LOOP 顺序处理语句; …… END LOOP; 注意: 循环控制条件没有直接给出循环次数,可以是任何 条件表达式,条件为“真”,进行循环,条件为“假”, 退出循环。 条件表达式需初始化。

EDA技术实用教程

第2-4讲 VHDL语言语言主要描述 语句

VHDL主要描述语句

在结构体 (ARCHITECTURE) 中 执行的语句 在进程(PROCESS) 函数(FUNCTION) 过程 (PROCEDURE) 中执行的语句

并行处理语句

硬件 描述 的特 点

高级 语言 的特 点

顺序处理语句

VHDL顺序语句P39

VHDL顺序语句

例: 8位奇偶校验电路 architecture abc of example is begin PROCESS(a) variable tmp:std_logic; begin tmp:=„0‟; FOR i IN 0 to 7 LOOP tmp:=tmp XOR a(i); END LOOP; Y<=tmp; end process; end abc;

VHDL顺序语句

例:

architecture abc of example is signal c :STD_LOGIC; begin PROCESS(a,b) begin c<=a and b after 10 ns; a<=„1‟; b<=„1‟; b<=„0‟; out<=c; end process; end abc;

VHDL断言语句与报告语句

例: RS触发器的VHDL描述中REPORT语句的使用。

LIBRARY IEEE; USE IEEE. STD_LOGIC_1164.ALL;

ENTITY rsff IS

PORT(s :IN BIT; r :IN BIT;

ቤተ መጻሕፍቲ ባይዱ

q :OUT BIT;

qb :OUT BIT); END rsff;

例: RS触发器的VHDL描述中断言语句的使用

LIBRARY IEEE; USE IEEE. STD_LOGIC_1164.ALL; ENTITY rsff IS PORT(s :IN BIT; r :IN BIT; q :OUT BIT; qb :OUT BIT); END rsff;

ARCHITECTURE rtl OF rsff IS BEGIN

last_state := 0;

ELSE last_state := 1;

END IF;

q <= last_state; qb <= not(last_state);

END PROCESS;

END rtl;

断言语句(Assert)

断言语句分为顺序断言语句和并行断言语句,顺序 断言语句主要用于进程、函数和过程仿真、调试中的人 机对话,它可以给出一个文字串作为警告和错误信息。 断言语句的书写格式如下:

PROCESS(s,r)

VARIABLE last_state :BIT; BEGIN ASSERT(NOT(s =„1‟AND r =„1‟)) REPORT “Both s and r equal to„1‟.” SEVERITY ERROR;

IF(s =„0‟AND r =„0‟)THEN last_state := last_state; ELSIF(s =„0‟AND r =„1‟)THEN last_state := 0; ELSE last_state := 1; END IF; q <= last_state; qb <= not(last_state); END PROCESS; END rtl;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

[进程标号: ] Process [ 触发信号1,触发信号2,…… + [ 定义区 ] Begin 顺序语句 …… End Process [ 进程标号] ;

注: 方括号内容可以省略;触发信号将决定该过程是否执行;一个结构体 当中可以有多个过程;多个进程语句之间是并行执行,进程内部属于 顺序执行语句。

顺序语句:

按动作特点:照语句书写顺序执行; 使用范围 :进程、函数和过程内部出现; 实际应用 :时序电路、数据流控制电路;

基本的VHDL顺序语句

VHDL中的顺序语句用于描述进程或子程序的内部功能,且只能出现在 PROCESS、FUNCTION、PROCEDURE等语句中。 可以用来设计 时序电路、组合电路。 主要作用:时序流控制、程序控制、条件和迭代等,行为描述代码。 常用的顺序语句见下表。

例如下面语句是错误的: PROCESS(clk) BEGIN IF rising_eng_edge(clk) then … end if; end peocess;

entity mul is port (a,b,c,selx,sely : IN bit; data_out: OUT BIT); end mul; ARCHITECTURE ex OF mul IS SIGNAL temp :BIT ; BEGIN p_a: PROCESS(a,b,selx) BEGIN IF(SELX='0') THEN temp<=a; ELSE temp<=b; END IF; END PROCESS p_a; p_b: PROCESS(temp,c,sely) BEGIN IF(SELy='0') THEN data_out<=temp; ELSE temp<=c; END IF; END PROCESS p_b; end ex;

语法说明:

时钟沿的VHDL描述方法总结(3种): 上升沿描述1: clk’event and clk=‘1’ ; 下降沿描述1: clk’event and clk=‘0’ ;

上升沿描述2:

clk='1' AND clk'EVENT AND clk'LAST_VALUE='0‘ 下降沿描述2: clk=‘0' AND clk'EVENT AND clk'LAST_VALUE=‘1‘

VHDL语言描述语句

一、VHDL语句分类; 二、基本的VHDL顺序语句 三、基本的VHDL并行语句 四、常用组合单元电路VHDL设计 五、常用时序单元电路VHDL设计

一、VHDL语句分类

按照功能分类:

赋值语句; 数据流控制语句(转向控制语句): 1. Case … when … ( 顺序 ); 2. If … else … ( 顺序 ); 3. with … select when ( 并 ); 4. When …else ( 并 ); 模块化设计语句:

上升沿描述3:

rising_edge(clk) ; 下降沿描述3: falling_edge(clk); Clk’event ??

进程语句总结:

进程仅在敏感信号发生变化时才执行。 特点:进程内部,顺序语句;进程语句之间,并行。 不同进程内不可以对同一信号赋值,即不可多重赋值。 进程内信号和变量赋值效果不同。 一个进程内不能同时扑捉同一个时钟信号的上升沿或者下降沿。

2.进程语句——语法说明

a) 进程标号:用于标识进程,可选。多个进程时,提高程序可读性;

a) 敏感信号列表:敏感信号发生变化(上升沿或者下降沿),进程被 激活,从而执行内部顺序语句。 注意:可以有多个敏感信号,用逗号隔开,任何一个变化都激活进 程,否则进程挂起。

c)

进程声明区: 用于定义进程内部的局部变量,信号不可在此声明。进程之间数据 交流通过全局信号。

基本的VHDL顺序语句

1、process(进程); 2、信号和变量; 3、IF语句; 4、C ASE语句; 5、CASE语句和IF语句的比较; 6、LOOP语句; 7、WAIT语句; 8、使用顺序代码设计组合逻辑电路;

5.3.1 进程(PROCESS)语句

语法说明: 1、Process为过程语句,定义如下:

process ; component ; generate ; block ;for…loop ; 子程序调用语句

仿真语句: wait ; 按照语句的执行方式特点分为: 并行语句:

按动作特点:语句执行顺序与书写顺序无关; 使用范围 :进程语句外部的语句都是并行的; 实际应用 :对应于各自独立运行的逻辑电路;

d) 顺序语句: 进程内部语句顺序执行。

e) 用处:适合描述时序电路。也可用于组合逻辑电路的设计。

例1:进程语句例程——带异步复位的D触发器

LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; ENTITY cydff IS PORT ( d,clk,rst : IN STD_LOGIC ; q : OUT STD_LOGIC ) ; END ENTITY cydff ; ARCHITECTURE behave OF cydff IS BEGIN cydff_inst : PROCESS ( clk,rst ) BEGIN IF (rst=‘1’) then q<=‘0’; elsIF ( clk='1' AND clk'LAST_VALUE='0' AND clk'EVENT ) THEN q<=d; END IF ; END PROCESS cydff_inst ; END ARCHITECTURE behave ;

顺序语句 顺序赋值语句 IF语句 CASE语句 LOOP语句 WAIT语句 NULL语句 ASSERT语句 语句作用 信号或变量赋值 条件控制 条件控制 循环控制 描述延迟 空操作 仿真时报告错误 是否可综合 可综合 可综合 可综合 循环次数有限时可综 合 WAIT ON和WAIT UNTIL可综合 可综合 不可综合