微机试卷

微机原理 试卷)

模拟试题(一)一、单选题1.在 8086 宏汇编过程中不会产生指令码,只用来指示汇编程序如何汇编的指令是 A. 汇编指令。

B. 伪指令 C. 机器指令。

C. (AX) < (DX) D. (AX) ≤ (DX) 。

D. 0DH D. 宏指令2.在 CMP AX,DX 指令执行后,当标志位 SF、OF、ZF 满足下列逻辑关系(SF⊕OF)+ZF=0 时,表明 A. (AX) > (DX) B. (AX) ≥ (DX)3.8086 微机系统的 RAM 存储单元中,从 0000H:002CH 开始依次存放 23H,0FFH,00H,和 0F0H 四个字节,该向量对应的中断号是 A. 0AH 对 B. 0BH C. 0CH 4.8255 的 A 口工作在方式 1 输入时,其中断允许控制位 INTE 的开/关是通过的按位置位/复位操作完成的。

A. PC0 A. 单步陷阱中断指令后接着 INTO 指令则会 A. 进入 INTO 中断服务子程序 C. 死机 B. PC2 B. INTR C. PC4 C. 被零除。

B. 执行 INTO 后面的指令 D. 显示器显示 OVERFLOW D. 断点 D. PC6 。

5.在 8086 中断优先级顺序中,最低优先级的中断源是6.在 PC/XT 中,设(AX)=9305H,(BX)=6279H,若 ADD BX,AX7.有一微机系统,采用 CPU 的低 10 位地址线 A0~A9 作为输入输出口的地址线,系统中接口芯片内部有 16 个端口地址,该接口芯片的片选信号由地址译码器产生,则地址译码器的输入地址线一般应为()。

A. A5~A9 A. 工作方式字 C. 计数执行部件 CE(减一计数单元)的当前值调试的程序。

A. RAM B. ROM C. PROM B. 中断类型号地址的高 5 位 D. 中断类型号的高 5 位 D.E2PROM 。

10.8259A 工作在 8086/8088 模式时,初始化命令字 ICW2 用来设置 A. 中断向量地址的高 8 位 C. 中断向量的高 5 位 B. A4~A9 C. A2~A9 D. A0~A9 )。

微机原理及接口技术试题及答案精选全文完整版

《微机原理及接口技术》试卷(A )适用专业(计算机科学与技术) 使用班级()一、选择题(每题 1 分,共 15 分) 1. 微机中控制总线传送的是 ( )。

A.存储器和I/O 接口的地址码B.微处理器向内存储器和I/O 的命令信号C.存储器和I/O 设备向微处理器传送的状态信号D.B 和C2. 8253可编程定时/计数器,在初始化时写入的最大计数初值是 ( )。

A.0000HB.7FFFHC.65535D.FFFFH3. 在异步串行通信中引入了"波特率因子"的概念,波特率因子为16,64时,接收时钟的频率为波特率的16,64倍,引入波特率因子的目的是 ( )。

A.识别正确的起始位 B.提高接收速度 C.提高采样精度 D.三者都是4. 8086 CPU 标志寄存器共有( )位,其中使用7位,未使用其它位均作为CPU 指令运行后的状态信息和控制标志信息。

A. 8 B. 10 C. 16 D. 205. 8086微处理器CLK 引脚输入时钟信号是由( )提供。

A.8284 B.8288C.8287 D.82896. 最基本的读操作包含4个状态,即T 1 、T 2、T 3和T 4 ,当存储器或 I/O 设备的速度慢于CPU 速度时,在( )状态之间插入1个或几个等待状态T W 。

A. T 3和T 4 B. T 1和T 2 C. T 2和T 3 D. T 1和T 37. 在计算机与外设之间数据的传送方式分为串行传送方式和( )传送方式两类。

A.并行传送方式 B. 同步传送方式 C. 异步传送方式 D. 串/并传送方式8. 8253的( )是软件触发选通方式。

A.方式OB.方式1C.方式2D.方式4 9.串行异步通信协议中一个字符正式发送前,先发送( )低电平有效。

A.两个起始位 B .3个起始位 C. 1.5个起始位 D .1个起始位 10.对8255A 的C 口执行按位置位/复位操作时,写入的端口地址是( )。

微机原理期末考试试卷(有答案)

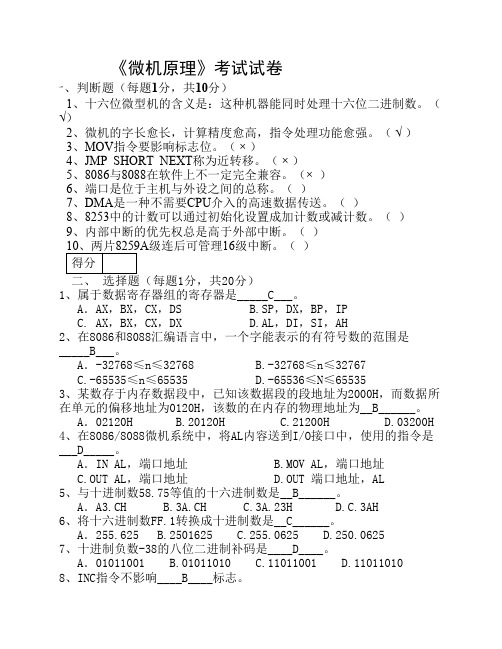

得分《微机原理》考试试卷一、判断题(每题1分,共10分)1、十六位微型机的含义是:这种机器能同时处理十六位二进制数。

(√)2、微机的字长愈长,计算精度愈高,指令处理功能愈强。

( √ )3、MOV指令要影响标志位。

( × )4、JMP SHORT NEXT称为近转移。

( × )5、8086与8088在软件上不一定完全兼容。

(× )6、端口是位于主机与外设之间的总称。

()7、DMA是一种不需要CPU介入的高速数据传送。

()8、8253中的计数可以通过初始化设置成加计数或减计数。

()9、内部中断的优先权总是高于外部中断。

()10、两片8259A级连后可管理16级中断。

()二、 选择题(每题1分,共20分)1、属于数据寄存器组的寄存器是_____C___。

A.AX,BX,CX,DS B.SP,DX,BP,IPC. AX,BX,CX,DXD.AL,DI,SI,AH2、在8086和8088汇编语言中,一个字能表示的有符号数的范围是_____B___。

A.-32768≤n≤32768 B.-32768≤n≤32767C.-65535≤n≤65535D.-65536≤N≤655353、某数存于内存数据段中,已知该数据段的段地址为2000H,而数据所在单元的偏移地址为0120H,该数的在内存的物理地址为__B______。

A.02120H B.20120H C.21200H D.03200H4、在8086/8088微机系统中,将AL内容送到I/O接口中,使用的指令是___D_____。

A.IN AL,端口地址 B.MOV AL,端口地址C.OUT AL,端口地址D.OUT 端口地址,AL5、与十进制数58.75等值的十六进制数是__B______。

A.A3.CH B.3A.CH C.3A.23H D.C.3AH6、将十六进制数FF.1转换成十进制数是__C______。

A.255.625 B.2501625 C.255.0625 D.250.06257、十进制负数-38的八位二进制补码是____D____。

微机原理 期末考试题库及答案(含3套试卷)

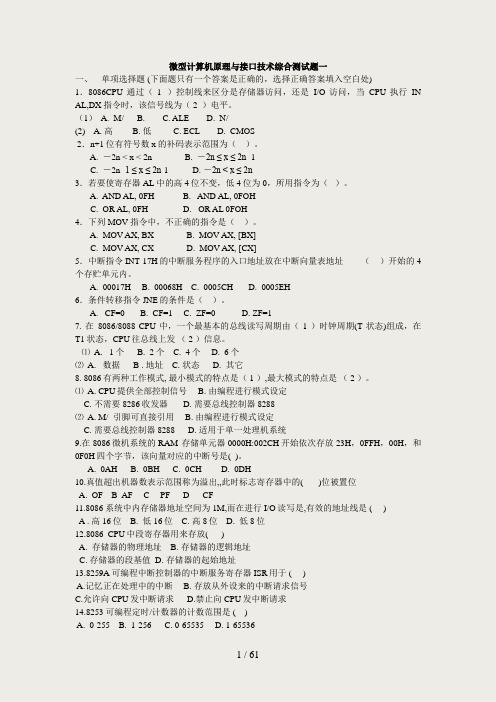

微型计算机原理与接口技术综合测试题一一、单项选择题 (下面题只有一个答案是正确的,选择正确答案填入空白处)1.8086CPU通过(1 )控制线来区分是存储器访问,还是I/O访问,当CPU执行IN AL,DX指令时,该信号线为( 2 )电平。

(1) A. M/ B. C. ALE D. N/(2) A. 高 B. 低 C. ECL D. CMOS2.n+1位有符号数x的补码表示范围为()。

A. -2n < x < 2nB. -2n ≤ x ≤ 2n -1C. -2n -1 ≤ x ≤ 2n-1D. -2n < x ≤ 2n3.若要使寄存器AL中的高4位不变,低4位为0,所用指令为()。

A. AND AL, 0FHB. AND AL, 0FOHC. OR AL, 0FHD. OR AL 0FOH4.下列MOV指令中,不正确的指令是()。

A. MOV AX, BXB. MOV AX, [BX]C. MOV AX, CXD. MOV AX, [CX]5.中断指令INT 17H的中断服务程序的入口地址放在中断向量表地址()开始的4个存贮单元内。

A. 00017HB. 00068HC. 0005CHD. 0005EH6.条件转移指令JNE的条件是()。

A. CF=0B. CF=1C. ZF=0D. ZF=17. 在8086/8088 CPU中,一个最基本的总线读写周期由(1 )时钟周期(T状态)组成,在T1状态,CPU往总线上发( 2 )信息。

⑴ A. 1个 B. 2个 C. 4个 D. 6个⑵ A. 数据 B . 地址 C. 状态 D. 其它8. 8086有两种工作模式, 最小模式的特点是( 1 ),最大模式的特点是( 2 )。

⑴ A. CPU提供全部控制信号 B. 由编程进行模式设定C. 不需要8286收发器D. 需要总线控制器8288⑵ A. M/ 引脚可直接引用 B. 由编程进行模式设定C. 需要总线控制器8288D. 适用于单一处理机系统9.在8086微机系统的RAM 存储单元器0000H:002CH开始依次存放23H,0FFH,00H,和0F0H四个字节,该向量对应的中断号是( )。

(完整word版)微机原理与接口技术期末试卷及答案

机原理与接口技术■期末考试试题及答案一、填空题(20*1)1、微机系统由(硬件系统〉和(软件系统)两部分组成。

2、80X6冇(20 )位地址线,存储器容量为(1M )B。

3、8086CPU内部组成结构从功能上讲,可分为(BIU )和(EU )两部分.4> 8086/8088 的四个段寄存器为(DS )、(ES )、(SS )、(CS )5、用来存放CPU状态信息的寄存器是(FLAGS )。

6、用來存放指令地址的寄存器是(IP)«7、X0X6的16位标志寄存器FLAGS屮OF=1表示运算结果(溢出).ZF=1表示运算结果为雯。

PF=()表示运算结果的低8位中I的个数为(奇数).8、8086的16位标志寄存器FLAGS中IF=1表示CPU (允许)中断,TF=I表示CPU进入(单步)工作方式。

9、地址4000H:0300H,其物理地址是(4O3OOH).段地址是(4000H ),偏移地址是(0300H1()、X0X6存储器管理采用(分段管理)技术。

IK I/O端口的寻址方式有两种,分别是(丸接寻址),(间接寻址).12、指令J() NEXT农示()F=(I )时转移。

13、将I/O设备端口内容读入AL中的指令助记符是(IN )。

14、8086CPU的1/()捋令采用间接寻址时,使用的间接寄存器是(DX)°15、设置DF=1的指令为(STD ).16、衲除CF标志的指令为(CLC )o17、一对操作堆栈的指令为(POP )和(PUSH )。

18、LOOPNZ的循环条件为(CXH0 HZF=0九19、实现无符巧数乘2的指令的助记符是(SHL ),实现冇符号数除2的抬令的助记符是(SAR )o20、变量/标号的三个属性是(段属性),(偏移属性).(类舉属性)o21、DEBUG命令中,反汇编命令的英文字母为(U ),显示内存命令的英文字母为(D ), 跟踪执行命令的英文字母为(T ),显示和修改寄存器的命令(R ).汇编命令是(A)。

微机试卷

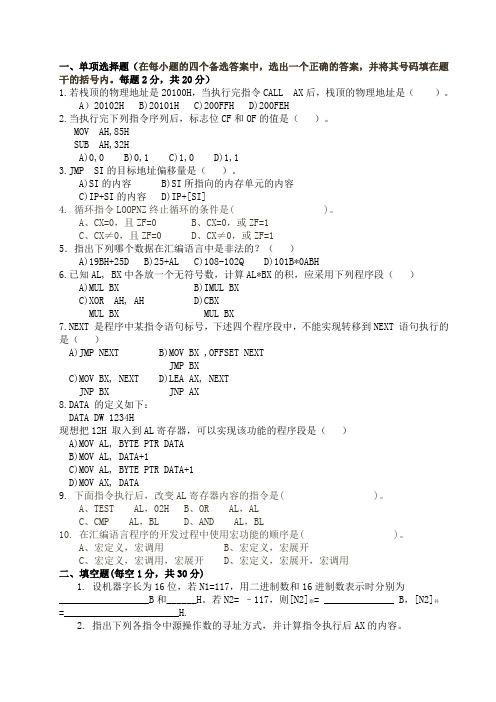

一、单项选择题(在每小题的四个备选答案中,选出一个正确的答案,并将其号码填在题干的括号内。

每题2分,共20分)1.若栈顶的物理地址是20100H,当执行完指令CALL AX后,栈顶的物理地址是()。

A)20102H B)20101H C)200FFH D)200FEH2.当执行完下列指令序列后,标志位CF和OF的值是()。

MOV AH,85HSUB AH,32HA)0,0 B)0,1 C)1,0 D)1,13.JMP SI的目标地址偏移量是()。

A)SI的内容 B)SI所指向的内存单元的内容C)IP+SI的内容 D)IP+[SI]4.循环指令LOOPNZ终止循环的条件是( )。

A、CX=0,且ZF=0B、CX=0,或ZF=1C、CX≠0,且ZF=0D、CX≠0,或ZF=15.指出下列哪个数据在汇编语言中是非法的?()A)19BH+25D B)25+AL C)108-102Q D)101B*0ABH6.已知AL, BX中各放一个无符号数,计算AL*BX的积,应采用下列程序段()A)MUL BX B)IMUL BXC)XOR AH, AH D)CBXMUL BX MUL BX7.NEXT 是程序中某指令语句标号,下述四个程序段中,不能实现转移到NEXT 语句执行的是()A)JMP NEXT B)MOV BX ,OFFSET NEXTJMP BXC)MOV BX, NEXT D)LEA AX, NEXTJNP BX JNP AX8.DATA 的定义如下:DATA DW 1234H现想把12H 取入到AL寄存器,可以实现该功能的程序段是()A)MOV AL, BYTE PTR DATAB)MOV AL, DATA+1C)MOV AL, BYTE PTR DATA+1D)MOV AX, DATA9.下面指令执行后,改变AL寄存器内容的指令是( )。

A、TEST AL,02HB、OR AL,ALC、CMP AL,BLD、AND AL,BL10. 在汇编语言程序的开发过程中使用宏功能的顺序是( )。

微机原理试卷库合集(有答案)

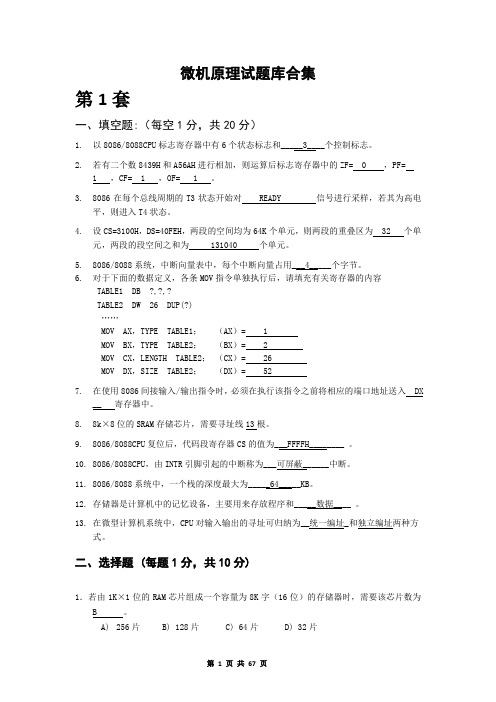

微机原理试题库合集第1套一、填空题:(每空1分,共20分)1.以8086/8088CPU标志寄存器中有6个状态标志和_____3____个控制标志。

2.若有二个数8439H和A56AH进行相加,则运算后标志寄存器中的ZF= 0 ,PF=1 ,CF= 1 ,OF= 1 。

3.8086在每个总线周期的T3状态开始对 READY 信号进行采样,若其为高电平,则进入T4状态。

4.设CS=3100H,DS=40FEH,两段的空间均为64K个单元,则两段的重叠区为 32 个单元,两段的段空间之和为 131040个单元。

5.8086/8088系统,中断向量表中,每个中断向量占用___4_____个字节。

6.对于下面的数据定义,各条MOV指令单独执行后,请填充有关寄存器的内容TABLE1 DB ?,?,?TABLE2 DW 26 DUP(?)……MOV AX,TYPE TABLE1;(AX)= 1MOV BX,TYPE TABLE2;(BX)= 2MOV CX,LENGTH TABLE2;(CX)= 26MOV DX,SIZE TABLE2;(DX)= 527.在使用8086间接输入/输出指令时,必须在执行该指令之前将相应的端口地址送入 DX__ 寄存器中。

8.8k×8位的SRAM存储芯片,需要寻址线13根。

9.8086/8088CPU复位后,代码段寄存器CS的值为___FFFFH________ 。

10.8086/8088CPU,由INTR引脚引起的中断称为___可屏蔽______中断。

11.8086/8088系统中,一个栈的深度最大为_____64_____KB。

12.存储器是计算机中的记忆设备,主要用来存放程序和_____数据____ 。

13.在微型计算机系统中,CPU对输入输出的寻址可归纳为__统一编址_和独立编址两种方式。

二、选择题 (每题1分,共10分)1.若由1K×1位的RAM芯片组成一个容量为8K字(16位)的存储器时,需要该芯片数为B 。

微机原理与接口技术试题四套卷版+答案

微机原理与接⼝技术试题四套卷版+答案微机原理与接⼝技术考试试卷(A)专业学号姓名成绩⼀、填空题(每⼩题5分,共10分)1. 某控制电路中,输出控制端⼝的⼝地址为34CH,输⼊状态端⼝的⼝地址为34DH。

现从输⼊⼝读⼊外部状态,若不为80H,就输出FFH关闭设备,否则输出00H开启设备。

请完善下⾯的程序。

...............MOV DX, 34DH;①________AL, DX②________AL, 80H③________MOV DX, 34CHMOV AL, 00HOUT DX, AL④________EXITGO-OFF: MOV DX, 34CHMOV AL, ⑤__________OUT DX, ALEXIT: RET2.下⾯是⼀个中断处理⼦程序的加载程序段,中断类型号为60H,请完善该程序段。

INT-INT PROC FAR.......... ;保护现场SUB AX, ①__________;MOV ES, AX;ES清零MOV ②__________,OFFEST inthandlerMOV AX, SEG inthandlerMOV DI ,③__________SHL DI, 1SHL ④__________, 1MOV ⑤__________, BXMOV ES:[DI]+2, AX............;恢复现场RETINT_INT ENDP⼆、单项选择题(每⼩题1分,共10分)1.指令MOV AX,[BX][SI]中源操作数的寻址⽅式是 ( )A.寄存器间接寻址B.变址寻址C.相对寻址D.基址变址寻址2.8086 CPU内有指⽰下条指令有效地址的指⽰器是 ( )A.IPB.SPC.BPD.SI3. .CPU与外设交换数据,当采⽤程序控制I/O⽅式时,是( )。

A.以CPU为主动⽅B.以存储器为主动⽅C.以外设为主动⽅D.外设直接和存储器交换数据4.8253在下⾯⼏种不同的⼯作⽅式中,可⽤GA TE作重触发信号的是( )。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

微机原理及运用声明:习题仅供参考不负任何责任1. 微处理器,微型计算机和微型计算机系统三者之间有何区别?答:微处理器即CPU,它包括运算器、控制器、寄存器阵列和内部总线等部分,用于实现微型计算机的运算和控制功能,是微型计算机的核心;一台微型计算机由微处理器、内存储器、I/O接口电路以及总线构成;微型计算机系统则包括硬件系统和软件系统两大部分,其中硬件系统又包括微型计算机和外围设备;由此可见,微处理器是微型计算机的重要组成部分,而微型计算机系统又主要由微型计算机作为其硬件构成。

2.8086从功能上分成了EU和BIU两部分。

这样设计的优点是什么? 答:8086CPU 在功能上分成了EU和BIU两部分,BIU负责取指令,EU负责指令的执行,它们之间既互相独立又互相配合,使得8086可以在执行指令的同时进行取指令的操作,即实现了取指令和执行指令的并行工作,大大提高了CPU和总线的利用率,从而提高了指令的处理速度。

3.设CPU中各有关寄存器的当前状况为:SS=0a8bH、DS=17ceH、CS=dc54H、BX=3 94bH、IP=2f39H、SP=1200H,BX 给出的是某操作数的有效地址,请分别写出该操作数、下一条要取的指令及当前栈顶的逻辑地址和物理地址。

答:该操作数的逻辑地址为DS:BX=17CE:394BH,物理地址=17CEH*10H+394BH=1B62BH;下一条要取的指令的逻辑地址为CS:IP=DC54:2F39H,物理地址=DC54H*10H+2F39 H=DF479H;当前栈顶的逻辑地址=SS:SP=0A8B:1200H,物理地址=0A8BH*10H+1 200H=0BAB0H。

4. .若DS=157DH时,某操作数的物理地址是215FAH,当DS=18DEH时,该操作数的物理地址是多少?答:该操作数的段内偏移地址=该操作数的物理地址-DS=215FAH-157D0H=BE2AH, 故当DS=18DEH时,该操作数的物理地址=DS*10H+BE 2AH=18DE0H+BE2AH=24C0AH5. 设 AX=2875H、BX=34DFH、SS=1307H、SP=8H,依此执行 PUSH AX、PUSH BX、POP AX、POP CX后栈顶指针变为多少?AX=? BX=? CX=?答:当前栈顶指针=SS*10H+SP=13070H+8H=13078H,依此执行PUSH AX、PUSH BX、POP AX、PO P CX后栈顶指针仍为13078H。

但AX=34DFH,BX=34DFH,CX=2875H。

6.假定(BX)=637DH,(SI)=2A9BH,位移量D=3237H,试确定在以下各种寻址方式下的有效地址是什么?(1)立即寻址(2)直接寻址(3)使用BX的寄存器寻址(4)使用BX的间接寻址(5)使用BX的寄存器相对寻址(6)基址变址寻址(7)相对基址变址寻址答:(1)立即数寻址的有效地址是当前IP的内容;(2)直接寻址,若使用位移量D=3237H进行,则有效地址为3237H;(3)使用BX的寄存器寻址时,操作数在BX寄存器中,因此无有效地址;(4)使用BX的间接寻址时,有效地址在BX寄存器中,即有效地址=637DH;(5)使用BX的寄存器相对寻址的有效地址=(BX)+D=637DH+3237H=95B4H;(6)基址变址寻址的有效地址=(BX)+(SI)=637DH+2A9BH=8E18H;(7)相对基址变址寻址的有效地址=(BX)+(SI)+D=C050H;7. 7.写出以下指令中内存操作数的所在地址。

(1)MOV AL,[BX+5](2)MOV [BP+5],AX(3)INC BYTE PTR [SI+3](4)MOV DL,ES:[BX+DI](5)MOV BX,[BX+SI+2]答:(1)指令MOV AL,[BX+5]中内存操作数的所在地址=(DS)*10H+(BX)+5;(2)指令MOV [BP+5],AX中内存操作数的所在地址=(SS)*10H+(BP)+5和(SS)*10H+(BP)+6;(3)指令INC BYTE PTR[SI+3]中内存操作数的所在地址=(DS)+(SI)+3;(4)指令MOV DL,ES:[BX+DI]中内存操作数的所在地址=(ES)*10H+(BX)+(DI);(5)指令MOV BX,[BX+SI+2]中内存操作数的所在地址=(DS)*10H+(BX)+(SI)+2和(DS)*10H+(BX)+(SI)+3;8. 8.判断下列指令书写是否正确,如有错误,指出错在何处并用正确的程序段(一条或多条指令)实现原错误指令((8)、(13)除外)期望实现的操作。

(1)MOV AL,BX (9)MOV ES,3278H(2)MOV AL,SL (10)PUSH AL(3)INC [BX] (11)POP [BX](4)MOV 5,AL (12)MOV [1A8H],23DH(5)MOV [BX],[SI] (13)PUSH IP(6)MOV BL,F5H (14)MOV [AX],23DH(7)MOV DX,2000H (15)SHL AX,5(8)POP CS (16)MUL AX,BX答:(1)MOV AL,BX 错,源操作数为字类型,目的操作数为字节类型,二者不一致。

应改为:MOV AX,BX 或 MOV AL,BL ;(2)MOV AL,SL 错,SI寄存器不能分为高8位和低8位使用,即没有SL寄存器。

应改为:MOV AX,SI(3)INC [BX] 错,未指定操作数的类型。

应改为:INC BYTE PTR [BX](4)MOV 5,AL 错,目的操作数使用了立即数,在指令中一般不允许。

应改为:MOV DS:[5],AL(5)MOV [BX],[SI] 错,源操作数和目的操作数均为内存单元,不允许。

应改为:MOV AX,[SI]MOV [BX],AX(6)MOV BL,F5H 错,源操作数错,以A~F开头的数字前应加0。

应改为:MOV BL,0F5H(7)MOV DX,2000H 正确。

(8) POP CS 错,不能将栈顶数据弹至CS中。

(9)MOV ES,3278H 错,立即数不能直接送ES寄存器。

应改为:MOV AX,3278HMOV ES,AX(10)PUSH AL 错,栈操作不能按字节进行。

应改为:PUSH AX(11)POP [BX] 正确。

(12)MOV [1A8H],23DH 错,源操作数是立即数,目的操作数必须使用寄存器指出。

应改为:MOV BX,1A8HMOV [BX],23DH(13)PUSH IP 错,不能用IP寄存器做源操作数。

(14)MOV [AX],23DH 错,不能用AX寄存器间接寻址。

应改为:MOV BX,AXMOV [BX],23DH(15)SHL AX,5 错,不能用大于己于1的立即数指出移位位数。

应改为:MOV CL,5SHL AX,CL(16)MUL AX,BX 错,目的操作数AX是隐含的,不能在指令中写出。

应改为:MUL BX9.要想完成把[2000H]送[1000H]中,用指令:MOV [1000H],[2000H]是否正确?如果不正确,应用什么方法?答:把[2000H]送[1000H]中,用指令 MOV [1000H],[2000H]不正确,应改为:MOV AX,[2000H] MOV [1000H],AX一、填空题1、执行部件EU的组织有: 4 个通用寄存器,4个专用寄存器和1个标志寄存器和算术逻辑部件。

2、8086CPU从偶地址访问内存1个字时需占用 1 个总线周期,而从奇地址访问内存1个字操作需占用 2 个总线周期。

3、IBM-PC机中的内存是按段存放信息的,一个段最大存贮空间为64K字节。

4、8086微处理机在最小模式下,用M/IO来控制输出地址是访问内存还是访问I/O。

5、一台计算机能执行多少种指令,是在设计时确定的。

二、单项选择题1、微型计算机的性能主要由 B 来决定。

A、价钱B、CPUC、控制器D、其它2、对微处理器而言,它的每条指令都有一定的时序,其时序关系是 CA、一个时钟周期包括几个机器周期,一个机器周期包括几个指令周期。

B、一个机器周期包括几个指令周期,一个指令周期包括几个时钟周期。

C、一个指令周期包括几个机器周期,一个机器周期包括几个时钟周期。

D、一个指令周期包括几个时钟周期,一个时钟周期包括几个机器周期。

3、属于数据寄存器组的寄存器是 CA、AX,BX,CX,DSB、SP,DX,BP,IPC、AX,BX,CX,DXD、AL,DI,SI,AH4、微型计算机的ALU部件是包含在 D 之中。

A、存贮器B、I/O接口C、I/O设备D、CPU5、在8086和8088汇编语言中,一个字能表示的有符号数的范围是 BA、-32768≤n≤32768B、-32768≤n≤32767C、-65535≤n≤65535D、-65536≤N≤655356、80386微型计算机是32位机,根据是它的 D 。

A、地址线是32位B、数据线为32位C、寄存器是32位的D、地址线和数据线都是32位7、某数存于内存数据段中,已知该数据段的段地址为2000H,而数据所在单元的偏移地址为0120H,该数的在内存的物理地址为( B )A.02120H B.20120H C.21200H D.03200H8、在存贮器读周期时,根据程序计数器PC提供的有效地址,使用从内存中取出( D )A.操作数 B.操作数地址 C.转移地址 D.操作码9、8086/8088系统中,对存贮器进行写操作时,CPU输出控制信号有效的是( A )A.W/IO=1, WR=0B. WR=1C.M/IO=0, RD=0D.RD=010、在8086/8088微机系统中,将AL内容送到I/O接口中,使用的指令是( D )A.IN AL,端口地址B.MOV AL,端口地址C.OUT AL,端口地址D.OUT 端口地址,AL1、B2、C3、C4、D5、B6、D7、B8、D9、A 10、D1.微处理器内部结构由哪些部件组成?答案:微处理器由两部分组成,总线接口单元和执行单元2.论述指令周期、机器周期和时钟周期间的关系。

、答:(1).执行一条指令所需要的时间称为指令周期;(2).一个CPU同外部设备和内存储器之间进行信息交换过程所需要的时间称为总线周期;(3).时钟脉冲的重复周期称为时钟周期;(4).一个指令周期由若干个总线周期组成,一个总线周期又由若干个时钟周期组成;(5). 8086CPU的总线周期至少由4个时钟周期组成;(6).总线周期完成一次数据传输包括:传送地址,传送数据;(7)等待周期----在等待周期期间,总线上的状态一直保持不变;(8)空闲周期----总线上无数据传输操作3.试比较8086CPU与8086CPU的异同之处。