CADENCE全定制IC设计流程图

Cadence原理图绘制流程

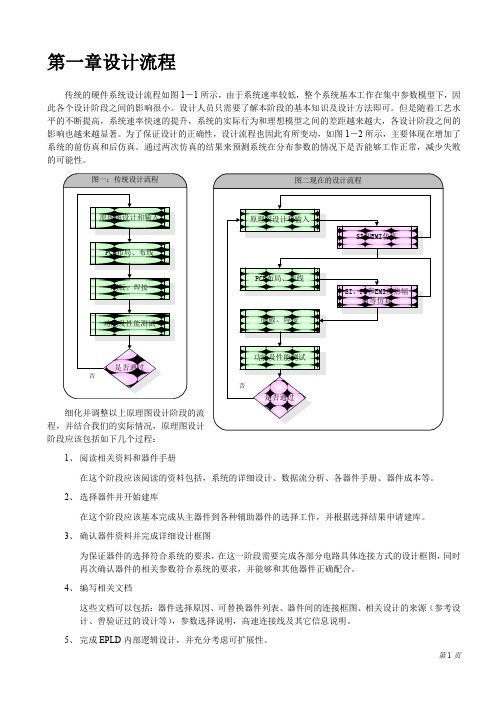

第一章设计流程传统的硬件系统设计流程如图1-1所示,由于系统速率较低,整个系统基本工作在集中参数模型下,因此各个设计阶段之间的影响很小。

设计人员只需要了解本阶段的基本知识及设计方法即可。

但是随着工艺水平的不断提高,系统速率快速的提升,系统的实际行为和理想模型之间的差距越来越大,各设计阶段之间的影响也越来越显著。

为了保证设计的正确性,设计流程也因此有所变动,如图1-2所示,主要体现在增加了系统的前仿真和后仿真。

通过两次仿真的结果来预测系统在分布参数的情况下是否能够工作正常,减少失败的可能性。

细化并调整以上原理图设计阶段的流程,并结合我们的实际情况,原理图设计阶段应该包括如下几个过程:1、 阅读相关资料和器件手册在这个阶段应该阅读的资料包括,系统的详细设计、数据流分析、各器件手册、器件成本等。

2、 选择器件并开始建库在这个阶段应该基本完成从主器件到各种辅助器件的选择工作,并根据选择结果申请建库。

3、 确认器件资料并完成详细设计框图为保证器件的选择符合系统的要求,在这一阶段需要完成各部分电路具体连接方式的设计框图,同时再次确认器件的相关参数符合系统的要求,并能够和其他器件正确配合。

4、 编写相关文档这些文档可以包括:器件选择原因、可替换器件列表、器件间的连接框图、相关设计的来源(参考设计、曾验证过的设计等),参数选择说明,高速连接线及其它信息说明。

5、 完成EPLD 内部逻辑设计,并充分考虑可扩展性。

在编写相关文档的的同时需要完成EPLD内部逻辑的设计,确定器件容量及连接方式可行。

6、使用Concept-HDL绘制原理图7、检查原理图及相关文档确保其一致性。

以上流程中并未包括前仿真的相关内容,在设计中可以根据实际情况,有选择的对部分重要连线作相关仿真,也可以根据I/O的阻抗,上升下降沿变化规律等信息简单分析判断。

此流程中的各部分具体要求、注意事项、相关经验和技巧有待进一步完善。

第二章Concept-HDL的使用运行Concept-HDL后将会出现类似如下界面。

cadence教程-IC设计工具原理共页课件 (一)

cadence教程-IC设计工具原理共页课件 (一) CADENCE教程-IC设计工具原理共页课件作为一名IC设计工程师,必须要掌握各种IC设计工具。

Cadence是业内最受欢迎的EDA(电子设计自动化)软件之一,广泛应用于IC和系统级芯片设计。

这篇文章将介绍Cadence教程——IC设计工具原理共页课件,帮助初学者更好地了解这款软件。

一、课程内容该课程共分为六个部分,从IC设计的基础知识开始,逐步深入讲解Cadence软件的使用和原理。

1. IC设计的基础知识该部分主要介绍集成电路的概念、IC设计的基本流程、ASIC和FPGA的区别等内容,帮助学习者更好地了解IC设计的基本知识。

2. Cadence软件的安装和配置该部分教授如何安装、配置Cadence软件,学习者将了解如何正确设置工作目录、环境变量等,以便进行后续的IC设计工作。

3. Cadence软件的基本流程该部分主要介绍Cadence软件的基本使用流程,包括创建项目、编辑电路图、绘制版图、进行仿真等,重要的是学习者将学会如何创建一个完整的设计流程。

4. Cadence软件的高级应用该部分讲解Cadence软件的高级应用,包括使用脚本自动化设计、使用Verilog语言、进行DC分析、进行静态时序分析等内容,让学习者掌握Cadence软件更加深入的应用。

5. Cadence软件的Debug该部分介绍如何使用Cadence软件进行Debug,掌握Debug技巧,帮助学习者快速找到设计中的问题,并进行修复。

6. 基于Cadence软件的实际设计案例该部分介绍基于Cadence软件的实际设计案例,包括ADC设计、FPGA 设计等,帮助学习者更好地理解设计流程,并将所学知识应用到实践中。

通过以上六个部分,这个Cadence课程全面系统的讲解了IC设计软件工具的使用和原理共页,让学习者更好地了解Cadence软件和IC设计的概念和方法。

二、课程特点1.操作实战:一步步教大家如何使用Cadence软件,操作更为透彻,方便学生理解。

清华大学cadence教程

操作步骤:

执行:CIW->File->Export->Stream… 弹出如下窗口:

33

版图验证工具-Dracula

CADENCE

运行目录

输出文件名 What is this?

34

版图验证工具-Dracula

CADENCE

These two items should be changed according to your design

CADENCE

Cadence设计系统介绍

清华大学微电子所

1

OUTLINE

CADENCE

Cadence 系统概述 版图设计工具-Virtuoso LE

版图验证工具-Diva

版图验证工具-Dracula

2

设计流程

CADENCE

3

版图验证

CADENCE

版图验证的必要性?

确保版图绘制满足设计规则 确保版图与实际电路图一致 确保版图没有违反电气规则 可供参数提取以便进行后模拟

Checking Limit 可以选择检查哪一部分的版图:

Full 表示查整个版图 Incremental 查自从上一次DRC检查以来,改变的版图。 by area 是指在指定区域进行DRC检查。一般版图较大时,可以分块 检查。

15

版图验证工具-DIVA

CADENCE

Switch Names

在DRC文件中,我们设置的switch在这里都会出现。这个选项可 以方便我们对版图文件进行分类检查。这在大规模的电路检查中 非常重要。

41

Dracula-DRC

CADENCE

42

Dracula-LVS

CADENCE

CADENCE全定制IC设计流程图

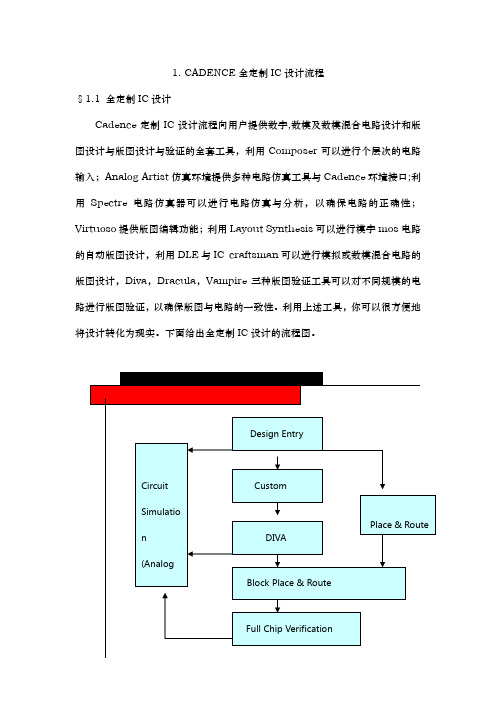

1. CADENCE全定制IC设计流程§1.1 全定制IC设计Cadence定制IC设计流程向用户提供数字,数模及数模混合电路设计和版图设计与版图设计与验证的全套工具,利用Composer可以进行个层次的电路输入;Analog Artist仿真环境提供多种电路仿真工具与Cadence环境接口;利用Spectre电路仿真器可以进行电路仿真与分析,以确保电路的正确性;Virtuoso提供版图编辑功能;利用Layout Synthesis可以进行模字mos电路的自动版图设计,利用DLE与IC craftsman可以进行模拟或数模混合电路的版图设计,Diva,Dracula,Vampire三种版图验证工具可以对不同规模的电路进行版图验证,以确保版图与电路的一致性。

利用上述工具,你可以很方便地将设计转化为现实。

下面给出全定制IC设计的流程图。

2.Cadence cdsSPICE 的使用说明Cadence cdsSPICE 也是众多使用SPICE 内核的电路模拟软件之一。

因此他在使用上会有部分同我们平时所用到的PSPICE 相同。

这里我将侧重讲一下它的一些特殊用法。

§ 2-1 进入Cadence 软件包一.在工作站上使用在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键),其中& 表示后台工作。

Icfb 调出Cadence 软件。

出现的主窗口如图2-1-1所示: 图 2-1-1Candence 主窗口二.在PC 机上使用1)将PC 机的颜色属性改为256色(这一步必须);2)打开Exceed 软件,一般选用xstart 软件,以下是使用步骤:start method 选择REXEC (TCP-IP ) ,Programm 选择Xwindow 。

Host 选择10.13.71.32 或10.13.71.33。

host type 选择sun 。

集成电路版图设计cadence设计流程

集成电路版图设计cadence设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!集成电路版图设计的Cadence设计流程详解集成电路(IC)版图设计是半导体行业中至关重要的环节,它直接影响到芯片的性能、功耗和可靠性。

Cadence原理图库和PCB库的设计与流程PPT精选文档

➢直接新建元件

① 新建元件

有几个part的元件符号是否相同

.5

Alias Names

元件别名: 对于新建元件,我们可以赋予它多个别名,新建的元件及其别名均出现在库文件中,

它们除了名称(对应于电路图中元件的part value值)不同外,其它方面均相同。

.6

Attach Implementation

.22

➢ Allegro 封装库与Protel PCB封装库的比较

最大的不同就是对焊盘的管理及调用方式不一样,Protel每一个封装有自己焊盘, Allegro里的焊盘是可以对应多个器件的,以库的形式管理。

{PAD_1,PAD_2,…PAD_n}

PAD

这种管理方式的优点是占用的资源比较少,当要批量更新焊盘的时候只要更 新PAD库里的焊盘,再刷新一下电路板就ok,这就是为什么用Allegro打开PCB会 比用Protel快的原因,资源是一点点省下来的。

元件的关联关系。 c) XXX.txt:Device文件,记录了该元件分类,针对集成IC、连接器IO及分立元件

有不同的功能定义,可交换管脚,及仿真需要的一些信息记录在此。

注:默认保存dra文件时,psm自动建立,当在把Drawing配置变 量:no_symbol_onsave设为1时,则需手动create psm文件,Device 文件需手动选类型并创建。

.35

➢封装库的建库方法

通过向导来创建: ⒐ 概括了下前面的设置。 ⒑ 设置完成后生成如下图元件符号。(注:向导不能添加中间的接

地大焊盘,需手工添加,完成最终的元件如右图)。

.36

➢封装库的建库方法

通过向导来创建: ⒒ 生成PSM文件,和Device文件。

Candence集成电路版图设计报告

目录一、实验目的: (2)二、实验工具: (2)三、设计规则: (2)1. 版图设计的内容: (2)2. 设计规则(Design Rule ): (2)四、实验原理: (5)1.CMOS反相器工作原理 (5)2.三级反相器工作原理 (5)3.电流镜工作原理 (6)4.差分放大电路 (6)5.基准电压源电路 (7)五、实验内容: (7)1.CMOS反相器 (7)2.三级反相器 (8)3.电流镜 (8)4.差分放大电路 (8)5.基准电压源电路 (8)六、原理图和版图绘制结果: (9)七、版图设计与绘制的总结: (9)1.设计方法、技巧以及要注意的问题 (9)2.心得体会 (9)参考文献 (10)附录 ................................................................................................................... 错误!未定义书签。

一、一、实验目的:1.在Linux系统下熟悉IC设计软件Cadence Virtuoso的使用方法。

2.掌握集成电路基本单元的原理图设计、版图设计的流程方法以及技巧。

然后对其进行基本的DRC检查和LVS检查。

二、实验工具:3.Virtuoso三、设计规则:1. 版图设计的内容:①布局:安排各个晶体管、基本单元、复杂单元在芯片上的位置。

②布线:设计走线,实现管间、门间、单元间的互连。

③尺寸确定:确定晶体管尺寸(W、L)、互连尺寸(连线宽度)以及晶体管与互连之间的相对尺寸等。

④版图编辑(Layout Editor ):规定各个工艺层上图形的形状、尺寸和位置。

⑤布局布线(Place and route ):给出版图的整体规划和各图形间的连接。

⑥版图检查(Layout Check ):设计规则检验(DRC,Design Rule Check)、电气规则检查(ERC,Electrical Rule Check)、版图与电路图一致性检验(LVS,Layout Versus Schematic )。

CADENCE全定制IC设计流程

CADENCE全定制IC设计流程CADENCE是一种广泛应用于集成电路(IC)设计的软件工具。

它提供了完整的设计流程和工具,用于设计、验证和制造IC芯片。

在基于CADENCE的全定制IC设计流程中,在IC设计的每个阶段都使用到了CADENCE工具套件,包括电路和物理设计工具、模拟和数字仿真工具、布图工具以及物理验证工具等。

下面是使用CADENCE进行全定制IC设计的一般流程:1.设计需求分析:根据所需的功能和性能需求,进行设计需求分析。

这包括确定电路拓扑结构、电路规范和性能指标等。

2. 电路设计:使用CADENCE中的Schematic设计工具,绘制电路原理图。

根据设计需求,选择合适的电子元件并进行电路布线。

使用CADENCE的仿真工具,验证电路的功能和性能。

3.物理设计:将电路原理图转换为布局图。

使用CADENCE的布局工具,在设计规范的限制下进行器件布局和连线布线。

这包括选择合适的器件大小和排列方式,以优化电路性能和功耗。

4.物理验证:使用CADENCE的物理验证工具,对电路布局进行验证。

这包括电路的电性能分析、功耗分析、时序等效验证以及电磁兼容性分析等。

根据验证结果进行布局优化和改进。

5.交互测试:将设计与其他模块和子系统进行集成测试。

使用CADENCE的模拟工具和数字仿真工具,对整个系统进行功能验证和性能评估。

7.物理制造:通过CADENCE的布局生成工具,生成用于物理制造的设计数据库文件。

这包括物理制造规则检查、填充、光刻掩膜生成等。

8.物理验证:使用CADENCE的物理验证工具,对物理制造的设计进行验证。

这包括工艺模拟、功耗分析、封装和信号完整性分析等。

9.物理制造:将设计数据库文件发送给制造厂商进行实际制造。

这包括掩膜制造、芯片加工、封装和测试等。

10.性能评估:对实际制造的芯片进行性能评估和测试。

使用CADENCE的集成测试工具,进行功能测试、速度测试和功耗测试等。

11.系统集成:将IC芯片集成到目标系统中,并进行系统级测试和验证。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1. CADENCE全定制IC设计流程§1.1 全定制IC设计Cadence定制IC设计流程向用户提供数字,数模及数模混合电路设计和版图设计与版图设计与验证的全套工具,利用Composer可以进行个层次的电路输入;Analog Artist仿真环境提供多种电路仿真工具与Cadence环境接口;利用Spectre电路仿真器可以进行电路仿真与分析,以确保电路的正确性;Virtuoso 提供版图编辑功能;利用Layout Synthesis可以进行模字mos电路的自动版图设计,利用DLE与IC craftsman可以进行模拟或数模混合电路的版图设计,Diva,Dracula,Vampire三种版图验证工具可以对不同规模的电路进行版图验证,以确保版图与电路的一致性。

利用上述工具,你可以很方便地将设计转化为现实。

下面给出全定制IC设计的流程图。

2.Cadence cdsSPICE 的使用说明Cadence cdsSPICE 也是众多使用SPICE 核的电路模拟软件之一。

因此他在使用上会有部分同我们平时所用到的PSPICE 相同。

这里我将侧重讲一下它的一些特殊用法。

§ 2-1 进入Cadence 软件包一.在工作站上使用在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键),其中& 表示后台工作。

Icfb 调出Cadence 软件。

出现的主窗口如图2-1-1所示:图 2-1-1Candence 主窗口二.在PC 机上使用1)将PC 机的颜色属性改为256色(这一步必须);2)打开Exceed 软件,一般选用xstart 软件,以下是使用步骤:start method 选择REXEC (TCP-IP ) ,Programm 选择Xwindow 。

Host 选择10.13.71.32 或10.13.71.33。

host type 选择sun 。

并点击后面的按钮,在弹出菜单中选择command tool 。

确认选择完毕后,点击run !3)在提示符ZDASIC22> 下键入:setenv DISPLAY 本机ip:0.0(回车)4)在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键)即进入cadence 中。

出现的主窗口如图1-1-1所示。

以上是使用xstart 登陆cadance 的方法。

在使用其他软件登陆cadance 时,可能在登录前要修改文件.cshrc ,方法如下:1.1 Candence主窗口在提示符下输入如下命令:vi .cshrc↙(进入全屏幕编辑程序vi)将光标移至setevn DISPLAY ZDASIC22:0.0 处,将“ZDASIC22”改为PC 机的IP,其它不变(重新回到服务器上运行时,还需按原样改回)。

改完后存盘退出。

然后输入如下命令: source .cshrc↙(重新载入该文件)以下介绍一下全屏幕编辑程序vi的一些使用方法:vi使用了两种状态,一是指令态(Command Mode),另一是插入态(Insert Mode)。

当vi处于指令态时,打入的容会视作指令来解释;而当vi处于插入态时,就可以打入正文(text)文件;大多数vi指令是单字符的。

由插入态改变为指令态,按〈Esc〉键;而由命令态转为插入态,则可以使用下面的插入令,直接打入,无需再按〈Return〉键。

在vi的指令态下,用h,j,k,l键移动光标,具体如下:h——光标左移一个字符;j——光标向下一行;k——光标向上一行;l——光标右移一个字符;以下是一些基本插入命令(须用到的)的用法:i——在光标处插入正文;x——删除光标处的字符;:wq——存盘退出;要记著一点,在插入态处,不能打入指令,必需先按〈Esc〉键,返回指令态。

假若户不知身处何态,也可以按〈Esc〉键,不管处于何态,都会返回指令态其它的一些命令请读者自己参阅有关的书籍。

§ 2-2 建立可进行SPICE模拟的单元文件主窗口分为信息窗口CIW、命令行以及主菜单。

信息窗口会给出一些系统信息(如出错信息,程序运行情况等)。

在命令行中可以输入某些命令。

如我们调用Cadence的命令icfb和一些其它命令,比较重要的有调出帮助文件的openbook&等。

一.File菜单在File菜单下,主要的菜单项有New、Open、Exit等。

在具体解释之前我们不妨先理顺一下以下几个关系。

library(库)的地位相当于文件夹,它用来存放一整个设计的所有数据,像一些子单元(cell)以及子单元(cell)中的多种视图(view)。

Cell(单元)可以是一个简单的单元,像一个与非门,也可以是比较复杂的单元(由symbol搭建而成)。

View则包含多种类型,常用的有schamatic,symbol,layout,extracted,ivpcell等等,他们各自代表什么意思以后将会一一提到。

New菜单项的子菜单下有Library、Cellview两项。

Library项打开New Library窗口,Cellview项打开Create New File窗口,如图1-2-1和1-2-2所示。

图2-2-1 New Library 窗口图2-2-2 Create New File 窗口1)建立库(library):窗口分Library和Technology File 两部分。

Library 部分有Name和Directory两项,分别输入要建立的Library的名称和路径。

如果只建立进行SPICE模拟的线路图,Technology部分选择Don’t need a techfile 选项。

如果在库中要创立掩模版或其它的物理数据(即要建立除了schematic外的一些view),则须选择Compile a new techfile(建立新的techfile)或Attach to an existing techfile(使用原有的techfile)。

2)建立单元文件(cell):在Library Name 中选择存放新文件的库,在Cell Name中输入名称,然后在Tool选项中选择Composer-Schematic工具(进行SPICE模拟),在View Name中就会自动填上相应的View Name——schematic。

当然在Tool工具中还有很多别的工具,常用的象Composer -symbol、virtuoso-layout等,分别建立的是symbol、layout的视图(view)。

在Library path file中,是系统自建的library path file 文件的路径及名称(保存相关库的名称及路径)。

Open菜单项打开相应的Open File窗口,如图2-2-3所示。

在Library Name中选择库名,在Cell Names中选择需要打开的单元名。

Mode 项可以选择打开方式——可编辑状态或者只读状态。

图 2-2-3 Open File窗口Exit项退出Cadence软件包。

二.Tools菜单在Tools菜单下,主要的菜单项有Library Manager、Library Path Editor 等。

Library Manager项打开的是库管理器(Library Manager)窗口,如图1-2-4所示。

图 2-2-4 Library Manager窗口在窗口的各部分中,分别显示的是Library、Category、Cell、View相应的容。

双击需要打开的view名(或同时按住鼠标左右键从弹出菜单中选择Open 项)即可以打开相应的文件。

同样在library manager中也可以建立library 和cell。

具体方法是点击file,在下拉菜单中选择library或cell即可。

Library Path Editor项打开的是Library Path Editor窗口,如图2-2-5 所示。

从File菜单中选择Add Library项,填入相应的库名和路径名,即可包括入相应的库。

图 2-2-5 Library Path Editor窗口三.Technology File菜单这个菜单中的最后一项Edit Layers 可以使用在版图编辑中,用来修改原始图层的一些属性。

选择主窗口的File→Open→Open file,打开相应的文件,即进入了Composer-Schematic Editing窗口,如图1-3-1所示。

窗口左边的按钮分别(从上到下)为Check and Save(检查并存盘)、Save(存盘)、Zoom out by 2(放图 2-3-1 Composer-Schematic Editing窗口大两倍)、Zoom in by 2(缩小两倍)、Stretch(延伸)、Copy(拷贝)、Delete (删除)、Undo(取消)、Property(属性)、Component(加元件)、Wire(Narrow)(画细线)、Wire(Wide)(画粗线)、Pin(管脚)、Cmd options、Repeat(重复),这些分别可以在菜单中找到相应的菜单项。

选择Add/Component菜单,打开相应添加元件的窗口,如图1-3-2所示。

点击Browse,会弹出library manager窗口,一些常用的元器件都在Analoglib 库中。

View Name一般选择symbol,instance Names不用自己填,系统会自己加上去。

添加完元件后需设定元件的模型名称(如果必须的话)以及一些参数的值,特别是mos管和三极管,一定要填model name,图 1-3-2 添加元件窗口否则在模拟时会出错(我们一般使用华晶的元件model)。

填好后,就可以将元件添加到Editing的编辑窗口中去了。

其它的一些连线、移动、删除、复制的操作和一般的EDA工具差不多,这儿就不一一再说了。

还有一点要提到的是,对于交叉相连的两条线,系统会有警告,可对连线稍作修改去除这个警告。

注:以下是一些常用的快捷键:i——添加元件,即打开添加元件的窗口;[——缩小两倍;]——扩大两倍;w——连线(细线);f——全图显示;p——查看元件属性。

从一种状态转为另一种状态,按escape,或直接点击图标或使用快捷键。

为了使电路图更加明了,一般在电路的输入输出部分加上pin脚。

这在后面的例子中将会提到。

§ 2-4 模拟的设置(重点)Composer-schamatic界面中的Tools→Analog Artist项可以打开Analog Artist Simulation图 2-4-1 Analog Artist Simulation窗口窗口,如图2-4-1 所示。