于博士Cadence视频教程原理图设计pdf

cadencePCB画图(傻瓜教程快速入门)

cade nee画PCB板傻瓜教程(转帖)一.原理图1.建立工程与其他绘图软件一样,OrCAD以Project来管理各种设计文件。

点击开始菜单,然后依次是所有程序一打开cade nee软件一》一般选用Design Entry CIS点击Ok 进入Capture CIS接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。

2.绘制原理图新建工程后打开的是默认的原理图文件SCHEMATIC1PAGE,1右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel 类似。

点击上侧工具栏的Project manager (文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。

1)修改原理图纸张大小:双击SCHEMATIC文件夹,右键点击PAGE1选择Schematic1Page Properties,在Page Size中可以选择单位、大小等;2)添加原理图库:File--New--Library,可以看到在Library 文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘;(注意:在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过,没法对齐,连不上线!)3)添加新元件:常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。

右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadshee,t 后者以表格的方式建立新元件,对于画管脚特多的芯片兀件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。

于博士candence视频说明

1.文件的创建一.原理图的设计2.元器件的创建13.元器件的创建2:分两部分画的元器件4.电路图中如何区分多个由两个部分组成的元器件如何分组。

5.元件库的导入及放置元器件:电容电阻在库DISCRETE里6.连线:NET同页面的链接不同页面不用这个7.总线连接方式,页面间的连线8.编辑,修改原理图,查找搜索元件,网络,等等。

9.搜索特定元器件:如电源,线,元件等10.替换元件,元件属性的编辑11.元件的拖动,镜像。

12.元件属性,值的修改,添加文本,放置黑框。

13.添加封装14.生成网表15.生成元件清单,打印初图二、高速电路设计:电路是设计出来的,不是仿真出来的。

16、正确对待经验,如何快速积累经验,设计流程17、工具介绍,18、PCB EDITOR:各个基本命令19、class subclass20、封装,IPC网站,PCBM软件(电容封装)(一)表贴类21、管脚,丝印层,。

封装画法,(多管脚封装)22、创建自定义图形焊盘1)、建立图形文件2)、利用图形文件创建焊盘23、将焊盘,等前面画的应用起来,画整个元件的封装。

24、元件四面都有管脚,方向不同,大小相同:焊盘建好后建封装(二)通孔类焊盘,封装25、焊盘,通过cadence自带的封装建立封装,flash焊盘26、非电气属性元件:(三)电路板的建立27、初步建立电路板:板宽,布线区域28、层叠结构29、布局前的准备工作:导入网表。

30、元件摆放,布局:手工摆放、镜像摆放、旋转31、原理图与PCB交互布局(按功能单元)32、按原理图页面进行摆放33、PCB中按room布局34、在原理图中设置room,通过网表传递,在PCB中按room布局35、快速摆放36、元件摆放布局的注意事项,(四)、线宽和线距37、约束规则的设置界面38、单根网络约束规则的具体设置:1设置好线宽;2找到网络,赋予属性;3把约束赋给网络属性39、工程中哪些网络需要设置,特殊线距线宽40、特殊区域,约束规则的设置:不符合网络约束规则的设置41、总线设置,线中有电阻电容,通过xnet来显示42、创建网络的拓扑结构/拓扑约束(一)43、建立拓扑约束(二)44、设置走线长度的约束规则45、设置相对传播延迟(等长设置)46、设置差分对(五)、布线47、布线前的准备工作:设置电源地线,使线看起来清水一点;不同网络,不同颜色高亮48、布线:扇出,fanout操作,引脚拉出一条线,打个过孔49、布线:手工布线:单个网络拉线50、手工拉线的几种方式51、总线方式的布线,群组走线52、高速信号布线的信息显示的问题53、边缘耦合差分对布线方法54、带有T型连接点的布线、蛇形走线(六)铺铜的工作55、铜皮56、铜皮内垫层的分割57、在PCB里给元件重新编号,布线后的检查,数据库检查58、生成丝印,加文字说明59、和钻孔文件相关的操作60、光绘文件。

cadence教程-IC设计工具原理共页课件 (二)

cadence教程-IC设计工具原理共页课件 (二) - Cadence教程-IC设计工具原理共页课件

1. 什么是Cadence?

Cadence是一家专门从事电子设计自动化软件的公司。

其产品涵盖了芯片设计、系统设计、封装设计和PCB设计等领域。

Cadence的软件被广泛应用于半导体、通信、计算机、消费电子等行业。

2. Cadence的主要产品

Cadence的主要产品包括Virtuoso、Allegro、OrCAD、Sigrity等。

其中,Virtuoso是一款用于模拟、布局和验证芯片的工具;Allegro是

一款用于PCB设计的工具;OrCAD是一款用于电路设计的工具;

Sigrity则是一款用于信号完整性分析的工具。

3. Cadence的应用领域

Cadence的软件被广泛应用于各种电子产品的设计和制造中,如手机、平板电脑、笔记本电脑、服务器、网络设备、汽车电子、医疗设备等。

在半导体行业中,Cadence的软件被用于设计各种芯片,如处理器、存储器、模拟集成电路、射频集成电路等。

4. Cadence的优势

Cadence的软件具有高度的可靠性、灵活性和易用性。

其产品支持多种操作系统,如Windows、Linux、Solaris等。

此外,Cadence还提供了丰富的教程和技术支持,帮助用户更好地使用其软件。

5. Cadence的未来发展

随着电子行业的不断发展,Cadence的软件也在不断升级和改进。

未来,Cadence将继续加强与各大芯片厂商和设备厂商的合作,开发出更加先进和适用的软件,为电子行业的发展做出更大的贡献。

Cadence教程(D422)PDF.pdf

规定:本实验教材中红色为键入命令或字符,兰色为菜单项,紫色为键盘功能键;“单击”指鼠标左键按下一次。

实验一、Virtuoso Schematic Editor实验目的:掌握电原理图(schematic)设计输入方法。

[1]启动IC Design 软件:首先,登陆Linux,在username文件夹中建立一个你命名的文件夹,然后在Terminal窗口中进入这个文件夹,在该文件夹目录下输入:icfb&,(这样,你在cadence中做的一切工作都会自动保存在这个文件夹中,如果直接icfb&的话,会导致你的工作成果,例如:电路图、仿真结果等,会在/home中保存,影响其他人的使用)[2]建立新库、新单元以及新视图(view):首先,输入icfb&后,出现下图窗口在图中CIW窗口中依次打开:Tools->Library Manager,出现下图窗口:在图中窗口中依次打开:File->New->Library,出现下图窗口:输入Library Name:test,然后点OK。

(注意下面的保存路径就是你第一步建立的文件夹)出现下一个窗口:选中Attach to an existing techfile,然后OK。

出现下一个窗口:选中右下方Technology Library:chrt35dg_SiGe,然后OK。

下面我们来画一个nand2电路。

选中左侧的test,在Library Manager 窗口,File->New->Cellview,如下图:在弹出的“Create New File”窗口Cell Name栏中,nand2 Tool栏中,选Composer-SchematicOK,如下图[3]添加元件(实例instance)在弹出的“Virtuos o Schematic Editing:…”窗口中,左边为工具栏,选instance 图标(或i)单击“Add instance”窗口Library栏最右侧Browser,弹出“Library Browser-…”窗口,Library选chrt35dg_SiGe,Cell选nmos_3p3, View选symbol鼠标回到“Add instance”窗口,Model name栏:nmos_3p3, width(Total Width): 3.0u , Length: 0.5u,Hide 如下图在“Virtuoso Schematic Editing:…”窗口, 鼠标左键单击一次,间隔一定距离再单击一次,这样就增加了2个nmos元件,ESC(试一试:先选中一个元件,再q ,查看/改变属性)。

于博士Cadence视频教程原理图设计pdf文档

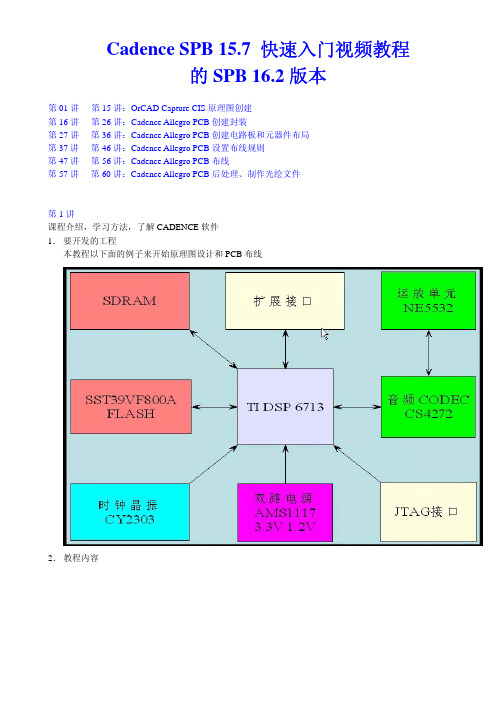

第 01 讲 - 第 15 讲:OrCAD Capture CIS 原理图创建 第 16 讲 - 第 26 讲:Cadence Allegro PCB 创建封装 第 27 讲 - 第 36 讲:Cadence Allegro PCB 创建电路板和元器件布局 第 37 讲 - 第 46 讲:Cadence Allegro PCB 设置布线规则 第 47 讲 - 第 56 讲:Cadence Allegro PCB 布线 第 57 讲 - 第 60 讲:Cadence Allegro PCB 后处理、制作光绘文件 第1讲 课程介绍,学习方法,了解 CADENCE 软件 1. 要开发的工程

:点击 Toolbar 或者:菜单:Place/Ellipse 画椭圆,如下图:

下面填充第一个椭圆 左键选取第一个椭圆,右键点击,如下图:

点击 Edit Properties,弹出下图: 选择填充式样,如下图:

点击 OK,如下图:

两个椭圆顶点画线 :Toolbar,或 Place/Line,如下图:

第2讲 创建工程,创建元件库 1. 必要的设置

菜单:Options/Design Template,如下图:

点击后,如下图:

这是设计时采用的一个模板,将一些通用的在这里设置,会方便以后的工作 2. 创建工程文件

菜单:File/New/Project,如下图:

点击后,弹出下图:

几点说明:

:命名工程的文件名 :指定存储路径

理图中所使用的元器件的一个拷贝),如下图:

Library:存放原理图中使用的元件库,也可以在另外位置把元件库加进来 Output:存放对原理图操作时,生成的一些文件 下图是工程管理器全图:

Cadence--原理图的设计

4、更新元件编号 在设计过程中,某

些元件可能被删除, 又有一些元件被添 加,所以元件的编 号可能有些混乱, 所以通常要进行重 新编号。 我们在项目窗口中, 选择工程文件,然 后点击 “Tools→Annotate…” 菜单,这时弹出如 下对话框:

为了更新元件编号,通常要把现有的元件编号统统

择“Check design rules”选项,如果要去掉图纸上的 DRC检验标记,应该选择“Delete existing DRC marker”。在“Report”栏目上,选择要进行的项 目。点击“确定”按钮后,就开始了DRC检验。 DRC检测结果:

6、生成网络表 在项目窗口中,选择工程文件,然后点击

5、进行DRC检验

进行DRC检验(即Design Rules Check),检查在我们

的设计中,有哪些错误,对可能出现的问题,也会 提出警告。

在项目窗口中,选择工程文件,然后点击

“Tools→Design Rules Check…”菜单,这时弹出如下 对话框:

如果要进行DRC检验,在“Action”栏目中应该选

在该对话框中,可以选把修改的结果去更新当前选中的元

件、把修改的结果去更新所有同型号元件、或修改作废。

3、添加封装属性 我们绘制原理图的目的之一就是生成网络表,而生成

网络表之前必须给每个元件都加上相应的封装属性。 双击元件打开属性编辑器。如果对话框的“PCB Footprint”一栏是空的,可以直接进行添加,如J1的封 装为“conn6xx”。

有两个列表框:在左边的列表框中列出可以作为元

件清单的栏目项;右边的列表框中是目前选中作为 元件清单的栏目项,应根据自己的需要调整该列表 框中的栏目项,最后点击“OK”,从而生成元件 清单。

第二章Cadence的原理图设计

第二章C adence的原理图设计2.1Design Entry CIS软件概述Cadence软件系统有两套电路原理图的设计工具,一套是Design Entry HDL,另一套就是我们马上要开始学习的Design Entry CIS。

其中Design Entry HDL是Cadence公司原本的原理图设计软件,可以用于芯片电路和板级电路的设计,其长处在于可以把芯片的电路原理图和板级电路原理图结合在一起,进行综合设计;而Design Entry CIS主要用于常规的板级电路设计,Design Entry CIS原本是OrCAD公司的产品,OrCAD公司后来被Cadence公司收购,于是Design Entry CIS也就成了Cadence公司的另一套电路原理图设计软件。

Design Entry CIS原理图设计软件的特点是直观、易学、易用,在业界有很高的知名度,利用Design Entry CIS原理图设计软件可以进行简单的(只有单张图纸构成的)电路原理图设计,也可以进行(由多张图纸拼接而成的)平坦式电路原理图设计,还可以进行(多张图纸按一定层次关系构成的)层次式电路原理图设计。

在本章中,我们首先学习简单的电路原理图设计,然后再学习较为复杂的平坦式和层次式电路原理图设计。

我们将围绕一块非常简单的STC系列单片机下载电路板,学习简单电路原理图的设计,同时在此过程中,还将学习到USB转UART串行口、STC系列单片机下载电路等方面的知识。

接着,我们将围绕一块ARM-7核心实验板,进行平坦式和层次式电路原理图的设计,而该核心板是配套于ARM-7实验箱。

在此过程中我们还将学习到嵌入式技术等方面的知识。

2.2初识Design Entry CIS一.启动Design Entry CIS我们在电脑上点击“开始→所有程序→Cadence SPB16.2→Design Entry CIS”,如下图所示:这时将弹出如下对话框:图2-2选择工作内容在这里我们选择“OrCAD Capture CIS”一项,点击“OK”按钮后,就实际启动了DesignEntry CIS,出现如下界面:图2-3OrCAD Capture CIS软件界面与大多数软件一样,OrCAD Capture CIS软件也是以项目方式管理我们的设计文件的,所以我们将首先要新建一个项目:在窗体上点击“File→New→Project”出现如下对话框:图2-4新建项目在“Name”中输入项目名称,“Location”中输入项目文件的存放位置(最好给每一个项目建立一个文件夹,把项目中的所有文件都放入该文件夹),在“Create a New Project Using”栏目中,选择“Schematic”(因为我们要进行电路原理图的设计)。

cadence软件基本原理图设计指导培训

9、INDUCTOR(电感) 10、MEMORY(存储器) 11、MICROPROCESSOR(微处理器) 12、OPTICAL_TRANSMITTER_MODULE(光传

输模块) 13、OPTOISOLATOR(光电耦合器) 14、POWER(电源模块) 15、RELAY(继电器) 16、RESISTOR(电阻)

二、原理图设计的基本流程

方案设计

器件选型

申请原理图库

初始化设置

创建proБайду номын сангаасect

库映射及调用

原理图设计

原理图check

原理图评审

pcb设计

pcb设计申请 毛坯图确认

申请毛坯

一、Cadence软件介绍 二、原理图设计基本流程 三、典型project的目录结构 四、原理图库相关 五、原理图设计相关(before/after) 六、原理图设计技巧及常见问题解决

17、SPECIAL_IC(专用器件) 18、SWITCH(开关) 19、TP_JP(测试点和跳针) 20、TRANSFORMER(变压器) 21、TRANSISTOR(晶体管) 22、OTHERS(其它)

原理图库所包含的信息

1、PARTCODE--物料号 2、PARTVALUE--器件型号 3、 JEDEC_TYPE--器件封装 4、 $LOCATION--器件位号 5、 GROUP --器件分组属性 6、 DESCRIPTION--器件描述(封装类型/器件

联系我们:

技术支持: 李军华 87691070 贾建收 87693634 廖 骞 87693634

器件库相关: 潘红英 87691070

原理图设计

原理图设计的初始设置 原理图设计的基本命令及操作 设计层次化原理图 原理图设计注意事项 原理图打印

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cadence SPB 15.7 快速入门视频教程的SPB 16.2版本第01讲 - 第15讲:OrCAD Capture CIS原理图创建第16讲 - 第26讲:Cadence Allegro PCB创建封装第27讲 - 第36讲:Cadence Allegro PCB创建电路板和元器件布局第37讲 - 第46讲:Cadence Allegro PCB设置布线规则第47讲 - 第56讲:Cadence Allegro PCB布线第57讲 - 第60讲:Cadence Allegro PCB后处理、制作光绘文件第1讲课程介绍,学习方法,了解CADENCE软件1.要开发的工程本教程以下面的例子来开始原理图设计和PCB布线2.教程内容3.软件介绍Design Entry CIS:板级原理图工具Design Entry HDL:设计芯片的原理图工具,板级设计不用Layout Plus:OrCAD自带的PCB布线工具,功能不如PCB Editor强大Layout Plus SmartRoute Calibrate:OrCAD自带的PCB布线工具,功能不如PCB Editor强大PCB Editor:Cadence 的PCB布线工具PCB Librarian:Cadence 的PCB封装制作工具PCB Router:Cadence 的自动布线器PCB SI:Cadence 的PCB信号完整性信号仿真的工具SigXplorer:Cadence 的PCB信号完整性信号仿真的工具4.软件列表5.开始学习Design Entry CIS启动:Start/Cadence SPB 16.2/Design Entry CIS启动后,显示下图:里面有很多选项,应该是对应不同的License本教程使用:OrCAD Capture CIS我个人认为:Allegro PCB Design CIS XL是所有可选程序中,功能最强大的,但不知道,强在哪里;而且本教程的原理图文件可以使用上表中不同的程序打开6.选择OrCAD Capture CIS,启动后显示下图File/Open/Project,如下图:选择一个project,打开后,如下图:左边是工程管理器窗口中间是原理图页面窗口右边是工具条下面是Session Log窗口,用以记录一些关键的操作,是一个日至文件工程管理器窗口的内容说明:.dsn文件:是一个工程的数据库文件,该数据库包含:Schematic(原理图文件)和Design Cache(存放原理图中所使用的元器件的一个拷贝),如下图:Library:存放原理图中使用的元件库,也可以在另外位置把元件库加进来Output:存放对原理图操作时,生成的一些文件下图是工程管理器全图:下面介绍菜单系统OrCAD Capture CIS的菜单是上下文相关的,也就是说:点击不同的窗口,菜单是不同的OrCAD Capture CIS的工具条也是上下文相关的,也就是说:点击不同的窗口,工具条是不同的8.工程管理窗口中的原理图页面的创建、删除和重命名操作8.1原理图页面的创建方法1:首先选择Schematic文件夹,如下图:在菜单上选择:Design/New Schematic Page,如下图:点击后,弹出对话框:输入名字,点击OK,则新建的名字出现在Schematic文件夹下,比如:输入1,如下图:方法2:首先左键选择Schematic,右键点击,弹出下图:点击New Page,弹出下图:输入2,点击OK,如下图:8.2 删除方法1:首先,选择想删除的页面,比如1,如下图:在菜单上,Design/Delete,如下图:方法2:选择想删除的页面,比如2,如下图:直接按键盘上的Delete键8.3 重命名与创建和删除一样,有两种方法,参照创建和删除即可9.原理图页面窗口中的操作:原理图的显示、放大、缩小和滚动9.1 放大、缩小的方法方法1:放大:按键盘的I (Zoom I n)缩小:按键盘的O (Zoom O ut)放大、缩小时,以光标为中心进行方法2:菜单:View/Zoom方法3:在原理图页面上,点击右键,选择Zoom In/Zoom Out方法4:按住Ctrl键,鼠标的滚轮向下转动,缩小,鼠标的滚轮向上转动,放大9.2 上下滚动方法1:使用滚动条方法2:使用Page up和Page down方法3:鼠标的滚轮向下或向上9.3 左右滚动按住Ctrl键,再按Page up:向左按住Ctrl键,再按Page down:向右第2讲创建工程,创建元件库1.必要的设置菜单:Options/Design Template,如下图:点击后,如下图:这是设计时采用的一个模板,将一些通用的在这里设置,会方便以后的工作2.创建工程文件菜单:File/New/Project,如下图:点击后,弹出下图:几点说明::命名工程的文件名:指定存储路径:选定project的类型,右侧有说明,通常选最后一个即可比如:输入:dsp6713system,指定路径后,点击OK,如下图:软件自动建立一个Page1原理图,可以重新命名下面修改原理图窗口的背景颜色菜单:Options/Preferences,如下图:点击后,弹出下图:点击Background左边的白色框,弹出色板,选择你喜欢的颜色作为背景,如下图:点击两次OK,返回,看一下效果:如果创建工程前,没有进行设置,现在可以设置方法1:使用1所用的方法设置方法2:Options/Schematic Page Properties,如下图:点击后,弹出下图:可以进行图纸尺寸等等设置3.创建(原理图)元件库在OrCAD Capture CIS中创建一个元件库,File/New/Library,如下图:在OrCAD Capture CIS中,元件库也是以工程方式来组织的,点击后,如下图:创建一个新元件库时,程序自动建立了文件名及路径,改变文件名及路径的方法如下:方法1:左键点击元件库(.olb),然后,File/Save as,如下图:指定文件名和路径方法2:左键点击元件库(.olb),然后,右键点击,如下图:点击后,在弹出的图中,选择路径,命名文件名,然后点击OK,如下图:4.创建元件方法1:左键点击元件库(.olb),然后,Design/New Part,如下图:方法2:左键点击元件库(.olb),然后,右键点击,如下图:点击后,弹出下图:我们以时钟芯片CY2303为例,在Name栏输入:CY2303,其它的不变,点击OK,如下图:下图是时钟芯片CY2303的资料:下面根据时钟芯片CY2303的资料,创建CY2303的元件库方法1:一个pin一个pin的放置可以采用Toolbar,如下图:或采用菜单Place/Pin,如下图:点击后,根据CY2303的资料输入Pin1的信息,如下图:点击OK,pin就挂在了鼠标上,如下图:点击左键,放置Pin 1,这时pin还挂在了鼠标上,如下图:再点击左键,Pin 2也被放置,如下图:这时,可以修改Pin 2,左键双击Pin 2,在弹出的对话框中,根据资料输入Pin 2信息,如下图:点击OK后,如下图:然后,逐个地输入方法2:使用放置pin array可以采用Toolbar,如下图:或者,采用菜单Place/Pin Array,如下图:点击后,弹出下图:由于已经放置了两个管脚,我们从第三管脚开始,只设置前三个,如下图:其它的等放置完后,再修改,点击OK,如下图:下面修改管脚方法1:逐个修改方法2:使用Spreadsheet修改,步骤如下:全部选上想修改的管脚,如下图:点击右键,如下图:点击Edit Properties后,弹出下图:根据资料,修改如下:点击OK,如下图:放置Body框,如下图:方法1:使用Toolbar方法2:使用菜单,Place/Rectangular点击后,沿着虚线,拉出一个矩形即可,如下图:上面所有的管脚信息全部输入完了,下面调整管脚的位置直接用鼠标左键选取管脚,然后拖动到适当位置放置即可,调整Body框大小,如下图:元件创建完了后,可以通过Options/Part Properties,或者Options/Package Properties来修改,如下图:可以在Edit Part Properties对话框中修改PCB的封装View/Package命令,如下图:点击后,如下图:有时候,一个元件很大,分成几部分,使用View Package,可以看到全貌,View Part只能看到部分5.修改元件属性的另一种方法View/Package命令Edit/Properties命令,如下图:点击后,弹出下图:6.非矩形类元件的创建:新建一个FERRITE元件(磁珠)首先,修改栅格点,菜单:Options/Preferences,如下图:点击后,选择Grid Display Tab,如下图::不选择该项,则画线时,可以在任意点起始点击OK,完成Grid设置:点击Toolbar或者:菜单:Place/Ellipse画椭圆,如下图:下面填充第一个椭圆左键选取第一个椭圆,右键点击,如下图:点击Edit Properties,弹出下图:选择填充式样,如下图:点击OK,如下图:两个椭圆顶点画线:Toolbar,或Place/Line,如下图:调整Body框,如下图:下面,放置两个管脚,如下图:下面不显示管脚名字,Options/Part Properties,如下图:选择False,点击OK,如下图:这时候,最好在把Grid Display设置回去7.Blank第3讲分裂元件的制作方法1、homogeneous 和 heterogeneous 区别打开新建元件对话框:同质的,比如NE5532里有两个一样的运放:异质的,一个Package里有不同的功能单元2.创建homogeneous类型元件下图是NE5532的框图:我们以NE5532为例,如下图:点击OK,如下图:软件会在U?后面加上A、B等先画出运放的外框,如下图:接下来,设置输入管脚的正负属性:点击Toolbar的Place Text,或者菜单Place/Text,如下图:输入-,点击OK,再输入+,点击OK,如下图:接下来放置管脚,如下图:现在,完成了NE5532中两个运放中的一个,现在编辑另一个:Ctrl+N,或者View/Next Part,如下图:因为我们选择的是homogeneous类型元件,homogeneous元件默认Package里面的东西是完全一样的,只是管脚编号不一样,编辑管脚属性,输入管脚编号,如下图:注意:U?A和U?B两个Part,均有Pin4和Pin8,在homogeneous类型元件里是合法的对于简单的元器件,我们可以将Name隐藏掉,这样做并不影响理解Options/Part Properties,点击后,如下图:点击OK,如下图:Save,完成NE5532创建View/Package,看一下:3.创建heterogeneous类型元件仍以NE5532为例创建,在对话框中输入,如下图:点击OK画Body,放置管脚,完成第一个Part,如下图:接下来创建另一个PartCtrl+N,或者View/Next Part,如下图:创建U?B有两种方法方法1:教程中使用的,也就是重新画一个方法2:复制U?A,然后,粘贴到U?B,删除pin4和pin8,编辑pin5、pin6和pin7的属性,如下图:注意:(1) heterogeneous类型的元件的管脚是不能有重复的,所以上图的pin4和pin8要删除(2) 隐藏管脚,要分别对U?A和U?B进行操作View/Package,看一下Package,如下图:第4讲正确使用heterogeneous类型的元件1.可能出现的错误放进一个heterogeneous类型的Package,不会出问题放进两个heterogeneous类型的Package,就会出问题,因为软件不知道哪个Part与哪个part是一个Package 当执行Annotate(编号)时,会给出错误信息2.出现错误的原因放进两个以上heterogeneous类型的Package,就会出问题,因为软件不知道哪个Part与哪个part是一个Package3.正确的处理方法正确的处理方法:在元件库里进行相应得处理正确的创建heterogeneous类型的元件步骤:(1) 在第3讲中的方法(2) 设置一个Package属性启动OrCAD Capture CIS,打开我们在第3讲创建的元件库,打开NE5532_HETE,选取U?A Edit/Part Properties,执行后,弹出下图:点击New,新建一个属性,如下图:输入如下图所示:注意:Name不可选用Group,因为Group为一个保留的词,软件自己使用的点击OK,如下图:完成了U?A的设置,下面设置U?B,按Ctrl+N,选则、U?B,重复上面的步骤,完成了U?B的设置(3) 在原理图中,可以利用package属性,区分哪个U?A与哪个U?B是一个Package,方法:就是将想为一个Package的U?A与U?B的package设为相同的Value,比如:设为1;另一个Package的U?A与U?B的package的Value设为2(4) 在原理图中,当Tools/Annotate时,如下图:注意::把POWER_GROUND改为package,如下图:整个设置,如下图:(5) Blank第5讲加入元件库,放置元件1.如何在原理图中加入元件库打开工程管理器,激活原理图页面菜单方式:Place/Part,或快捷键方式:P,如下图:点击后,弹出下图:添加元件库::点击左侧图标,弹出下图:上面的是OrCAD Capture CIS自带的元件库,用哪个可以加哪个先添加我们自己做的元件库,指定路径和文件名,点击“打开”,如下图:下面添加常用元件库(OrCAD Capture CIS自带的元件库)Discrete.olb2.如何删除元件库如上图,选择想删除的元件库,然后,点击3.如何在元件库中搜索元件在Place Part对话框中,如下图:在知道元件在哪个库的情况下,选择那个库,然后在中输入元件,在Part List中就会出现想要的元件列表在不知道元件在哪个库的情况下,点击,如下图:在Path栏:指定搜索路径在Search For栏:输入搜索的名字然后,点击搜索结果将显示在里例如:搜索LM393,搜索结果显示LM393在OPAmp.olb库里面,如下图:选择LM393/OPAmp.olb,再点击Add,OPAmp.olb被添加到库中4.放置元件放置元件时要注意,教程中演示的与16.2中的不太一样,举例如下:如果这样选择:NE5532,Heterogeneous类型,Part A,如下图:点击,或双击NE5532,将NE5532放置在原理图页面上,它是按照U1A、U1B、U2A、U2B的顺序放置的,如下图:如果这样选择:NE5532,Heterogeneous类型,Part B,如下图:图:不知道为什么是这样5.旋转元件选取元件,然后按R键,或者右键点击,选择Rotate6.放置元件时,有无位号的设置Options/Preferences,点击Miscellaneous Tab,如下图:有无位号的设置在这里:7.放置电源和地也可以使用菜单:Place/Power,或者Place/Ground8.Design Cache每当放置一个元件,软件自动在Design Cache文件夹下,保存一个拷贝,如下图:这方便了我们再次放置同一类元件时,把Design Cache指定为Library,然后从中选取元件,如下图:第6讲同一个页面内建立电气互连1.放置wire,90度转角,任意转角方法1:Place/Wire方法2:按W键方法3:点击ToolbarOrCAD Capture CIS的默认连线是按照90度角连线;如果想可以任意角度连接,步骤如下:使用上面的方法1-3中的任意中,按住Shift键,这时鼠标再连线就可以了2.wire的连接方式3.十字交叉wire加入连接点方法,删除连接点方法加入连接点方法:方法1:Place/Junction方法2:按J键方法3:点击Toolbar删除连接点方法:在连接点上,再放置一个连接点,就可以删除掉4.放置net alias方法,连接网络用途:对于比较远的连接、单元电路输入、单元电路输出和电源等关键网络的一种可选择连接方法缺点:不熟悉电路时,看电路图不好找到信号是从那里过来的或去哪里了注意:放置net alias方法,连接网络只适用于同一页面,不同页面的连接不可以使用放置net alias方法不同页面的连接应该使用Off-Page connector放置net alias的方法方法1:Place/Net Alias方法2:按N键方法3:点击Toolbar点击后,弹出对话框,如下图:在Alias栏:输入IN,点击OK,然后,用鼠标点击网络名为IN的线,如下图:5.没有任何电气连接管脚处理方法没有任何电气连接的管脚应该标示为没有连接,否则,进行规则检查时,会报告出错方法1:Place/No Connect方法2:按X键方法3:点击Toolbar点击后,在没有电气连接的管脚处,点击一下,放置标示,再点击一次,取消标示,如下图:对比上图,可知道:哪里表示了6.建立电气连接的注意事项(1况下,不会出错(2)电源与元件的管脚,以及地与元件的管脚都不可以直接连接,一定要通过线进行连接(3)可以通过软件设置,不允许这样连接;在Options/Preferences下,Miscellaneous Tab,如下图:不要check这个选项第7讲总线的使用方法1.放置总线适用于:地址总线、数据总线等类型的连接放置方法:方法1:Place/Bus方法2:按B键方法3:点击Toolbar点击后,画出总线,双击结束,如下图:命名总线:点击Net Alias,如下图:注意:总线命名规则:以ED[0:31]为例说明如下:ED为Basename,Basename不可以以数字结尾[0:31]为总线数量标示,也可[0,,31]这个标示Basename与[0:31]之间不可以有空格点击OK,找到总线,如下图:注意:一定要放在总线上,点击左键,放置,如下图:下面通过Bus Entry来连接各个信号线到总线方法1:Place/Bus Entry方法2:按E键方法3:点击点击后,一个一个地放置,或按F4键依次放置,如下图:。