Cadencespb16.3学习笔记1_原理图

Cadence spb16.3学习笔记3__封装

Cadence学习笔记3__封装IPC软件计算后导出下面是STM32F103RCT6(64脚QFP封装)数据手册的封装尺寸:STM32F103xC, STM32F103xD, STM32F103xE Package characteristicsFigure 71. LQFP64 – 10 x 10 mm 64 pin low-profile Figure 72. Recommended footprintTable 72. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data然后打开IPC,在Calculate中打开SMD Calculator,选择QFP封装,双击或者点击ok,出现计算界面,如下图:此时在左侧窗口填上相应的数据,然后光标停在任意一个数据中回车,就可以计算出其余的尺寸了。

注意到这里的单位是毫米Millimeters,所以应该对应数据手册中的毫米而不是英尺。

Pitch(P)在图中是引脚中心的间距,对应于数据手册中的e,值为0.5。

A和B分别是两个方向上的引脚数量,都是16,下面给出了提示,如果是矩形芯片的话,A应该小于B。

Pin Count(for search)是引脚总数,填64。

L1和L2表示包括引脚的芯片宽度和长度,对应芯片手册的D和E,最小值是11.8,最大值是12.2。

T是引脚长度,对应于数据手册中的L,最小值为0.45,最大值为0.75。

W表示焊盘的宽度,对应于数据手册中的b,最小值为0.17,最大值为0.27。

A和B表示不包括引脚的芯片宽度和长度,对应芯片手册的D1和E1,最小值为9.8,最大值为10.2。

H表示芯片的高度,对应于芯片手册中的A,最大值为1.6,不用填最小值。

K表示芯片离PCB板的高度,对应于芯片手册中的A1,最小值为0.05,不用填最大值。

填完之后光标放在任意一个框中回车,就可以计算出其余的数据了。

Cadence_SPB16.3入门教程——元器件布局 .doc

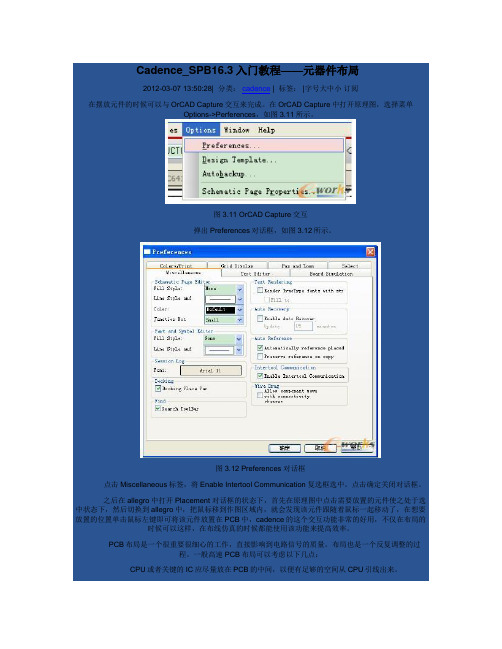

Cadence_SPB16.3入门教程——元器件布局2012-03-07 13:50:28| 分类:cadence | 标签: |字号大中小订阅在摆放元件的时候可以与OrCAD Capture交互来完成。

在OrCAD Capture中打开原理图,选择菜单Options->Perferences,如图3.11所示。

图3.11 OrCAD Capture交互弹出Preferences对话框,如图3.12所示。

图3.12 Preferences 对话框点击Miscellaneous标签,将Enable Intertool Communication复选框选中。

点击确定关闭对话框。

之后在allegro中打开Placement 对话框的状态下,首先在原理图中点击需要放置的元件使之处于选中状态下,然后切换到allegro中,把鼠标移到作图区域内,就会发现该元件跟随着鼠标一起移动了,在想要放置的位置单击鼠标左键即可将该元件放置在PCB中,cadence的这个交互功能非常的好用,不仅在布局的时候可以这样,在布线仿真的时候都能使用该功能来提高效率。

PCB布局是一个很重要很细心的工作,直接影响到电路信号的质量。

布局也是一个反复调整的过程。

一般高速PCB布局可以考虑以下几点:·CPU或者关键的IC应尽量放在PCB的中间,以便有足够的空间从CPU引线出来。

·CPU与内存之间的走线一般都要做等长匹配,所以内存芯片的放置要考虑走线长度也要考虑间隔是否够绕线。

·CPU的时钟芯片应尽量靠近CPU,并且要远离其它敏感的信号。

·CPU的复位电路应尽量远离时钟信号以及其它的高速信号。

·去耦电容应尽量靠近CPU电源的引脚,并且放置在CPU芯片的反面。

·电源部分应放在板子的四周,并且要远离一些高速敏感的信号。

·接插件应放置在板子的边上,发热大的元器件应放在置在通风条件好的位置,如机箱风扇的方向。

蚊子Cadence16.6粗略笔记 (1)

1 原理图笔记 (1)2 PCB笔记 (6)1 :原理图画完处理:1:检查连接性(眼睛看)2 重新编号,tool--->anotate3 DRC检查, tool---->Design rules check4 tools--->create netlist--->allegro(破解的不完全,有时候需要自己创建一个allgero文件夹。

2:PCB完成后处理事项:1 看连接线是否都铺完,tools->quick reqorts->unconnected pinsshape dynamic stateshape no netshape islandsDRC2 tools-->database check3 display-->state(保证全为绿色)4丝印层显示准备(把需要生成丝印的东西提取到丝印层):(显示stack-up(选pin/via/drc)/geometry(选outline/assemble_top/bottom/pin_number)/manufacturing(选autosilk_top/bottom))先把所有电气层关掉,stach-up-->所有etch关掉略去:5 生成丝印层---->manufacture-->silkscreen-->layer(选both)/elements(选both)/classes and subclasses(把那些东西提取出来放到丝印层,改package geometry和reference designator为silk 其余为none-->执行silkscreen6:提取之后,调整丝印信息,例如器件编号位置。

7 添加文字说明:add-->text-->manufacturing-->autosilk_top-->点击要添加文字的位置,输入文字就可以了8 设置钻孔文件数据参数——>manufacture-->nc-->nc parameters-->点击closed就自动把参数文件放置到设置好的目录下。

Cadence SPB16.3 进阶教程

Allegro SPB 16.3版PCB画板速成教材:目录:1.创建平面元器件图2.绘制原理图并添加好其属性3.生成网表4.制作PCB焊盘5.制作PCB封装器件6.新建PCB板(画板框设板层)7.导入网表8.布局9.布线10.覆铜11.DRC检查12.出光绘说明:这是一个简单明了的画图过程,而不讲细节,否则正如其它500多页的教材那样,让你一下子没有个清晰的概念,而这部教材是为了让你有个全过程的基础概念并可真正画出PCB板来,以后细节(或高级)部分你再慢慢去深究就不会觉得迷茫了。

(软件界面的介绍就省了,各大教材都已说得很清楚)可能有些细节上写得不对,仅供学习参考.By:龍治铭E-mail:693303589@2011/01/09一、创建电路原理中的新元器件(目的:库里没有现成的元器件就得自己创建以便在画原理图时调用)打开Allegro Design Entry CIS ,先创建自己的一个元器件库(以后你可以拷到U盘备份或到其它电脑用)如下图:点Library后弹出右图如上右图所示,library1.olb就是刚才建的库名称,如果你再建一个那就是library2.olb了。

右击library1.0lb那行,出现如下左边图所示:接着点New Part出现给元器件命名的对话框,如上右边图所示,PCB Footpring栏我们一般不在这里填,空着吧,原因很简单,以后你可能要它用作0603或0805的封装都不一定,所以先不理。

Parts per Pkg一栏意思就是你这个元器件你要分为几部分来画,比如LM358如果两个放大器我们分为两个来画,那就填2。

点OK后正式进入创建元器件界面如下图所示:点Place pin按钮开始加管脚,最后虚线元器件外框要加外框变为实线。

特别注意的是,各管脚名不可同名,否则生成网表时会报错而无法生成网表。

创好的元器件如下图:如上图所示就算建完了,点保存就可以了。

提示:管脚编号以后在做PCB封装时是相对应的.特别是三极管的中B中C封装形式值得注意一下.二、绘制原理图:(目的:生成网表及以后布局布线用)如下左边图选Project,点之出现右边图,我们是为了画PCB板而画的电路路就选PCB Board Wizard.命名→选保存的路径→点OK。

Cadence allegro spb 16.3安装说明

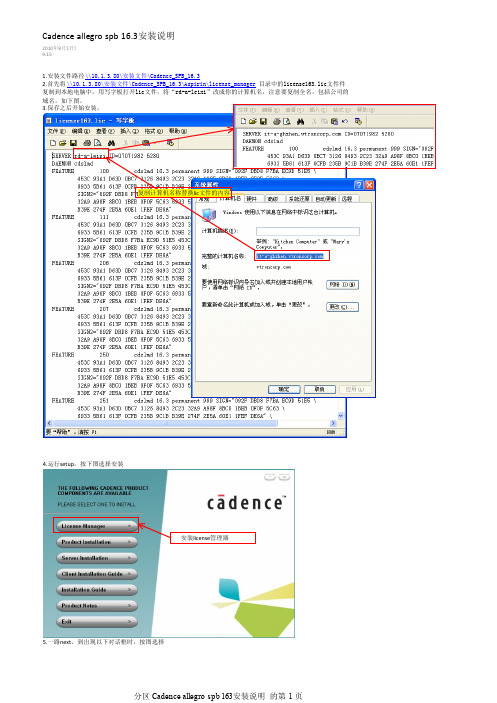

1.安装文件路径\\10.1.3.80\安装文件\Cadence_SPB_16.32.首先将\\10.1.3.80\安装文件\Cadence_SPB_16.3\Aspirin\license_manager目录中的license163.lic文件件复制到本地电脑中,用写字板打开lic文件,将“rd-a-leixi”改成你的计算机名,注意要复制全名,包括公司的域名,如下图。

3.保存之后开始安装。

复制计算机名称替换lic文件的内容4.运行setup,按下图选择安装5.一路next,到出现以下对话框时,按图选择安装license管理器Cadence allegro spb 16.3安装说明2010年8月17日9:15打开浏览找到刚才修改后的lic文件这里显示你的计算机名称,说明lic正确其它都不用管,直接点next点击完成用写字板打开安装license管理器目录(如X:\Cadence\LicenseManager)下的license.dat正确的应该是你的计算机名指向cdslmd.exe注意:这里只能有一个这样的内容,如果有重复的一定要删掉多余的,否则无法激活。

6.然后打开任务管理器,找到lmgrd.exe,结束这个进程。

将\\10.1.3.80\安装文件\Cadence_SPB_16.3\Aspirin\license_manager中的cdslmd.exe复制到本地电脑中license管理器的安装目录中(如x:\Cadence\LicenseManager),替换掉里面的这个文件。

注意:这个动作很重要,如果不操作的话,容易导致程序找不到license。

7.然后启动license管理器Lmtools,不要管下面的状态如何,都启动一下这个服务。

启动服务提示服务启动成功8.回到软件安装界面,按提示操作选择安装软件出现以下对话框时,按下图操作找到安装license管理器下面的license.dat,点next按提示操作,出现下面的对话框时,按自己的需要勾选模块,如果一次只安装一个,下次要添加的时候需要再破解过。

Cadence软件学习:绘制原理图

Cadence软件学习:绘制原理图基本操作:1、 Place Part(P):放置元件2、 Place wire(W):连接相连的pin脚3、 Place Auto wire:自动连线4、 Place bus(B):总线连接5、 Place junction(J):交叉点连接,两条wire相交有两种连接关系:连或不连,加J为连6、Place bus entry(E):可以理解为总线入口,有bus必有entry7、 Place net alias(N):相当于wire,用于连接距离远的Pin 脚,仅限于同一page电气连接8、 Place power(F):放置电源9、 Place ground(G):放置地10、 Place off-page connector:类似alias,但alias仅用于同一页面,而off-page用于不同页面之间的电气连接11、Place no connect(X):用于无电气连接的pin脚,不放会报错12、 Place text(T):放置文本常用操作:1、按住Ctrl滚动鼠标滚轮放大缩小原理图(以鼠标指针为中心);直接滚动鼠标滚轮上下移动;按住Shift滚动左右移动2、改变原理图尺寸大小:options->Schematic Page Properties->Page Size3、旋转器件:放置器件前直接按R可旋转,放置后选中按R旋转4、选中单个或者多个器件,按住Ctrl,鼠标左键在选择器件上按住拖动可复制所选器件5、连线时改变连线角度需先按shift键6、元件镜像:选定后V键(垂直)和H键(水平)7、鼠标右键选End mode结束当前操作8、连线时,终点如不是管脚脚,双击结束9、管脚之间不要直接相连,通过线连接以防出错(软件设置不允许连接的方法:Options/Preferences->Miscellaneous->Wire Drag 打钩去掉)10、总线命名规则:后期处理:1、浏览原理图:选中 .dsn , edit->browse可以浏览parts、nets等,主要检查是否有漏掉的信息,双击可以打开原理图并高亮显示所选内容2、元件替换和更新:右键需要修改的元件,选择Replace cache 或Update CacheReplace cache:用于替换Update Cache:用于更新1、 Cleanup Cache:右键Design Cache选择Cleanup Cache 用于检测Design Cache与原理图是否一致,并删除多余的内容2、移动:默认连线与移动元件一同移动,按住Alt 移动仅元件移动3、自动编号:右键.dsn 选Annotate 。

学习笔记-candence16.6-原理图部分

学习笔记目录一、原理图设计部分1.针对原理图界面的操作2.对原理图进行编辑3.对制作原件的编辑4.生成网表5.生成清单和打印设置针对原理图界面的操作Design entry CIS:进行板级设计时用来画原理图的。

PCB Editor:cadence进行布局布线的软件。

Cadence product choices-----OrCAD capture CIS进行原理图页面个性化设置(整体设置)Options-->design template..(即原理图页面模板). 进行原理图页面个性化设置(单页设置)Options-->schematic page propertise..5. .drn文件是建立的工程的数据库文件,包括电路原理图(schematic)、元件库(design cache)、输出文件(outputs)。

6.工具栏的显示、隐藏和自定义View-->toolbar7.更改原理图背景颜色Option-->Preferences..8.原理图的放大、缩小快捷键i、o。

View-->zoom-->in/out按住ctrl,滚动鼠标。

对原理图进行编辑旋转元器件:快捷键R画线:places -->wire快捷键W任意角度画线:画线时按住shift网络节点:junction删除网络节点:按住“s”键,鼠标左键单击节点,此时出现一个方框,这时按“delete”键,即可删除。

浏览命令browse整体浏览:选中.drn文件Edit-->browse-->parts/nets......点击原件标号可以直接定位到该原件。

对制作原件的编辑1.批量放置管脚:place--pin array2.批量修改管教:选中需要修改的管脚---右键---editproperties..3.查看元件的属性:options-->part propertise..Options-->edit part propertise..(可以改写footprint)相同的不同的4.查看一个package里的几个部分:View--packageView--package propertisesCtrl+B:package的上一级Ctrl+N:package的下一级5.画线时任意起点和终点画线:options--->prefences..-->grid display---取消pointer snap to grid6.按组编号:Tool-->annotate..四、生成网表Netlist---PCB Editor生成清单和打印设置TOOLS---Bill OF materials针对allegro原理图界面的操作allegro的5种应用模式(application mode)general edit 普通模式Placement edit 排零件模式。

Cadence学习笔记1__原理图

新建元件时选择Heterogeneous,A部分和上面的一样画法,但是按键盘上的ctrl+N切换到B部分时,B部分是空白的,需要再画一次。

不管是Homogeneous还是Heterogeneous,点击工具栏ViewPakage,可以将A和B同时显示出来,如下图:

保存后,一个元件就画好了,画原理图时直接调用即可。

如果是由两部分组成的分裂元件,要在新建元件时在Parts per Pkg写2,这里分为Homogeneous和Heterogeneous两种。Homogeneous是只要画出A部分,B部分会默认的和A部分完全一样,Heterogeneous是画好A部分后,B部分仍然是空白的,需要再画。如果一个芯片包含了2个功能完全相同的部分,像下图中NE5532中的两个运放,就需要用到Homogeneous了,这里先选Homogeneous,点击ok。

元器件

FileNewLibrary新建一个库,如下图,显示了路径和默认库名library1.olb,右击选择Save As可以改变路径和库名,右击新建一个元件,可以选择New Part或者是NewPart From Speadsheet,是两种不同的方式,先介绍New Part的操作。

右击选择New Part后,弹出下面的对话框,在Name中填入元件名,还可以指定PCBFootprint,下面Parts per Pkg表示这个元件有几部分,1表示普通的元件,如果元件是两部分组成的分裂元件就写2,这里先操作1,点击ok。

点击左侧工具栏make图标 ,所有的横线和竖线都变成粉红色的,这就生成了一个表格,鼠标右击选择Tag Pin Name,在引脚名这一列点一下,会在这一列最上面出现“Name”,同样的,右击选择TagPin Number,在引脚编号这一列点一下,会在这一列最上面出现“Num”,如果放错了,比如说该放Name的地方放成了Num,可以在放Num之后再点一次,Num就消失了,产生的结果如上图右。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

元器件

FileNewLibrary新建一个库,如下图,显示了路径和默认库名library1.olb,右击选择Save As可以改变路径和库名,右击新建一个元件,可以选择New Part或者是NewPart From Speadsheet,是两种不同的方式,先介绍New Part的操作。

右击选择New Part后,弹出下面的对话框,在Name中填入元件名,还可以指定PCBFootprint,下面Parts per Pkg表示这个元件有几部分,1表示普通的元件,如果元件是两部分组成的分裂元件就写2,这里先操作1,点击ok。

A部分画好后,按键盘上的ctrl+N可以切换到B部分,此时B部分已经画好了,和A部分一样,只是没有引脚编号,双击每一个引脚添加编号即可,如上图右。注意,一个元件中的引脚编号应该是不重复的,但是这个元件只有一套电源,而且引脚4和8是将A和B接到一起的,所以A和B中都有4和8。返回到A部分按键盘ctrl+B即可。由于只有两部分,按ctrl+N也可以。N是Next,B是Back。

保存后,一个元件就画好了,画原理图时直接调用即可。

如果是由两部分组成的分裂元件,要在新建元件时在Parts per Pkg写2,这里分为Homogeneous和Heterogeneous两种。Homogeneous是只要画出A部分,B部分会默认的和A部分完全一样,Heterogeneous是画好A部分后,B部分仍然是空白的,需要再画。如果一个芯片包含了2个功能完全相同的部分,像下图中NE5532中的两个运放,就需要用到Homogeneous了,这里先选Homogeneous,点击ok。

下面介绍Heterogeneous的操作。

新建元件时选择Heterogeneous,A部分和上面的一样画法,但是按键盘上的ctrl+N切换到B部分时,B部分是空白的,需要再画一次。

不管是Homogeneous还是Heterogeneous,点击工具栏ViewPakage,可以将A和B同时显示出来,如下图:

此时会在库工程目录下面出现NE5532,右击选择Rename可以改变元件名,如果要从库中删除这个元件,关闭元件编辑窗口后,右击选择cut即可,如下图:

此时开始编辑元件了,先用直线画三角形,和两个竖线,然后用放置Text的方式加上+和-符号,如果不能放的更好,可以先取消勾选栅格点限制,然后再勾选。

接着放置引脚,从上图可以看到运放A的5个引脚编号和引脚名,在右侧工具栏点击 图标放置引脚,引脚名输入IN-,引脚编号输入2,类型选Input,点击ok,然后在上图中+号处点一下图标,就会出现一个引脚,其余引脚同样设置。注意引脚类型为输入输出时,默认是可见的,如果引脚为power型,需要勾选PinVisible才能可见,如下图左,也可以连续放几个引脚,然后再双击引脚改变它们的属性。

也可以在一个Excel表格里编辑好后复制粘贴到这里,也可以将这里的内容通过ctrl+C复制到Excel里。Pin Visibility勾选就在表格里写1,不勾选就写0,一般都是勾选的。下图是Excel里填好的第一项:

有的时候,芯片的引脚很多,比如说64或更多,就可以从数据手册直接抓取引脚名:

如果打开了多个元件编辑窗口,在窗口上右击选择Clபைடு நூலகம்se就可以关闭了。

如果右击元件库library1.olb新建一个元件,选择NewPart From Speadsheet,则会打开一个表格,如下图,已经填好了第一个引脚,写好后点击save保存,section表示引脚所在的部分,如果是只有一部分的元件就选择A,如果是有两部分组成的就相应的选择A或者B,如果在Section上侧选的是Alphabetic,就显示A或B,如果选的是Numetic就显示1或2:

cadence学习笔记1__原理图

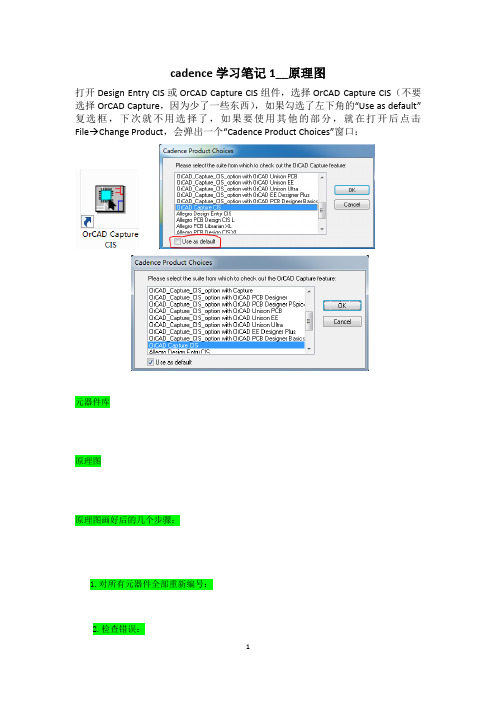

打开Design Entry CIS或OrCAD Capture CIS组件,选择OrCAD CaptureCIS(不要选择OrCAD Capture,因为少了一些东西),如果勾选了左下角的“Use as default”复选框,下次就不用选择了,如果要使用其他的部分,就在打开后点击FileChange Product,会弹出一个“Cadence Product Choices”窗口:

如果想改变其中一个引脚的引脚名、引脚编号、引脚类型,选中该引脚,右击选择EditProperties,或者双击该引脚,如下图:

画直线的时候,这里默认是按照栅格点为最小单位的,可以改变这种限制,画出任意长度任意角度的线,在工具栏OptionsGrid Display中,不要勾选Pointersnap to grid就可以了,记得画完想要的任意直线后,再将这里勾选,这是一个好习惯,可以让画出的线更规则整齐。

在使用两个或两个以上部分的元件时,无论是Homogeneous还是Heterogeneous,都要先对元件新建一个属性(似乎16.3版本不需要,15.7版本需要),并赋相同的属性值,如Homogeneous类型的元件,在A或B部分双击空白处打开元件属性窗口,属性名随便写,但是不要写关键字group,因为在布局布线的时候会有冲突,属性值随便写,这里写1,点击ok,可以看到属性窗口多了一个package属性,如下图。对于Heterogeneous类的元件,要在A和B部分都新建这样一个属性,而且属性名和属性值都一样。