实验一、1位全加器的原理图设计

一位全加器的设计

一位全加器的设计一.实验目的1.掌握原理图输入设计。

2.利用一位半加器实现一位全加器。

二.实验原理1.一位半加器输入a,b;输出co,so;其中co为进位输出;so为和的输出;真值表如下图所示。

2.一位全加器真值表如下图所示。

三.实验内容1.以原理图输入作为设计输入,设计半加器。

2.利用设计好的半加器,实现全加器的设计。

3.通过仿真,观察设计的正确性。

4.仿真完成后,将原理图设计转换为VHDL文件。

四.设计提示仔细阅读真值表,思考如何将半加器设计为全加器。

五.实验报告要求1.写出原理图设计。

(半加器电路原理图)(全加器原理图)2.分析设计过程。

用两个半加器构成全加器。

3.记录仿真波形,保存生成的元件以及RTL,将原理图文件转变为VHDL文件。

(全加器仿真图)(符号元件)(全加器RTL)(全加器VHDL文件)LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY work;ENTITY quan2 ISPORT(a : IN STD_LOGIC;b : IN STD_LOGIC;c : IN STD_LOGIC;ci : OUT STD_LOGIC;si : OUT STD_LOGIC);END quan2;ARCHITECTURE bdf_type OF quan2 ISCOMPONENT quanPORT(a : IN STD_LOGIC;b : IN STD_LOGIC;co : OUT STD_LOGIC;so : OUT STD_LOGIC);END COMPONENT;SIGNAL SYNTHESIZED_WIRE_0 : STD_LOGIC;SIGNAL SYNTHESIZED_WIRE_1 : STD_LOGIC;SIGNAL SYNTHESIZED_WIRE_2 : STD_LOGIC;BEGINb2v_inst : quanPORT MAP(a => a,b => b,co => SYNTHESIZED_WIRE_2,so => SYNTHESIZED_WIRE_0);b2v_inst1 : quanPORT MAP(a => SYNTHESIZED_WIRE_0,b => c,co => SYNTHESIZED_WIRE_1,so => si);ci <= SYNTHESIZED_WIRE_1 OR SYNTHESIZED_WIRE_2;END bdf_type;4.书写实验报告时要结构合理,层次分明,在分析描述的时候,注意语言的流畅。

一位全加器实验

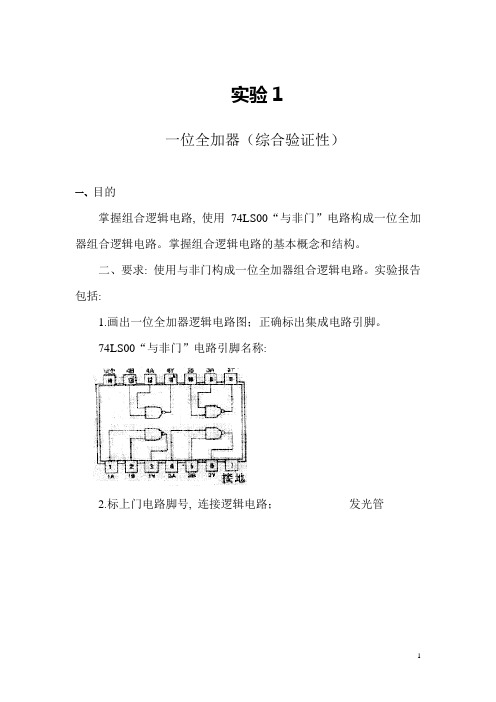

实验1一位全加器(综合验证性)一、目的掌握组合逻辑电路, 使用74LS00“与非门”电路构成一位全加器组合逻辑电路。

掌握组合逻辑电路的基本概念和结构。

二、要求: 使用与非门构成一位全加器组合逻辑电路。

实验报告包括:1.画出一位全加器逻辑电路图;正确标出集成电路引脚。

74LS00“与非门”电路引脚名称:2.标上门电路脚号, 连接逻辑电路;发光管3.模拟输入Ai 、Bi 、Ci, 记载Si 、Ci-1实验结果。

Ai Bi Ci Si Ci-1三、实验设备和集成电路1.数字逻辑实验板一块。

2、3片74LS00, 连结导线50根。

四、考核方式1.逻辑电路图应当整洁、规范。

2.实验前作好充分实验准备。

3.数字逻辑实验课是一项实践性很强的教学课程。

考核的重点是电路连接, 调试和测试的实践性环节。

考察学生在实验中的动手能力和事实求是的科学态度。

核心是检查是否能够实际完成一位全加器数字逻辑电路, 并电路运行正确作为重要标准。

在电路连接, 调试和测试完成后, 经老师检查确认满足实验要求, 学生签字, 递交报告书, 方可通过实验一的验收。

五、连接, 调试和测试组合逻辑电路参考事项注意如下:1.实验开始时, 检查并确定实验设备上的集成电路是否符合要求。

2、导线在插孔中一定要牢固接触。

集成电路引脚与引脚之间的连线一定要良好接触。

连线在面包板上排列整齐, 连线的转弯成直角。

连线不要飞线。

3、在组合逻辑电路连线时, 为了防止连线时出错, 可以在每连接一根线以后, 在组合逻辑电路图中做一个记号, 这样可以避免搞错连线, 漏掉连线, 多余连线等现象发生。

实验一1 1位全加器的设计

实验一1位全加器的设计一、实验目的1.熟悉ISE软件的使用;2.熟悉下载平台的使用;3.掌握利用层次结构描述法设计电路。

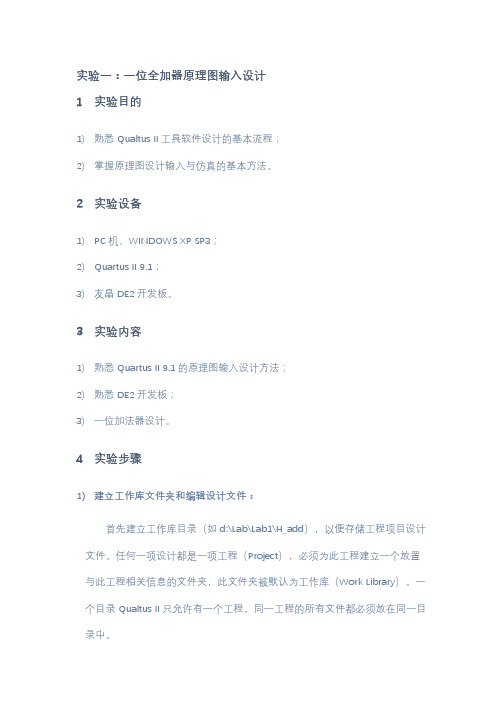

二、实验原理及说明由数字电路知识可知,一位全加器可由两个一位半加器与一个或门构成,其原理图如图1所示。

该设计利用层次结构描述法,首先设计半加器电路,将其打包为半加器模块;然后在顶层调用半加器模块组成全加器电路;最后将全加器电路编译下载到实验板,其中a,b,cin 信号可采用实验箱上SW0,SW1,SW2键作为输入,输出sum,cout信号采用发光二极管LED3,LED2来显示。

图1 全加器原理图三、实验步骤1.在ISE软件下创建一工程,工程名为full_adder,工程路径在E盘,或DATA盘,并以学号为文件夹,注意不要有中文路径,注意:不可将工程放到默认的软件安装目录中。

芯片名为Spartan3E系列的XC3S500E-PQG2082.新建Verilog HDL文件,首先设计半加器,输入如下源程序;module half_adder(a,b,s,co);input a,b;output s,co;wire s,co;assign co=a & b;assign s=a ^ b;endmodule3.保存半加器程序为half_adder.v,通过HDL Bench画仿真波形,获得仿真用激励文件,随后进行功能仿真、时序仿真,验证设计的正确性,观察两种仿真波形的差异。

4.在Design窗口中,选择Design Utilities→Create Schematic Symbol创建半加器模块;5.新建一原理图(Schematic)文件,在原理图中调用两个半加器模块、一个或门模块,按照图1所示连接电路,并连接输入、输出引脚。

完成后另保存full_adder.sch。

6.对设计进行综合,如出现错误请按照错误提示进行修改。

7.HDL Bench画仿真波形,获得仿真用激励文件,分别进行功能与时序仿真,验证全加器的逻辑功能,观察两类波形的差异。

实验指导书-一位全加器原理图输入设计

实验一:一位全加器原理图输入设计1实验目的1)熟悉Qualtus II工具软件设计的基本流程;2)掌握原理图设计输入与仿真的基本方法。

2实验设备1)PC机、WINDOWS XP SP3;2)Quartus II 9.1;3)友晶DE2开发板。

3实验内容1)熟悉Quartus II 9.1的原理图输入设计方法;2)熟悉DE2开发板;3)一位加法器设计。

4实验步骤1)建立工作库文件夹和编辑设计文件:首先建立工作库目录(如d:\Lab\Lab1\H_add),以便存储工程项目设计文件。

任何一项设计都是一项工程(Project),必须为此工程建立一个放置与此工程相关信息的文件夹,此文件夹被默认为工作库(Work Library)。

一个目录Qualtus II只允许有一个工程,同一工程的所有文件都必须放在同一目录中。

①打开编辑窗口打开Quartus II,选择菜单File→New命令。

在弹出的New对话框中选择Design Files的Block Diagram/Schematic File,如下图所示:②放置元件在原理图编辑窗中的任何空白处双击鼠标左键,跳出Symbol选择窗(或单击右键选择Insert→Symbol…),出现元件选择对话框,如下图所示:元件选择对话框中Libraries:的路径c:/altera/90/quartus/libraries/primitives下为基本逻辑元件库,双击选择你需要的元件(如二与门);或者在Name:中直接输入元件名称(AND2),单击OK按钮。

你需要的元件会出现在原理图逻辑窗中。

为了设计半加器,分别调入元件AND2、NOT、XNOR2、INPUT和OUTPUT。

如果安放相同元件,只要按住Ctrl键,同时用鼠标拖动该元件。

③添加连线,引脚命名把鼠标移到引脚附近,则鼠标自动由箭头变为十字,按住鼠标左键拖动,即可画出连线。

双击INPUT和OUTPUT的PIN-NAME,使其变成黑色,再输入各引脚名:ain、bin、co和so。

EXP01实验一 一位全加器设计

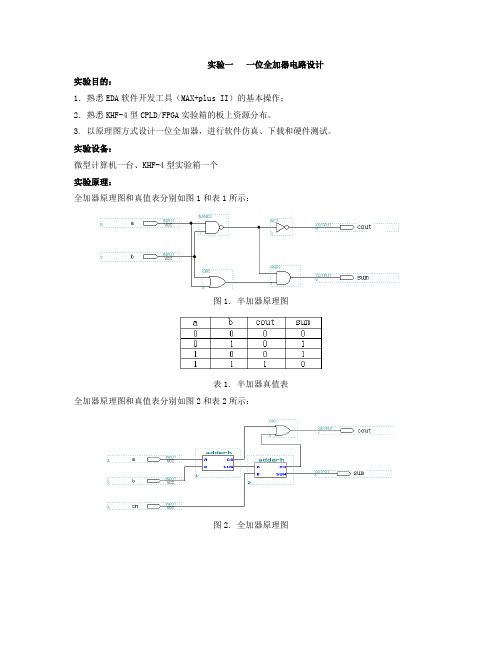

实验一一位全加器电路设计实验目的:1.熟悉EDA软件开发工具(MAX+plus II)的基本操作;2.熟悉KHF-4型CPLD/FPGA实验箱的板上资源分布。

3. 以原理图方式设计一位全加器,进行软件仿真、下载和硬件测试。

实验设备:微型计算机一台、KHF-4型实验箱一个实验原理:全加器原理图和真值表分别如图1和表1所示:图1. 半加器原理图表1. 半加器真值表全加器原理图和真值表分别如图2和表2所示:图2. 全加器原理图表2. 全加器真值表实验步骤:1)打开MAX+plus II设计软件。

2)新建图形编辑文件(File/New/Graphic Edit file),在文件空白处双击鼠标左键(或选择菜单Symbol/Enter Symbol)打开添加符号对话框(Enter Symbol),在“Symbol Libraries”框中双击选择“../maxplus2/max2lib/prim”库,在Symbol Files添加半加器原理图中各元件、输入(input)和输出(output)管脚,修改管脚名称后完成半加器原理图的绘制如图1;保存文件到具体设计目下。

图3.新建文件、添加符号和保存文件3)将半加器文件设为顶层文件(File/Project/Set Project to Current File),打开编译器(MAX+plus II/Complier)进行编译综合。

图4.设为顶层和编译4)创建半加器符号(File/Creat Default Symble)。

5)新建图形编辑文件(File/New/Graphic Edit file),在文件空白处双击鼠标左键打开添加符号对话框(Enter Symbol),从“File Symbol”框中调用半加器符号,完成全加器原理图的绘制如图2,保存文件到具体设计目录。

6)将全加器文件设为顶层文件,打开编译器进行编译综合。

7)新建波形编辑文件(File/New/Waveform Edit file),添加节点信号(在Name下点击鼠标右键选择Enter Nodes from SNF…)并编辑输入信号波形;保存(File/Save)波形文件(按默认文件名点击OK保存)。

实验一--一位全加器的原理图设计【范本模板】

桂林电子科技大学实验报告2015-2016学年第二学期开课单位海洋信息工程学院适用年级、专业13级电子信息工程课程名称EDA技术与应用主讲教师覃琴实验名称一位全加器学号1316030515姓名魏春梅实验一一位全加器的原理图设计一、实验目的①掌握Quartus II原理图输入法的编辑、编译(综合)、仿真和编程下载的操作过程.②用原理图输入法设计全加器电路,并通过电路仿真和硬件验证,进一步了解全加器的功能.③熟悉EDA实训仪的使用方法。

二、实验原理考虑来自低位来的进位的加法运算称为”全加”,能实现全加运算的电路称为全加器.1位全加器的真值表如表1。

1所列,表中的A、B是两个一位二进制加数的输入端。

CI是来自低位来的进位输入端。

SO是和数输出端,CO是向高位的进位输出端。

根据真值表写出电路输出与输入之间的逻辑关系表达式为:A B CI SO CO三、实验设备①EDA实训仪1台.②计算机1台(装有Quartus II软件)。

四、实验内容在Quartus II软件中,采用原理图输入法设计1位的全加器电路,编辑、编译(综合)、仿真,引脚锁定,并下载到EDA实训仪中进行验证。

注:用EDA实训仪上的拨动开关S1、S2、SO分别作为加数A、加数B、低位进位输入端CI,用发光二极管L1、L0分别作为和输出端SO、仅为输出端CO。

五、实验预习要求①查阅资料,复习有关全加器的内容,并认真阅读实验指导书,分析、掌握实验原理.②预习理论课本有关Quartus II软件的使用方法,并简要地写出Quartus II软件的操作步骤。

③复习数字逻辑电路有关全加器的内容,设计1位全加器的逻辑电路图。

1、实验电路图路径:E/1316030515/adder2、实验波形仿真图路径:E/1316030515/adder3、实验结果图六、实验总结①用Quartus II软件的原理图输入法进行数字电路设计的方法及步骤。

1、建立工程项目(文件夹、工程名、芯片选择);2、编辑设计文件(元件、连线、输入输出、检查电路正确性);3、时序仿真(波形验证设计结果);4、引脚锁定(参考文件锁定输入输出引脚);5、编译下载;6、硬件调试。

实验1 1位全加器设计

实验1 一位全加器设计【实验目的】1.掌握数字电路的两种设计方法2.掌握在Cadence中绘制原理图的方法3.掌握芯片外围特性与实现硬件电路4.掌握Verilog HDL设计电路的方法。

【实验内容】1.设计1位全加器2.绘制1位全加器原理图3.在面包板上实现1位全加器设计4.用Verilog HDL行为描述法设计实现1位全加器并仿真【实验器件】1.异或门电路74HC86一片,内含四个异或门,异或门的引脚封装图与内部原理如图1-1所示。

图1-1 异或门74HC86的内部原理图与芯片封装图2.与门电路芯片74HC08一片,内含四个与门,与门的引脚封装图与内部原理如图1-2所示。

图1-2与门74HC08的内部原理图与芯片封装图3.或门电路芯片74HC32一片,内含四个或门,或门的引脚封装图与内部原理如图1-3所示。

图1-3或门74HC32的内部原理图与芯片封装图4.3个1k的电阻和两个发光二极管,一个8路开关,5v电源,面包板一块,导线若干条。

【实验步骤】1.设计1位全加器1)设1位全加器的输入为被加数为A,加数B,低位进位Cin;输出为本位和Sum,对高位的进位为Cout。

2)根据1位加法器的运算{Cout,Sum}=A+B+Cin列真值表如表吗-1所示。

表1-1 1位加法器真值表3)根据真值表列出逻辑表达式CinBACinBACinBACinBABACinABBAABCinCinBACinBACinBASum⊕⊕=⊕+⊕=+++=+++=)()()()(ABCinBAABCinCinABCinBABCinACout+⊕=+++=)(4)手动绘制该原理图,为电路加上开关控制数据输入,用发光二极管显示输出,电路图如图1-4所示。

图1-4 1位全加器原理图2.在实验板上连接实现该电路并分析电路元件构成3.在protel软件中绘制原理图1)绘制元件符号2)绘制原理图4. .在protel软件中绘制pcb1)封装绘制2)pcb绘制。

1位全加器原理图输入设计

实验步骤

(6)波形文件存盘。 (7)运行仿真器。 (注意,刚进入窗口时,应该将最下方的滑标拖 向最左侧,以便可观察到初始波形)。 (8)观察分析波形。 MAX+plusII项及其中的Timing Analyzer选 项,点击跳出的分析器窗口中的Start键。

实验步骤

6. 包装元件入库 7. 设计顶层文件 (1)仿照前面的“步骤2”,打开一个新的原理图 编辑窗,然后在元件输入窗的本工程目录中找到 已包装好的半加器元件,并将它调入原理图编辑 窗中。这时如果对编辑窗中的半加器元件双击, 即刻弹出此元件内部的原理图。 (2)完成全加器原理图设计。 (3)将当前文件设置成Project。

实验步骤

最后启动编译器,首先选择左上角MAX+plusII 选项,在其下拉菜单中选择编译器项Compiler。 点击Start,开始编译!如果发现有错,排除错误 后再次编译。 5. 时序仿真 (1)建立波形文件。选菜单 FileNew,再选择 Waveform Editer..项,打开波形编辑窗。

实验步骤

首先在Assign选项的下拉菜单中选择器件选择项 Device,此窗口的Device Family是器件序列 栏,应该首先在此拦中选定目标器件对应的序列 名,为了选择EPF10K10LC84-4器件,应将此 栏下方标有Show only Fastest Speed Grades 的勾消去以便显示出所有速度级别的器件。完成 器件选择后,按OK键。

一位全加器_可编程逻辑器件VHDL实验报告

1.一位全加器实验报告一、实验目的要求学习计数器的设计、仿真和硬件测试,进一步熟悉VHDL设计技术。

设计程序独立完成全加器的仿真。

全加器由两个半加器组合而成,原理类似。

半加器不考虑低位进位,但有高位进位;全加器要考虑低位的进位且该进位和求和的二进制相加,可能获得更高的进位。

二、设计方法与原理图图1是一个一位二进制全加器电路图,由图1所示,由两个半加器和一个或门构成一个一位二进制全加器;ain,bin为全加器的输入端,cin为全加器的低位进位,sum是全加器的全加和,cout是全加器的全加进位端;从而实现一位二进制全加器。

(图1)一位二进制全加器原理图三、实验内容按照教材上的步骤,在max plus II上进行编辑、编译、综合、适配、仿真。

说明例中各语句的作用,详细描述示例的功能特点,给出其所有信号的时序仿真波形。

四、源程序library ieee;use ieee.std_logic_1164.all;entity full_adder isport(a,b,cin:in std_logic;cout,sum:out std_logic);end entity full_adder;architecture fd1 of full_adder iscomponent h_adderport(a,b:in std_logic;co,so:out std_logic);end component;component or2aport(a,b:in std_logic;c:out std_logic);end component;signal d,e,f:std_logic;beginu1:h_adder port map(a=>ain,b=>bin,co=>d,so=>e); u2:h_adder port map(a=>e,b=>cin,co=>f,so=>sum); u3:or2a port map(a=>d,b=>f,c=>cout);end fd1;五过程性截图六、仿真结果(图2)一位二进制全加器仿真结果七、分析结果与总结由图2,本实验的目标已达成,及通过编写VHDL语言实现一个一位二进制全加器。

实验一1位全加器电路设计

实验一1位全加器电路的设计一、实验目的1、学会利用Quartus Ⅱ软件的原理图输入方法设计简单的逻辑电路;2、熟悉利用Quartus Ⅱ软件对设计电路进行仿真的方法;3、理解层次化的设计方法。

二、实验内容1、用原理图输入方法设计完成一个半加器电路。

并进行编译与仿真。

2、设计一个由半加器构成1位全加器的原理图电路,并进行编译与仿真。

3、设计一个由1位全加器构成4位加法器的原理图电路,并进行编译与仿真。

三、实验步骤1. 使用Quartus建立工程项目从【开始】>>【程序】>>【ALtera】>>【QuartusII6.0】打开Quartus软件,界面如图1-1示。

图1-1 Quartus软件界面在图1-1中从【File】>>【New Project Wizard...】新建工程项目,出现新建项目向导New Project Wizard 对话框如图1-2所示。

该对话框说明新建工程应该完成的工作。

在图1-2中点击NEXT进入新建项目目录、项目名称和顶层实体对话框,如图1-3 所示,顶层实体名与项目名可以不同,也可以不同。

输入项目目录如E:\0512301\ first、工程项目名称和顶层实体名同为fadder。

图1-2 新建工程向导说明对话框图1-3 新建工程目录、项目名、顶层实体名对话框接着点击NEXT进入新建添加文件对话框如图1-4所示。

这里是新建工程,暂无输入文件,直接点击NEXT进入器件选择对话框如图1-5所示。

这里选择Cyclone 系列的EP1C6Q240C8。

图1-4 新建添加文件对话框图1-5器件选择对话框点击NEXT进入添加第三方EDA开发工具对话框如图1-6所示。

图1-6 添加第三方EDA开发工具对话框本实验只利用Quartus集成环境开发,不使用其它EDA开发工具,直接点击NEXT进入工程信息报告对话框如图1-7所示。

点击Finish完成新建工程项目的建立如图1-8示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一一位全加器的原理图设计

一、实验目的:

1、学习QuartusⅡ软件的使用,包括软件安装及基本的使用流程。

2、掌握用原理图输入法设计简单组合电路的方法和详细设计流程。

3、掌握原理图的层次化设计方法。

二、实验原理:

本实验要用原理图输入设计方法完成1位全加器的设计。

1位全加器可以用两个半加器及一个或门连接构成,因此需要首先完成半加器的设计。

采用原理图层次化的设计方法,按照课本4.5节介绍的方法用原理图输入法设计一个半加器,并将其封装成模块,然后在顶层调用半加器模块完成1位全加器的设计。

三、实验内容和步骤:

1、打开原理图编辑器,完成半加器的设计。

半加器原理图如下:

2、完成1位半加器的设计输入、目标器件选择、编译和仿真各步骤,详细过程见教材4.5节相关内容。

3、正确完成之后,选择“File”/“create/Update”/“Create Symbol file for current file”,将文件变成一个包装好的单一元件模块待调用。

4、调用1位半加器模块可画出以下1 位全加器:

5、保存并完全编译,进行仿真,给出仿真结果。

6、引脚锁定并下载。

7、引脚锁定后再重新编译,并连接实验箱进行下载。

注意第一次下载时的一些设定。

四、根据以上的实验内容写出实验报告,包括实验目的、实验原理、实验内容和步骤、仿真分析、硬件测试,给出仿真波形图及实验总结。