实验一1 1位全加器的设计

全加器设计

步骤8:编程下载

(1)下载方式设定。

通信仿真之MAX+plus II应用

39

步骤8:编程下载

通信仿真之MAX+plus II应用

40

步骤8:编程下载

通信仿真之MAX+plus II应用

41

步骤8:编程下载

(2)下载。连接好硬件及下载连接线等。按“Configure”下载 配置文件。成功后通过硬件进行逻辑验证。

通信仿真之MAX+plus II应用

2

3基本设计步骤

步骤1:为本项工程设计建立文件夹 任何一项设计都是一项工程(Project),都 必须首先为此工程建立一个放置与此工程相关的 文件的文件夹,此文件夹将被EDA软件默认为工 作库(Work Library)。一般不同的设计项目最 好放在相应的文件夹中,注意,一个设计项目可 以包含多个设计文件。 假设本项设计的文件夹取名为MY_Project,路径 为D:\ MY_Project, MAX+plus II 软件装在D盘 maxplus2文件夹下。 注意:文件夹名不能用中文,且不可带空格。

通信仿真之MAX+plus II应用 8

步骤2:输入设计项目和存盘

(4)调入元件and2、not、xnor、input和output。

方法一:用鼠标双击元件 库“Symbol Libraries”中 d:\maxplus2\maxplus2\ma x2lib\prim项。在 “Symbol Files”窗口即可 看到基本逻辑元件库prim 中的所有元件,双击需要 的元件即可调入原理图编 辑窗中。

27

步骤5:时序仿真

(7)运行仿真器。

实验一 1位全加器的设计(修改后)

• 步骤三:编辑全加器的原理图: 步骤三:编辑全加器的原理图:

• 由file->new,打开原理图文件Block Diaoram/Schematic File,并存盘为full_adder.bdf

左键双击原理图编辑窗空白处,弹出如下窗口

• 调入 1)半加器:half_adder, 2)二输入或门:2or, 3)输入,输出引脚

实验一 1位全加器的设计 位全加器的设计

一位全加器的原理分析

• 一位全加器可由两个一位半加器与一个或 门构成,其原理图如下图。

该设计利用层次结构描述法, • 首先设计半加器电路,将其打包为半加器 模块; • 然后在顶层调用半加器模块 半加器模块和ALTERA提供 半加器模块 的二输入或门 输入或门组成全加器电路; 输入或门 • 最后将全加器电路编译下载到实验箱,

输入是 两个加数:ain,bin, 一个进位:cin 这三个输入数据是1位(1bit),可由DE2的 SW0,SW1,SW2提供 为了显示更加清楚,可以将ain,bin,cin的输出引 出到DE2上的红色发光二极管显示,可选用 LEDR0,LEDR1,LEDR2. 输出是: 输出是: 和:sum 进位:cout 输出可由DE2的绿色发光二极管显示,可选用 LEDG0,LEDG1

• 步骤一:建立full_adder的工程 (project)

新建立full_adder工程(project)

设置project相关参数

• 设置project放置的位置及其名称,随后按 Next继续

• 添加文件到工程(project)中,在无相关文件需要 添加的情况下,按Next继续

• 选择FPGA目标器件,根据DE2的平台情况,选 择cyclone II系列的EP2C35F672C6,继续

整理实验一-一位二进制全加器设计实验

整理人 尼克 实验一一位二进制全加器设计实验目录实验一Protel DXP 2004认识实验 (1)实验二两级阻容耦合三极管放大电路原理图设计 (1)实验三原理图元件库建立与调用 (3)实验四两级阻容耦合三极管放大电路PCB图设计 (5)实验五集成电路的逻辑功能测试 (7)实验六组合逻辑电路分析与设计 (12)实验七Quartus II 的使用 (17)实验八组合逻辑器件设计 (17)实验九组合电路设计 (25)实验一 Protel DXP 2004 认识实验一、实验目的1.掌握Prot e l DXP 2004 的安装、启动和关闭。

2.了解Protel DXP 2004 主窗口的组成和各部分的作用。

3.掌握Prot e l DXP 2004 工程和文件的新建、保存、打开。

二、实验内容与步骤1、Protel_DXP_2004 的安装(1)用虚拟光驱软件打开Protel_DXP_2004.iso 文件(2)运行setup\Setup.exe 文件,安装Protel DXP 2004(3) 运行破解程序后,点击“导入模版”,先导入一个ini文件模版(如果要生成单机版的License选择Unified Nexar-Protel License.ini;要生成网络版的License选择Unified Nexar-Protel Network License.ini),然后修改里面的参数:TransactorName=Your Name(将“Your Name”替换为你想要注册的用户名);SerialNumber=0000000(如果你只有一台计算机,那么这个可以不用修改,如果有两台以上的计算机且连成局域网,那么请保证每个License文件中的SerialNumber=为不同的值。

修改完成后点击“生成协议文件”,任意输入一个文件名(文件后缀为.alf)保存,程序会在相应目录中生成1个License文件。

点击“替换密钥”,选取DXP.exe (在DXP 2004安装目录里,默认路径为C:\Program Files\Altium2004\),程序会自动替换文件中的公开密钥。

一位全加器的设计

一位全加器的设计全加器的主要作用是将两个二进制数相加,并产生一个结果和一个进位。

在设计全加器时,我们需要考虑以下几个方面:输入信号的处理、逻辑门的选择、进位的传递、和输出结果的计算。

首先,我们需要考虑输入信号的处理。

一个全加器需要接收两个二进制数和一个进位作为输入信号。

每个输入信号都可以用一个二进制位表示,这些位可以通过电路的输入端口进入电路。

在设计全加器时,我们需要确定如何使用这些输入信号。

其次,我们需要选择逻辑门来实现全加器。

逻辑门是数字电路的基本组件,通常用于实现计算和逻辑运算。

在设计全加器时,我们可以使用与门、或门和异或门来完成计算。

接下来,我们需要实现进位的传递。

当两个二进制数相加时,如果它们的和超过了二进制数能够表示的范围,就会产生一个进位。

为了实现进位的传递,我们可以使用逻辑门来判断是否产生了进位,并将进位传递到高位。

最后,我们需要计算输出结果。

一个全加器的输出结果是一个和位和一个进位位。

和位表示两个输入位的和,进位位表示是否产生了进位。

我们可以通过使用逻辑门和输入信号来计算输出结果。

下面是一个典型的全加器电路的设计:首先,我们将输入信号连接到三个输入端口。

一个输入端口用于接收两个输入二进制数,另一个输入端口用于接收进位。

接下来,我们将输入信号与逻辑门连接起来。

我们可以使用两个异或门来实现和位的计算,然后使用一个与门计算进位。

最后,我们将输出信号连接到两个输出端口。

一个输出端口用于输出和位,另一个用于输出进位位。

在实际设计中,我们需要综合考虑多个全加器的连接,以实现更复杂的计算。

这可以通过将多个全加器链接成一个加法器来实现。

加法器是一个包含多个全加器的数字电路,可以将更长的二进制数相加。

总结起来,全加器是一个重要的数字电路组件,用于将两个二进制数相加。

在全加器的设计过程中,我们需要考虑输入信号的处理、逻辑门的选择、进位的传递、和输出结果的计算。

通过合理选择逻辑门和连接输入输出信号,我们可以实现一个高效的全加器。

1位全加器的设计max

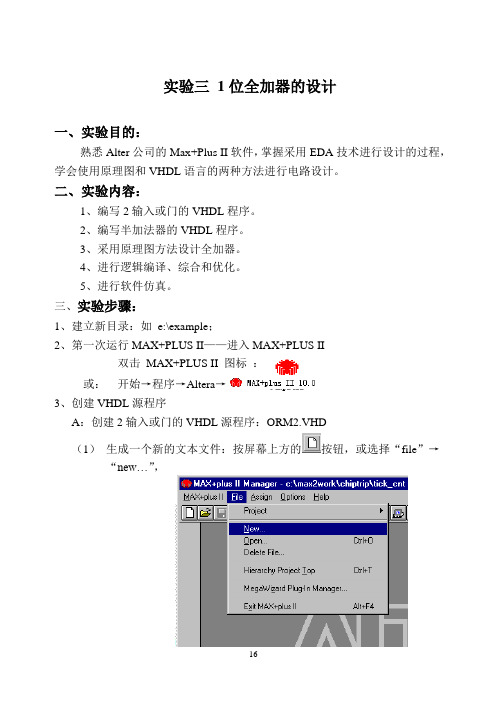

实验三1位全加器的设计一、实验目的:熟悉Alter公司的Max+Plus II软件,掌握采用EDA技术进行设计的过程,学会使用原理图和VHDL语言的两种方法进行电路设计。

二、实验内容:1、编写2输入或门的VHDL程序。

2、编写半加法器的VHDL程序。

3、采用原理图方法设计全加器。

4、进行逻辑编译、综合和优化。

5、进行软件仿真。

三、实验步骤:1、建立新目录:如e:\example;2、第一次运行MAX+PLUS II——进入MAX+PLUS II双击MAX+PLUS II 图标:或:开始→程序→Altera→3、创建VHDL源程序A:创建2输入或门的VHDL源程序:ORM2.VHD(1)生成一个新的文本文件:按屏幕上方的按钮,或选择“file”→“new…”,出现对话框:选择Text Editor file(文本编辑方式),然后按下OK按钮,会出现一个无标题的文本编辑窗口——Untitled-Text Editor。

(2)在编文本辑窗口中输入2输入或门的VHDL源程序:ORM2.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ORM2 ISPORT (A,B: IN STD_LOGIC;C: OUT STD_LOGIC);END ORM2;ARCHITECTURE ART1 OF ORM2 ISBEGINC<=A OR B;END ARCHITECTURE ART1;(3)保存文件:按工具栏中的按钮,或选择File→Save,出现对话框:在File Name(文件名)栏中输入文件名,如ORM2.vhd在驱动器选择栏选刚刚建立的项目路径所在的驱动器,如e:在路径栏选择所建立的项目路径,如:example在Automatic Extension(自动扩展名)的下拉菜单中选择.vhd按键,就把输入的文件存放在了目录e:\example中了。

此时,所有的标识符都变色。

一位全加器VHDL的设计实验报告

EDA技术及应用实验报告——一位全加器VHDL的设计班级:XXX姓名:XXX学号:XXX一位全加器的VHDL设计一、实验目的:1、学习MAX+PLUSⅡ软件的使用,包括软件安装及基本的使用流程。

2、掌握用VHDL设计简单组合电路的方法和详细设计流程。

3、掌握VHDL的层次化设计方法。

二、实验原理:本实验要用VHDL输入设计方法完成1位全加器的设计。

1位全加器可以用两个半加器及一个或门连接构成,因此需要首先完成半加器的VHDL设计。

采用VHDL层次化的设计方法,用文本编辑器设计一个半加器,并将其封装成模块,然后在顶层调用半加器模块完成1位全加器的VHDL设计。

三、实验内容和步骤:1、打开文本编辑器,完成半加器的设计。

2、完成1位半加器的设计输入、目标器件选择、编译。

3、打开文本编辑器,完成或门的设计。

4、完成或门的设计输入、目标器件选择、编译。

5、打开文本编辑器,完成全加器的设计。

6、完成全加器的设计输入、目标器件选择、编译。

7、全加器仿真8、全加器引脚锁定四、结果及分析:该一位加法器是由两个半加器组成,在半加器的基础上,采用元件的调用和例化语句,将元件连接起来,而实现全加器的VHDL编程和整体功能。

全加器包含两个半加器和一或门,1位半加器的端口a和b分别是两位相加的二进制输入信号,h是相加和输出信号,c是进位输出信号。

构成的全加器中,A,B,C分别是该一位全加器的三个二进制输入端,H是进位端,Ci是相加和输出信号的和,下图是根据试验箱上得出的结果写出的真值表:信号输入端信号输出端Ai Bi Ci Si Ci0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1。

EXP01实验一 一位全加器设计

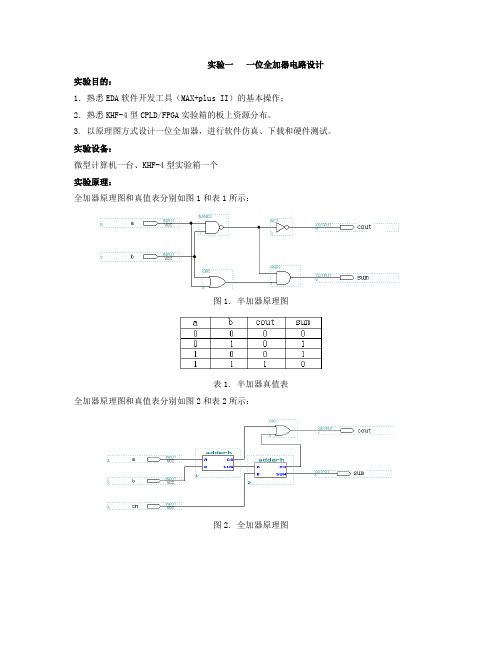

实验一一位全加器电路设计实验目的:1.熟悉EDA软件开发工具(MAX+plus II)的基本操作;2.熟悉KHF-4型CPLD/FPGA实验箱的板上资源分布。

3. 以原理图方式设计一位全加器,进行软件仿真、下载和硬件测试。

实验设备:微型计算机一台、KHF-4型实验箱一个实验原理:全加器原理图和真值表分别如图1和表1所示:图1. 半加器原理图表1. 半加器真值表全加器原理图和真值表分别如图2和表2所示:图2. 全加器原理图表2. 全加器真值表实验步骤:1)打开MAX+plus II设计软件。

2)新建图形编辑文件(File/New/Graphic Edit file),在文件空白处双击鼠标左键(或选择菜单Symbol/Enter Symbol)打开添加符号对话框(Enter Symbol),在“Symbol Libraries”框中双击选择“../maxplus2/max2lib/prim”库,在Symbol Files添加半加器原理图中各元件、输入(input)和输出(output)管脚,修改管脚名称后完成半加器原理图的绘制如图1;保存文件到具体设计目下。

图3.新建文件、添加符号和保存文件3)将半加器文件设为顶层文件(File/Project/Set Project to Current File),打开编译器(MAX+plus II/Complier)进行编译综合。

图4.设为顶层和编译4)创建半加器符号(File/Creat Default Symble)。

5)新建图形编辑文件(File/New/Graphic Edit file),在文件空白处双击鼠标左键打开添加符号对话框(Enter Symbol),从“File Symbol”框中调用半加器符号,完成全加器原理图的绘制如图2,保存文件到具体设计目录。

6)将全加器文件设为顶层文件,打开编译器进行编译综合。

7)新建波形编辑文件(File/New/Waveform Edit file),添加节点信号(在Name下点击鼠标右键选择Enter Nodes from SNF…)并编辑输入信号波形;保存(File/Save)波形文件(按默认文件名点击OK保存)。

实验一--一位全加器的原理图设计【范本模板】

桂林电子科技大学实验报告2015-2016学年第二学期开课单位海洋信息工程学院适用年级、专业13级电子信息工程课程名称EDA技术与应用主讲教师覃琴实验名称一位全加器学号1316030515姓名魏春梅实验一一位全加器的原理图设计一、实验目的①掌握Quartus II原理图输入法的编辑、编译(综合)、仿真和编程下载的操作过程.②用原理图输入法设计全加器电路,并通过电路仿真和硬件验证,进一步了解全加器的功能.③熟悉EDA实训仪的使用方法。

二、实验原理考虑来自低位来的进位的加法运算称为”全加”,能实现全加运算的电路称为全加器.1位全加器的真值表如表1。

1所列,表中的A、B是两个一位二进制加数的输入端。

CI是来自低位来的进位输入端。

SO是和数输出端,CO是向高位的进位输出端。

根据真值表写出电路输出与输入之间的逻辑关系表达式为:A B CI SO CO三、实验设备①EDA实训仪1台.②计算机1台(装有Quartus II软件)。

四、实验内容在Quartus II软件中,采用原理图输入法设计1位的全加器电路,编辑、编译(综合)、仿真,引脚锁定,并下载到EDA实训仪中进行验证。

注:用EDA实训仪上的拨动开关S1、S2、SO分别作为加数A、加数B、低位进位输入端CI,用发光二极管L1、L0分别作为和输出端SO、仅为输出端CO。

五、实验预习要求①查阅资料,复习有关全加器的内容,并认真阅读实验指导书,分析、掌握实验原理.②预习理论课本有关Quartus II软件的使用方法,并简要地写出Quartus II软件的操作步骤。

③复习数字逻辑电路有关全加器的内容,设计1位全加器的逻辑电路图。

1、实验电路图路径:E/1316030515/adder2、实验波形仿真图路径:E/1316030515/adder3、实验结果图六、实验总结①用Quartus II软件的原理图输入法进行数字电路设计的方法及步骤。

1、建立工程项目(文件夹、工程名、芯片选择);2、编辑设计文件(元件、连线、输入输出、检查电路正确性);3、时序仿真(波形验证设计结果);4、引脚锁定(参考文件锁定输入输出引脚);5、编译下载;6、硬件调试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一1位全加器的设计

一、实验目的

1.熟悉ISE软件的使用;

2.熟悉下载平台的使用;

3.掌握利用层次结构描述法设计电路。

二、实验原理及说明

由数字电路知识可知,一位全加器可由两个一位半加器与一个或门构成,其原理图如图1所示。

该设计利用层次结构描述法,首先设计半加器电路,将其打包为半加器模块;然后在顶层调用半加器模块组成全加器电路;最后将全加器电路编译下载到实验板,其中a,b,cin 信号可采用实验箱上SW0,SW1,SW2键作为输入,输出sum,cout信号采用发光二极管LED3,LED2来显示。

图1 全加器原理图

三、实验步骤

1.在ISE软件下创建一工程,工程名为full_adder,工程路径在E盘,或DATA盘,

并以学号为文件夹,注意不要有中文路径,注意:不可将工程放到默认的软件安装

目录中。

芯片名为Spartan3E系列的XC3S500E-PQG208

2.新建Verilog HDL文件,首先设计半加器,输入如下源程序;

module half_adder(a,b,s,co);

input a,b;

output s,co;

wire s,co;

assign co=a & b;

assign s=a ^ b;

endmodule

3.保存半加器程序为half_adder.v,通过HDL Bench画仿真波形,获得仿真用激励文

件,随后进行功能仿真、时序仿真,验证设计的正确性,观察两种仿真波形的差异。

4.在Design窗口中,选择Design Utilities→Create Schematic Symbol创建半加器模

块;

5.新建一原理图(Schematic)文件,在原理图中调用两个半加器模块、一个或门模块,

按照图1所示连接电路,并连接输入、输出引脚。

完成后另保存full_adder.sch。

6.对设计进行综合,如出现错误请按照错误提示进行修改。

7.HDL Bench画仿真波形,获得仿真用激励文件,分别进行功能与时序仿真,验证全

加器的逻辑功能,观察两类波形的差异。

8.根据下载板的情况锁定引脚

9.下载,采用JATG方式进行下载,通过SW0,SW1,SW2输入,观察的LED2,LED3,

亮灭情况,验证全加器的逻辑功能。

四、思考题

1.为什么在实验步骤3中,将半加器保存为half_adder,可否保存为full_adder?

2.对电路进行功能仿真与时序仿真时,发现二者有什么样的区别?

3.为什么要进行引脚锁定?

4.采用层次结构法描述电路有什么样的优点?。