一位全加器的设计

一位全加器的设计

一位全加器的设计(总23页) --本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--课程设计任务书学生姓名:袁海专业班级:电子1303班指导教师:封小钰工作单位:信息工程学院题目: 一位全加器的设计初始条件:计算机、ORCAD软件,L-EDIT软件要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)1、课程设计工作量:1周2、技术要求:(1)学习ORCAD软件,L-EDIT软件。

(2)设计一个一位全加器电路。

(3)利用ORCAD软件对该电路进行系统设计、电路设计,利用L-EDIT软件进行版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。

学习ORCAD软件和L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。

对一位全加器电路进行设计仿真工作,完成课设报告的撰写。

提交课程设计报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要........................................................ 错误!未定义书签。

ABSTRACT .................................................... 错误!未定义书签。

1绪论...................................................... 错误!未定义书签。

集成电路发展现状........................................ 错误!未定义书签。

集成电路版图工具L-edit简介............................. 错误!未定义书签。

一位全加器的设计

一位全加器的设计全加器的主要作用是将两个二进制数相加,并产生一个结果和一个进位。

在设计全加器时,我们需要考虑以下几个方面:输入信号的处理、逻辑门的选择、进位的传递、和输出结果的计算。

首先,我们需要考虑输入信号的处理。

一个全加器需要接收两个二进制数和一个进位作为输入信号。

每个输入信号都可以用一个二进制位表示,这些位可以通过电路的输入端口进入电路。

在设计全加器时,我们需要确定如何使用这些输入信号。

其次,我们需要选择逻辑门来实现全加器。

逻辑门是数字电路的基本组件,通常用于实现计算和逻辑运算。

在设计全加器时,我们可以使用与门、或门和异或门来完成计算。

接下来,我们需要实现进位的传递。

当两个二进制数相加时,如果它们的和超过了二进制数能够表示的范围,就会产生一个进位。

为了实现进位的传递,我们可以使用逻辑门来判断是否产生了进位,并将进位传递到高位。

最后,我们需要计算输出结果。

一个全加器的输出结果是一个和位和一个进位位。

和位表示两个输入位的和,进位位表示是否产生了进位。

我们可以通过使用逻辑门和输入信号来计算输出结果。

下面是一个典型的全加器电路的设计:首先,我们将输入信号连接到三个输入端口。

一个输入端口用于接收两个输入二进制数,另一个输入端口用于接收进位。

接下来,我们将输入信号与逻辑门连接起来。

我们可以使用两个异或门来实现和位的计算,然后使用一个与门计算进位。

最后,我们将输出信号连接到两个输出端口。

一个输出端口用于输出和位,另一个用于输出进位位。

在实际设计中,我们需要综合考虑多个全加器的连接,以实现更复杂的计算。

这可以通过将多个全加器链接成一个加法器来实现。

加法器是一个包含多个全加器的数字电路,可以将更长的二进制数相加。

总结起来,全加器是一个重要的数字电路组件,用于将两个二进制数相加。

在全加器的设计过程中,我们需要考虑输入信号的处理、逻辑门的选择、进位的传递、和输出结果的计算。

通过合理选择逻辑门和连接输入输出信号,我们可以实现一个高效的全加器。

1位全加器的设计max

实验三1位全加器的设计一、实验目的:熟悉Alter公司的Max+Plus II软件,掌握采用EDA技术进行设计的过程,学会使用原理图和VHDL语言的两种方法进行电路设计。

二、实验内容:1、编写2输入或门的VHDL程序。

2、编写半加法器的VHDL程序。

3、采用原理图方法设计全加器。

4、进行逻辑编译、综合和优化。

5、进行软件仿真。

三、实验步骤:1、建立新目录:如e:\example;2、第一次运行MAX+PLUS II——进入MAX+PLUS II双击MAX+PLUS II 图标:或:开始→程序→Altera→3、创建VHDL源程序A:创建2输入或门的VHDL源程序:ORM2.VHD(1)生成一个新的文本文件:按屏幕上方的按钮,或选择“file”→“new…”,出现对话框:选择Text Editor file(文本编辑方式),然后按下OK按钮,会出现一个无标题的文本编辑窗口——Untitled-Text Editor。

(2)在编文本辑窗口中输入2输入或门的VHDL源程序:ORM2.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ORM2 ISPORT (A,B: IN STD_LOGIC;C: OUT STD_LOGIC);END ORM2;ARCHITECTURE ART1 OF ORM2 ISBEGINC<=A OR B;END ARCHITECTURE ART1;(3)保存文件:按工具栏中的按钮,或选择File→Save,出现对话框:在File Name(文件名)栏中输入文件名,如ORM2.vhd在驱动器选择栏选刚刚建立的项目路径所在的驱动器,如e:在路径栏选择所建立的项目路径,如:example在Automatic Extension(自动扩展名)的下拉菜单中选择.vhd按键,就把输入的文件存放在了目录e:\example中了。

此时,所有的标识符都变色。

实验一1 1位全加器的设计

实验一1位全加器的设计一、实验目的1.熟悉ISE软件的使用;2.熟悉下载平台的使用;3.掌握利用层次结构描述法设计电路。

二、实验原理及说明由数字电路知识可知,一位全加器可由两个一位半加器与一个或门构成,其原理图如图1所示。

该设计利用层次结构描述法,首先设计半加器电路,将其打包为半加器模块;然后在顶层调用半加器模块组成全加器电路;最后将全加器电路编译下载到实验板,其中a,b,cin 信号可采用实验箱上SW0,SW1,SW2键作为输入,输出sum,cout信号采用发光二极管LED3,LED2来显示。

图1 全加器原理图三、实验步骤1.在ISE软件下创建一工程,工程名为full_adder,工程路径在E盘,或DATA盘,并以学号为文件夹,注意不要有中文路径,注意:不可将工程放到默认的软件安装目录中。

芯片名为Spartan3E系列的XC3S500E-PQG2082.新建Verilog HDL文件,首先设计半加器,输入如下源程序;module half_adder(a,b,s,co);input a,b;output s,co;wire s,co;assign co=a & b;assign s=a ^ b;endmodule3.保存半加器程序为half_adder.v,通过HDL Bench画仿真波形,获得仿真用激励文件,随后进行功能仿真、时序仿真,验证设计的正确性,观察两种仿真波形的差异。

4.在Design窗口中,选择Design Utilities→Create Schematic Symbol创建半加器模块;5.新建一原理图(Schematic)文件,在原理图中调用两个半加器模块、一个或门模块,按照图1所示连接电路,并连接输入、输出引脚。

完成后另保存full_adder.sch。

6.对设计进行综合,如出现错误请按照错误提示进行修改。

7.HDL Bench画仿真波形,获得仿真用激励文件,分别进行功能与时序仿真,验证全加器的逻辑功能,观察两类波形的差异。

一位全加器的实验报告

一位全加器的实验报告一位全加器的实验报告摘要:本实验旨在通过搭建一位全加器电路,探究数字电路中的加法运算原理。

通过实验,我们成功验证了全加器的功能,并观察到了其在二进制加法中的作用。

实验结果表明,全加器是一种重要的数字电路元件,能够实现多位二进制数的相加运算。

引言:全加器是一种常见的数字电路元件,用于实现二进制数的相加运算。

它能够处理两个输入位和一个进位位,并输出一个和位和一个进位位。

全加器的设计和实现对于数字电路的理解和应用具有重要意义。

本实验将通过搭建一位全加器电路,探究其工作原理和应用。

材料与方法:1. 逻辑门:与门、或门、异或门、非门2. 连线材料:导线、电源线3. 电源:直流电源4. 示波器:用于观察电路输出波形实验步骤:1. 按照电路图搭建一位全加器电路,包括两个输入位A和B,一个进位位Cin,一个和位S和一个进位位Cout。

2. 将电源线连接至电路,确保电路正常供电。

3. 分别将输入位A和B的电平信号输入到与门和异或门中,将进位位Cin的电平信号输入到与门中。

4. 将与门和异或门的输出信号输入到或门中,得到和位S的输出信号。

5. 将与门的输出信号输入到与非门中,得到进位位Cout的输出信号。

6. 使用示波器观察和位S和进位位Cout的波形。

结果与讨论:通过实验观察,我们得到了一位全加器的输出波形。

当输入位A和B均为0时,和位S和进位位Cout均为0;当输入位A和B均为1时,和位S为0,进位位Cout为1;当输入位A和B中有一个为1时,和位S为1,进位位Cout为0;当输入位A和B均为1时,和位S和进位位Cout均为1。

这一结果与全加器的逻辑运算规则相符,验证了全加器电路的正确性。

全加器在二进制加法中起到了关键作用。

通过将多个全加器连接起来,我们可以实现多位二进制数的相加运算。

在实际应用中,全加器被广泛应用于计算机的算术逻辑单元(ALU)中,用于实现加法和其他运算。

结论:通过本实验,我们成功搭建了一位全加器电路,并验证了其在二进制加法中的功能。

EXP01实验一 一位全加器设计

实验一一位全加器电路设计实验目的:1.熟悉EDA软件开发工具(MAX+plus II)的基本操作;2.熟悉KHF-4型CPLD/FPGA实验箱的板上资源分布。

3. 以原理图方式设计一位全加器,进行软件仿真、下载和硬件测试。

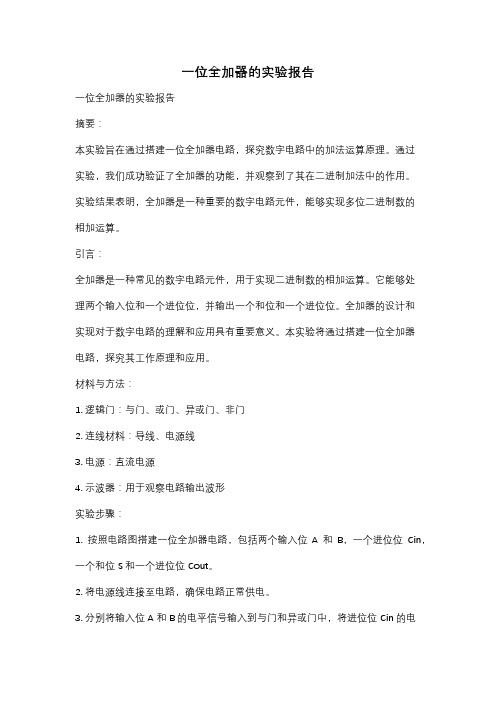

实验设备:微型计算机一台、KHF-4型实验箱一个实验原理:全加器原理图和真值表分别如图1和表1所示:图1. 半加器原理图表1. 半加器真值表全加器原理图和真值表分别如图2和表2所示:图2. 全加器原理图表2. 全加器真值表实验步骤:1)打开MAX+plus II设计软件。

2)新建图形编辑文件(File/New/Graphic Edit file),在文件空白处双击鼠标左键(或选择菜单Symbol/Enter Symbol)打开添加符号对话框(Enter Symbol),在“Symbol Libraries”框中双击选择“../maxplus2/max2lib/prim”库,在Symbol Files添加半加器原理图中各元件、输入(input)和输出(output)管脚,修改管脚名称后完成半加器原理图的绘制如图1;保存文件到具体设计目下。

图3.新建文件、添加符号和保存文件3)将半加器文件设为顶层文件(File/Project/Set Project to Current File),打开编译器(MAX+plus II/Complier)进行编译综合。

图4.设为顶层和编译4)创建半加器符号(File/Creat Default Symble)。

5)新建图形编辑文件(File/New/Graphic Edit file),在文件空白处双击鼠标左键打开添加符号对话框(Enter Symbol),从“File Symbol”框中调用半加器符号,完成全加器原理图的绘制如图2,保存文件到具体设计目录。

6)将全加器文件设为顶层文件,打开编译器进行编译综合。

7)新建波形编辑文件(File/New/Waveform Edit file),添加节点信号(在Name下点击鼠标右键选择Enter Nodes from SNF…)并编辑输入信号波形;保存(File/Save)波形文件(按默认文件名点击OK保存)。

设计一位全加器的设计流程概述,基本步骤

设计一位全加器的设计流程概述,基本步骤下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!全加器设计流程概述全加器是数字逻辑电路中的一个重要组成部分,主要用于实现二进制数的加法运算。

EDA之1位全加器

EDA技术实验教案实验一1位全加器原理图输入设计一、实验目的1、熟悉MAX+plusII软件的基本使用方法。

2、熟悉GW48-ES EDA实验开发系统的基本使用方法。

3、了解原理图输入设计方法。

二、实验内容设计并调试好一个1位二进制全加器,并用GW48-ES EDA实验开发系统(拟采用的实验芯片的型号为EPF10K20TC144-4或EP1K30TC144-3)进行系统仿真、硬件验证。

设计1位二进制全加器时要求先用基本门电路设计一个1位二进制半加器,再由基本门电路和1位二进制半加器构成1位二进制全加器。

三、实验条件1、开发条件:MAX+plusII2、实验设备:GW48-ES EDA实验开发系统、联想电脑3、拟用芯片:EPF10K20TC144-4或EP1K30TC144-3四、实验设计半加器(h_adder.gdf)全加器(f_adder.gdf)实验结果半加器仿真波形半加器引脚锁定实验芯片:EPF10K20TC144-4选用模式:模式5设计实体I/O标识I/O来源/去向结构图上的信号名芯片引脚号a 键1 PIO0 8b 键2 PIO1 9so 二极管D1 PIO8 20co 二极管D2 PIO9 21 全加器仿真波形全加器引脚锁定实验芯片:EPF10K20TC144-4选用模式:模式5设计实体I/O标识I/O来源/去向结构图上的信号名芯片引脚号ain 键1 PIO0 8bin 键2 PIO1 9cin 键3 PIO2 10sum 二极管D1 PIO8 20cout 二极管D2 PIO9 21全加器真值表ain 0 1 0 1 0 1 0 1 bin 0 0 1 1 0 0 1 1 cin 0 0 0 0 1 1 1 1 sum 0 1 1 0 1 0 0 1 cout 0 0 0 1 0 1 1 1实验二1位全加器VHDL文本输入设计一、实验目的1、熟悉MAX+plusII软件的基本使用方法。

1位全加器电路设计

1位全加器电路设计全加器是一种组合逻辑电路,用于将两个二进制数相加,并输出和及进位。

一个1位全加器包含两个输入(被加数和加数)和两个输出(和和进位)。

全加器具有一个额外的输入(进位输入)来接收来自上一位的进位。

一个1位全加器可以使用与门(AND)、异或门(XOR)和或门(OR)来实现。

设计思路如下:1.将两个输入(被加数和加数)分别与一个异或门(XOR)连接,得到一个输出(和)。

2.将两个输入(被加数和加数)分别与一个与门(AND)连接,得到一个输出(进位)。

3.将两个输入的与门(AND)的输出(进位)与进位输入进行异或运算,得到最终的进位输出。

4.将输出(和)和最终进位输出作为全加器的输出。

下面是我对1位全加器的详细设计:首先,我们需要定义输入和输出信号:输入信号:A, B, Cin(被加数,加数,进位输入)输出信号:S, Cout(和,进位输出)接下来,我们可以按照设计思路,逐步实现1位全加器:Step 1: 设计异或门(XOR)的电路将输入A和B连接到一个异或门,得到一个信号X(X=AXORB)Step 2: 设计与门(AND)的电路将输入A和B连接到一个与门,得到一个信号Y(Y=AANDB)Step 3: 设计第一个异或门(XOR)的电路将信号X和进位输入Cin连接到一个异或门,得到一个信号Z(Z = X XOR Cin)Step 4: 设计与门(AND)的电路将信号X和进位输入Cin连接到一个与门,得到一个信号CarryOut (CarryOut = X AND Cin)Step 5: 设计或门(OR)的电路将信号Y和信号CarryOut连接到一个或门,得到输出信号Cout (Cout = Y OR CarryOut)Step 6: 设计或门(OR)的电路将信号X和信号Z连接到一个或门,得到输出信号S(S=XORZ)最后,我们将输入A、B和Cin以及输出S、Cout连接到1位全加器的电路中,即可实现1位全加器。

实验一--一位全加器的原理图设计【范本模板】

桂林电子科技大学实验报告2015-2016学年第二学期开课单位海洋信息工程学院适用年级、专业13级电子信息工程课程名称EDA技术与应用主讲教师覃琴实验名称一位全加器学号1316030515姓名魏春梅实验一一位全加器的原理图设计一、实验目的①掌握Quartus II原理图输入法的编辑、编译(综合)、仿真和编程下载的操作过程.②用原理图输入法设计全加器电路,并通过电路仿真和硬件验证,进一步了解全加器的功能.③熟悉EDA实训仪的使用方法。

二、实验原理考虑来自低位来的进位的加法运算称为”全加”,能实现全加运算的电路称为全加器.1位全加器的真值表如表1。

1所列,表中的A、B是两个一位二进制加数的输入端。

CI是来自低位来的进位输入端。

SO是和数输出端,CO是向高位的进位输出端。

根据真值表写出电路输出与输入之间的逻辑关系表达式为:A B CI SO CO三、实验设备①EDA实训仪1台.②计算机1台(装有Quartus II软件)。

四、实验内容在Quartus II软件中,采用原理图输入法设计1位的全加器电路,编辑、编译(综合)、仿真,引脚锁定,并下载到EDA实训仪中进行验证。

注:用EDA实训仪上的拨动开关S1、S2、SO分别作为加数A、加数B、低位进位输入端CI,用发光二极管L1、L0分别作为和输出端SO、仅为输出端CO。

五、实验预习要求①查阅资料,复习有关全加器的内容,并认真阅读实验指导书,分析、掌握实验原理.②预习理论课本有关Quartus II软件的使用方法,并简要地写出Quartus II软件的操作步骤。

③复习数字逻辑电路有关全加器的内容,设计1位全加器的逻辑电路图。

1、实验电路图路径:E/1316030515/adder2、实验波形仿真图路径:E/1316030515/adder3、实验结果图六、实验总结①用Quartus II软件的原理图输入法进行数字电路设计的方法及步骤。

1、建立工程项目(文件夹、工程名、芯片选择);2、编辑设计文件(元件、连线、输入输出、检查电路正确性);3、时序仿真(波形验证设计结果);4、引脚锁定(参考文件锁定输入输出引脚);5、编译下载;6、硬件调试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计任务书学生:袁海专业班级:电子1303班指导教师:封小钰工作单位:信息工程学院题目: 一位全加器的设计初始条件:计算机、ORCAD软件,L-EDIT软件要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)1、课程设计工作量:1周2、技术要求:(1)学习ORCAD软件,L-EDIT软件。

(2)设计一个一位全加器电路。

(3)利用ORCAD软件对该电路进行系统设计、电路设计,利用L-EDIT软件进行版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《理工大学课程设计工作规》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规。

时间安排:2016.12.30布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。

2016.12.31-2017.1.2学习ORCAD软件和L-EDIT软件,查阅相关资料,复习所设计容的基本理论知识。

2017.1.3-2017.1.4对一位全加器电路进行设计仿真工作,完成课设报告的撰写。

2017.1.5 提交课程设计报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (I)ABSTRACT (I)1绪论 (1)1.1集成电路发展现状 (1)1.2集成电路版图工具L-edit简介 (1)2全加器原理及一位全加器原理图设计 (1)2.1一位全加器原理简介 (1)2.2实现一位全加器功能的原理图设计 (1)2.2.1一位全加器原理图 (1)2.2.2基于ORCAD的一位全加器设计 (1)2.2.3 一位全加器的电路图仿真 (1)3一位全加器的版图设计 (1)3.1确定一位全加器版图结构 (1)3.2源漏共享缩小版图面积 (1)3.3 版图所需基础器件绘制编辑 (1)3.3.1 PMOS、NMOS等基础器件编辑 (1)3.3.2 两输入与非门与异或门的绘制编辑 (1)3.3.3源漏共享得到版图 (1)3.4 绘制最终一位全加器版图 (1)4心得体会 (1)5参考文献 (1)摘要加法运算是数字系统中最基本的运算,为了更好地利用加法器实现减法、乘法、除法等运算,需要对全加器进行功能仿真设计和分析。

另外通过全加器可以对其它相关电路有所了解。

本文用对一位全加器进行了全面的分析,根据其逻辑功能及结构,分别利用ORCAD 软件和L-EDIT软件对电路进行了系统设计、电路设计和版图设计。

在画电路元器件的版图需要熟练使用版图设计软件,熟悉电路知识和版图设计规则,掌握MOS管等基本元器件的部结构及版图画法,通过对门电路和一位全加器电路的版图设计,熟悉电路元器件的版图布局,元器件版图间的连线等设计方法,在版图设计规则无误的前提下做到电路的版图结构紧密,金属连线达到最优化的目的。

关键词:ORCAD软件;L-EDIT软件;全加器;电路设计;版图设计ABSTRACTAddition operation is the basic operation of the digital system, In order to achieve much better use of the adder subtraction, multiplication, division and other operations, The need for full adder functional simulation design and analysis is necessary .The paper has a comprehensive analysis to the full adder. According to its logic function and structure, the circuit design, circuit design and layout design are carried out by ORCAD software and L-EDIT software respectively. In the drawing circuit components layout proficiency in the use of layout design software, familiar with the circuit knowledge and layout design rules, master MOS tube and other basic components of the internal structure and layout drawing method, through the gate circuit and a full adder circuit layout design , Familiar with the layout of the circuit components, wiring layout between components and other design methods, layout rules in the correct layout under the premise of the circuit structure close to the metal connection to achieve the purpose of optimization.KEY WORDS:ORCAD software; L-edit software; a full adder,circuit design; layout design1绪论1.1集成电路发展现状集成电路的出现与飞速发展彻底改变了人类文明和人们日常生活的面目。

近几年,中国集成电路产业取得了飞速发展。

中国集成电路产业已经成为全球半导体产业关注的焦点,即使在全球半导体产业陷入有史以来程度最严重的低迷阶段时,中国集成电路市场仍保持了两位数的年增长率,凭借巨大的市场需求、较低的生产成本、丰富的人力资源,以及经济的稳定发展和宽松的政策环境等众多优势条件,以京津唐地区、长江三角洲地区和珠江三角洲地区为代表的产业基地迅速发展壮大,制造业、设计业和封装业等集成电路产业各环节逐步完善。

目前,中国集成电路产业已经形成了IC设计、制造、封装测试三业及支撑配套业共同发展的较为完善的产业链格局,随着IC设计和芯片制造行业的迅猛发展,国集成电路价值链格局继续改变,其总体趋势是设计业和芯片制造业所占比例迅速上升。

作为电子科学与技术专业的一门重要的实践课程,集成电路课程设计主要目的是使学生熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础。

提高学生综合运用已掌握的知识,利用相关软件,进行集成电路芯片的能力。

集成电路设计的流程:系统设计、逻辑设计、电路设计(包括:布局布线验证)、版图设计版图后仿真(加上寄生负载后检查设计是否能够正常工作)。

1.2集成电路版图工具L-edit简介L-Edit是一个图形编辑器,它允许生成和修改集成电路掩模版上的几何图形。

鼠标接口允许用户执行一般图形操作。

既可使用鼠标访问下拉菜单也可以使用键盘来调用L-Edit 命令。

(1) 文件和单元使用文件、单元、连接器、掩模基元来描述布局设计,一个文件可以有任意多个单元组成,在典型设计中,这些单元可以有层次关系,也可以相互独立,单元可以包括任意数量的掩模基元和连接件,以及两者的组合,掩模单元由矩形、图、直线、多边形和技术层端口组成。

(2) 层次完全层次性的单元可以包含别的单元的连接件。

一个连接件是一个单元的“拷贝”;如果编辑连接单元,这种改变将反映到那个单元的所有连接件上。

L-Edit对层次不作限制。

单元可以包含单元的连接件,被包含的单元又可以包含别的连接件。

这样就形成了单元层次。

在层次结构中可以有任意级。

L-Edit不能用于分离的层次结构,连接件和基元几何图形都可以存在于层次结构的任意级中的同一单元。

(3) 单元设计L-Edit是一个低层次的,全定掩模编辑器,该编辑器不能执行层的自动转换。

(4) 层规划L-Edit是一个高层规划工具。

用户可以选择要显示的连接件,它显示一个边框,中间显示单元名,也可以显示掩模几何图形。

使用部隐藏时,可以操作用户设计的大型芯片级块,以获得所需要的层规划。

用户可使用用于操作基元的几何图形的命令。

(5) 文件格式L-Edit能输出两种掩模布局交换格式(CIF,GDSⅡ)以及Tanner Research公司的二进制数据库的格式TDB(Tanner Data Base),L-Edit能够读取CIF(Caltech Intermediate Form)和TDB文件。

(6) L-Edit支持对象L-Edit支持九种对象:框、直线、图、多边形、圆形、扇形、圆环形,端口和单元连接元件,所有对象可以用同样的方式来建立和编辑,移动和选择。

L-Edit不能对用户绘制的图形进行修改。

L-Edit是面向对象的设计工具,而不是位图编辑器。

2全加器原理及一位全加器原理图设计2.1一位全加器原理简介一位全加器(FA)的逻辑表达式为:1i i i i S A B C =-⊕⊕ (2-1)11i i i i i i i C A b B C A C --=++(2-2)其中Ai,Bi 为要相加的数,Ci-1为进位输入;Si 为和,Ci 是进位输出;0如果要实现多位加法可以进行级联,就是串起来使用;比如32位+32位,就需要32个全加器;这种级联就是串行结构速度慢,如果要并行快速相加可以用超前进位加法,超前进位加法前查阅相关资料; 如果将全加器的输入置换成A 和B 的组合函数Xi 和Y (S0…S3控制),然后再将X,Y 和进位数通过全加器进行全加,就是ALU 的逻辑结构。

即 X=f (A ,B)Y=f (A ,B )不同的控制参数可以得到不同的组合函数,因而能够实现多种算术运算和逻辑运算。

对两个一位二进制数及来自低位的“进位”进行相加,产生本位“和”及向高位“进位”。

全加器有三个输入端,二个输出端,其真值表如下所示。

表2-1 一位全加器真值表1 0 0 1 0 1 1 1 0 1 1 1 1 0 0 10 11 12.2实现一位全加器功能的原理图设计2.2.1一位全加器原理图根据一位全加器逻辑表达式和真值表设计其原理图如图2-1图2-1 一位全加器原理图对一位全加器逻辑表达式进行分析而后转化成为与非的形式便得到如上图所示的原理图。

该原理图由2个异或门和3个两输入与非门构成并实现。

2.2.2基于ORCAD的一位全加器设计1、异或门的原理图设计与编辑异或门(英语:Exclusive-OR gate,简称XOR gate,又称EOR gate、ExOR gate)是数字逻辑中实现逻辑异或的逻辑门。