数字电子技术基础习题册答案

《数字电子技术基础》课后习题答案

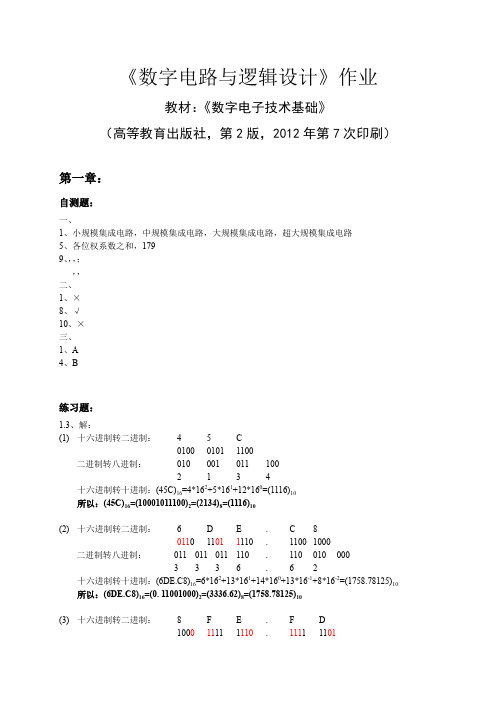

《数字电路与逻辑设计》作业教材:《数字电子技术基础》(高等教育出版社,第2版,2012年第7次印刷)第一章:自测题:一、1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路5、各位权系数之和,1799、,,;,,二、1、×8、√10、×三、1、A4、B练习题:1.3、解:(1) 十六进制转二进制: 4 5 C0100 0101 1100二进制转八进制:010 001 011 1002 13 4十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10所以:(45C)16=(10001011100)2=(2134)8=(1116)10(2) 十六进制转二进制: 6 D E . C 80110 1101 1110 . 1100 1000 二进制转八进制:011 011 011 110 . 110 010 0003 3 3 6 . 6 2十六进制转十进制:(6DE.C8)16=6*162+13*161+14*160+13*16-1+8*16-2=(1758.78125)10 所以:(6DE.C8)16=(0. 11001000)2=(3336.62)8=(1758.78125)10(3) 十六进制转二进制:8 F E . F D1000 1111 1110. 1111 1101二进制转八进制:100 011 111 110 . 111 111 0104 3 7 6 . 7 7 2十六进制转十进制:(8FE.FD)16=8*162+15*161+14*160+15*16-1+13*16-2=(2302.98828125)10 所以:(8FE.FD)16=(1.11111101)2=(437 6.772)8=(2302.98828125)10(4) 十六进制转二进制:7 9 E . F D0111 1001 1110 . 1111 1101二进制转八进制:011 110 011 110 . 111 111 0103 6 3 6 . 7 7 2十六进制转十进制:(79E.FD)16=7*162+9*161+14*160+15*16-1+13*16-2=(1950. )10 所以:(8FE.FD)16=0.11111101)2=(3636.772)8=(1950.98828125)101.5、解:(74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD(45.36)10 =(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD(136.45)10 =(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10 =(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD1.8、解(1)(+35)=(0 100011)原= (0 100011)补(2)(+56 )=(0 111000)原= (0 111000)补(3)(-26)=(1 11010)原= (1 11101)补(4)(-67)=(1 1000011)原= (1 1000110)补。

数字电子技术基础试题及答案

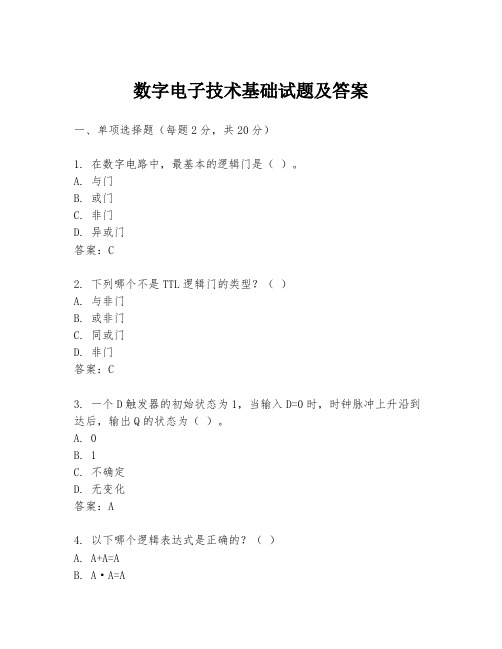

数字电子技术基础试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑门是()。

A. 与门B. 或门C. 非门D. 异或门答案:C2. 下列哪个不是TTL逻辑门的类型?()A. 与非门B. 或非门C. 同或门D. 非门答案:C3. 一个D触发器的初始状态为1,当输入D=0时,时钟脉冲上升沿到达后,输出Q的状态为()。

A. 0B. 1C. 不确定D. 无变化答案:A4. 以下哪个逻辑表达式是正确的?()A. A+A=AB. A·A=AC. A+A=0D. A·A=0答案:B5. 一个4位二进制计数器,从0000开始计数,当计数到1111时,下一个状态是()。

A. 0000B. 1000C. 10000D. 0111答案:A6. 在数字电路中,若要实现一个逻辑函数,下列哪种方法最为经济?()A. 使用与非门B. 使用或非门C. 使用与门D. 使用或门答案:A7. 一个三态输出门,当控制端为高电平时,输出状态为()。

A. 高阻态B. 低电平C. 高电平D. 低阻态答案:C8. 以下哪个是BCD码的特点?()A. 每个十进制数字对应一个唯一的二进制代码B. 每个二进制数字对应一个唯一的十进制数字C. 每个二进制数字对应一个唯一的十六进制数字D. 每个十进制数字对应多个二进制代码答案:A9. 在数字电路中,一个反相器的逻辑功能是()。

A. 与B. 或C. 非D. 异或答案:C10. 一个JK触发器在时钟脉冲上升沿到达时,如果J=1,K=0,则触发器的状态()。

A. 保持不变B. 翻转C. 置0D. 置1答案:D二、填空题(每题2分,共20分)1. 一个2输入的与门,当两个输入都为1时,输出为______。

答案:12. 在数字电路中,一个D触发器的D端输入为0,时钟脉冲上升沿到达后,输出Q的状态为______。

答案:03. 一个4位二进制计数器,如果初始状态为0101,下一个状态为______。

完整word版数字电子技术基础练习题及参考答案word文档良心出品

第一章数字电路基础第一部分基础知识一、选择题1.以下代码中为无权码的为。

A. 8421BCD码B. 5421BCD码C. 余三码D. 格雷码2.以下代码中为恒权码的为。

A.8421BCD码B. 5421BCD码C. 余三码D. 格雷码3.一位十六进制数可以用位二进制数来表示。

A. 1B. 2C. 4D. 164.十进制数25用8421BCD码表示为。

A.10 101B.0010 0101C.100101D.101015.在一个8位的存储单元中,能够存储的最大无符号整数是。

A.(256)B.(127)C.(FF)D.(255)1016 10 106.与十进制数(53.5)等值的数或代码为。

10 A.(0101 0011.0101) B.(35.8) C.(110101.1) D.(65.4)8 8421BCD1627.矩形脉冲信号的参数有。

A.周期B.占空比C.脉宽D.扫描期:数为)等值的7.与八进制数(438.8 B.(27.6) C.(27.011)3 ) D. (100111.11).A. (1001112162169. 常用的BCD码有。

码三 D.余421码格 B.雷码 C.8偶A.奇校验码10.与模拟电路相比,数字电路主要的优点有。

A.容易设计B.通用性强C.保密性好D.抗干扰能力强二、判断题(正确打√,错误的打×)1. 方波的占空比为0.5。

()2. 8421码1001比0001大。

()3. 数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

()4.格雷码具有任何相邻码只有一位码元不同的特性。

()5.八进制数(18)比十进制数(18)小。

()108)(。

1为应值上位验校的码验校奇1248在,时5数制进十送传当.6.7.在时间和幅度上都断续变化的信号是数字信号,语音信号不是数字信号。

()8.占空比的公式为:q = t / T,则周期T越大占空比q越小。

()w9.十进制数(9)比十六进制数(9)小。

数字电子技术基础习题及答案

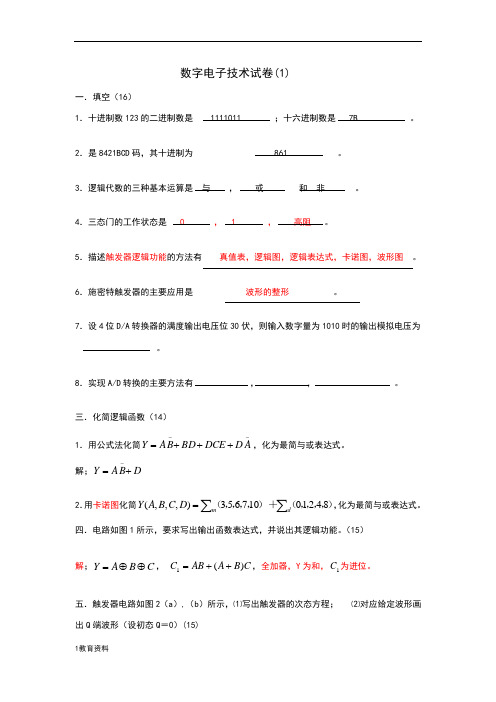

数字电子技术试卷(1)一.填空(16)1.十进制数123的二进制数是 1111011 ;十六进制数是 7B 。

2.是8421BCD 码,其十进制为 861 。

3.逻辑代数的三种基本运算是 与 , 或 和 非 。

4.三态门的工作状态是 0 , 1 , 高阻 。

5.描述触发器逻辑功能的方法有 真值表,逻辑图,逻辑表达式,卡诺图,波形图 。

6.施密特触发器的主要应用是 波形的整形 。

7.设4位D/A 转换器的满度输出电压位30伏,则输入数字量为1010时的输出模拟电压为 。

8.实现A/D 转换的主要方法有 , , 。

三.化简逻辑函数(14)1.用公式法化简--+++=A D DCE BD B A Y ,化为最简与或表达式。

解;D B A Y +=-2.用卡诺图化简∑∑=mdD C B A Y ),,,,()+,,,,(84210107653),,,(,化为最简与或表达式。

四.电路如图1所示,要求写出输出函数表达式,并说出其逻辑功能。

(15)解;C B A Y ⊕⊕=, C B A AB C )(1++=,全加器,Y 为和,1C 为进位。

五.触发器电路如图2(a ),(b )所示,⑴写出触发器的次态方程; ⑵对应给定波形画出Q 端波形(设初态Q =0)(15)解;(1)AQ Q Q n +=-+1,(2)、A Q n =+1六.试用触发器和门电路设计一个同步的五进制计数器。

(15)七.用集成电路定时器555所构成的自激多谐振荡器电路如图3所示,试画出V O ,V C 的工作波形,并求出振荡频率。

(15)数字电子技术试卷(2)二.填空(16)1.十进制数的二进制数是;十六进制数是。

2.逻辑代数中逻辑变量得取值为 0、1 。

3.组合逻辑电路的输出状态只与当前输入有关而与电路原状态无关。

4.三态门的输出有0、1、高阻,三种状态,当多个三态门的输出端连在一根总线上使用时,应注意只能有1个三态门被选通。

5.触发器的基本性质有有两个稳态,在触发信号作用下状态可相互转变,有记忆功能6.单稳态触发器的主要应用是延时。

(全)数字电子技术基础课后答案夏路易

《数字电子技术基础教程》习题与参考答案(2010.1)第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101 解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

数字电子技术基础习题及答案

数字电子技术基础习题及答案..(总33页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--数字电子技术基础试题一、填空题 : (每空1分,共10分)1. 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

2图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>Ω)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC34.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2 A、并行A/D转换器 B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

4图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

《数字电子技术基础》课后习题及参考答案

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)=177(2)=170(3)=241(4)=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=()2(3)(B1)16=(1011 0001)2(4)(AF)16=()2【题1-5】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)()2=(2)()2=(3)()2=【题1-6】将下列十进制数转换为二进制数。

(1);(2);(3);(4)解:(1)=()2(2)=()2(3)=()2(4)=()2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

(1)01101100;(2);(3);(4)解:(1)01101100是正数,所以其反码、补码与原码相同,为01101100(2)反码为,补码为(3)反码为,补码为(4)反码为,补码为【题1-8】将下列自然二进制码转换成格雷码。

000;001;010;011;100;101;110;111解:格雷码:000、001、011、010、110、111、101、100【题1-9】将下列十进制数转换成BCD码。

数字电子技术基础. 第四版. 课后习题答案详解

(1)Y=A+B

(2)YABCABC

解:BCABCCABC(A+A=)

(5)Y=0

(2)(1101101)2=(6D)16=(109)10

(4)(11.001)2=(3.2)16=(3.125)10

(2)(127)10=(1111111)2=(7F)16

(4) (25.7)10(11001.1011 0011)2(19.B3)16

1.12

将下列各函数式化为最大项之积的形式

(1)Y(ABC)(ABC)(ABC)

(3)YM0⋅M3⋅M4⋅M6⋅M7

(5)YM0⋅M3⋅M5

(2)Y(ABC)(ABC)(ABC)

(4)YM0⋅M4⋅M6⋅M9⋅M12⋅M13

1.13

用卡诺图化简法将下列函数化为最简与或形式:

(3)Y(AB)(AC)ACBC

(2)Y

ACD

解:(AB)(AC)ACBC[(AB)(AC)AC]⋅BC

(ABACBCAC)(BC)BC

(5)YADACBCDC

解:Y(AD)(AC)(BCD)CAC(AD)(BCD)

ACD(BCD)ABCD

(4)YABC

(6)Y0

1.11

将函数化简为最小项之和的形式

(3)Y=1

(4)YAB CDABDAC D

解:YAD(B CBC)AD(BCC)AD

(7)Y=A+CD

(6)YAC(C DA B)BC(BADCE)

解:YBC(B⋅ADCE)BC(BAD)⋅CEABCD(CE)ABCDE

(8)YA(BC)(ABC)(ABC)

解:YA(B⋅C)(ABC)(ABC)A(AB CB C)(ABC)

数字电子技术基础习题答案(精编文档).doc

【最新整理,下载后即可编辑】数字电子技术基础答案第1章自测题 1.1填空题1. 100011.11 00110101.01110101 11110.01 1E.42. 43. n 24. 逻辑代数 卡诺图5.)(D C B A F )(D C B A F +='6.))((C B D C B A F7. 代数法 卡诺图8. 1 1.2判断题1. √2.√3. × 1.3选择题 1.B 2.C 3.C1.4 A F =1⊙B AB F 2 B A F +=3 1.51.6 C L =1.7 AB C B A BC Y 习题1.1 当000012 A A A ,7A 到3A 有1个不为0时,就可以被十进制8整除 1.2 (a)AC BC AB F ++=1 (b )B A AB F +=2(c)C B A S ⊕⊕= AC BC AB C 0 1.3略 1.4 (1))(B A D C F )(1))((1B A D C F ++=' (2))(B A B A F )(2))((2B A B A F ++='(3) E D C B A F 3 DE C AB F ='3 (4))()(4D A B A C E A F )())()((4D A C AB E A F +++='1.5 C B A F ⊕⊕=1.6 (1) B A C B C A L (2) D B C B D C A L (3) AD L (4) E ABCD L (5) 0 L 1.7 C B A BC A C AB ABC C B A L ),,(1.8(1) ABD D A C F 1 (2) BC AB AC F 2(3) C A B A B A F 3 (有多个答案) (4) C B D C AB C A CD F +++=4 (5) C B A ABD C B A D B A F 5 (6) 16 F 1.9 (1) AD D C B B A F 1 (2) B A AC F 2(3) D A D B C B F 3 (4) B C F 4 1.10 (1) C A B F 1 (2) B C F 2(3) D A B C F 3 (4) C B A D B D C F 4 1.11 C A B A D F1.12 (1) D B A D C A D C B F 1(多种答案) (2)C B BCD D C D B F 2(3) C B C A D C F 3 (4) A B F 4 (5) BD D B F 5(6) C B D A D C A F 6(多种答案) (7) C A D B F 7(多种答案)(8) BC D B F 8(多种答案) (9) B D C F 9 1.13 略第2章自测题 2.1 判断题1. √2. √3. ×4. √5. √6. √7. ×8. √9. × 10√ 2.2 选择题1.A B 2.C D 3.A 4.B 5.B 6.A B D 7.C 8.A C D 9.A C D 10.B 习题2.1解:ABC Y =1 2.2解:(a)mA234.0503.012=-=-=C CES CC BS R U V I βBS mA 1.0537.06I I B <=-=∴三极管处于放大状态,)V (711.05012=⨯⨯-=-=CB CC O R I V u β。

数字电子技术基础(第4版)_课后习题答案

第一章1.1二进制到十六进制、十进制(1)(10010111)2=(97)16=(151)10 (2)(1101101)2=(6D)16=(109)10(3)(0.01011111)2=(0.5F)16=(0.37109375)10 (4)(11.001)2=(3.2)16=(3.125)10 1.2十进制到二进制、十六进制(1)(17)10=(10001)2=(11)16 (2)(127)10=(1111111)2=(7F)161621016210)3.19()1010 1(11001.101(25.7)(4))A D7030.6()0101 0000 0111 1101 0110 (0.0110(0.39)(3) B ====1.8用公式化简逻辑函数(1)Y=A+B (3)Y=1)=+(解:1A A 1)2(=+++=+++=+++=C B A C C B A C B Y CB AC B A Y ADC C B AD C B C B AD DC A ABD CD B A Y =++=++=++=)()(Y )4(解:(5)Y=0 (7)Y=A+CDE ABCD E C ABCD CE AD B BC CE AD B BC Y CE AD B BC B A D C AC Y =+=⋅+=+⋅=++++=)()()()()()6(解:CB AC B C B A A C B A C B A C B A C B C B A A C B A C B A C B A Y C B A C B A C B A Y +=++=+++=++++=++++⋅+=++++++=)())(())()(())()((8解:)(D A D A C B Y ++=)9(E BD E D BF E A AD AC Y ++++=)10(1.9 (a) C B C B A Y += (b) C B A ABC Y +=(c) ACD D C A D C A B A Y D AC B A Y +++=+=21,(d) C B A ABC C B A C B A Y BC AC AB Y +++=++=21, 1.10 求下列函数的反函数并化简为最简与或式(1)C B C A Y += (2)DC A Y++=CB C B AC C B AC B A BC AC C A B A BC AC C A B A Y BCAC C A B A Y +=++++=⋅+++=+++=+++=))((]))([())(())(()3(解: (4)C B A Y ++=DC ABD C B D C A D C B D A C A C D C B C A D A Y CD C B C A D A Y =++=+++=++++=+++=)())(())()(()5(解: (6)0=Y1.11 将函数化简为最小项之和的形式CB AC B A ABC BC A C B A C B A C B A ABC BC A CB A AC B B A BC A C B AC BC A Y CB AC BC A Y +++=++++=++++=++=++=)()()1(解:D C B A CD B A D C B A ABCD BCD A D C B A Y +++++=)(2)13()()()(3CD B A BCD A D BC A D C B A D C B A ABCD D ABC D C AB D C AB CD B A D C B A D C B A D C B A CD AB B A B A B A ACD D AC D C A D C A CD A D C A D C A D C A B BCD D BC D C B D C B CD B D C B D C B D C B A Y CDB A Y ++++++++++++=+++++++++++++++++++=++=解:)((4)CD B A D ABC D BC A D C AB D C AB CD B A ABCD BCD A Y +++++++= (5)MN L N M L N LM N M L N M L N M L Y +++++=1.12 将下列各函数式化为最大项之积的形式(1)))()((C B A C B A C B A Y ++++++= (2)))()((C B A C B A C B A Y ++++++= (3)76430M M M M M Y ⋅⋅⋅⋅= (4)13129640M M M M M M Y ⋅⋅⋅⋅⋅= (5)530M M M Y ⋅⋅=1.13 用卡诺图化简法将下列函数化为最简与或形式:(1)D A Y +=(3)1=Y (2)D C BC C A B A Y +++= (4)B AC B A Y ++=B A DC Y ++=AC B A Y +=(5)D C B Y ++= (6)C B AC B A Y ++=(7)C Y = (9)D C A C B D A D B Y +++=(8))14,11,10,9,8,6,4,3,2,1,0(),,,(m D C B A Y ∑= (10)),,(),,(741m m m C B A Y ∑=D A D C B Y ++=ABC C B A C B A Y ++=1.14化简下列逻辑函数(1)D C B A Y +++= (2)D C A D C Y += (3)C A D AB Y ++= (4)D B C B Y += (5)E D C A D A E BD CE E D B A Y +++++=1.20将下列函数化为最简与或式(1)AD D C B D C A Y ++= (2)AC D A B Y ++= (3)C B A Y ++= (4)D B A Y +=第二章2.1解:Vv v V V v T I mA I mA Vv T V v a o B o B BS B o B 10T 3.0~0(2.017.0230103.0207.101.57.05I V 5v 1021.5201.510V 0v )(i i ≈≈∴<=×≈=−≈∴−=×+−=截止,负值,悬空时,都行)饱和-=时,=当截止时,=当都行)=饱和,,-=悬空时,都行)饱和。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第7章 时序逻辑电路【7-1】已知时序逻辑电路如图所示,假设触发器的初始状态均为0。

(1 )写出电路的状态方程和输出方程。

(2) 分别列出X =0和X =1两种情况下的状态转换表,说明其逻辑功能。

(3) 画出X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形。

1J 1KC11J 1KC1Q 1Q 2CPXZ1图解:1.电路的状态方程和输出方程n 1n2n 11n 1Q Q Q X Q +=+n 2n 11n 2Q Q Q ⊕=+ CP Q Q Z 21=2.分别列出X =0和X =1两种情况下的状态转换表,见题表所示。

逻辑功能为 当X =0时,为2位二进制减法计数器;当X =1时,为3进制减法计数器。

3.X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形如图(b)所示。

题表Q Q Z图(b)【7-2】电路如图所示,假设初始状态Q a Q b Q c =000。

(1) 写出驱动方程、列出状态转换表、画出完整的状态转换图。

(2) 试分析该电路构成的是几进制的计数器。

Q c图解:1.写出驱动方程1a a ==K J ncn a b b Q Q K J ⋅== n b n a c Q Q J = n a c Q K = 2.写出状态方程n a 1n a Q Q =+ n a n a n a n a n c n a 1n b Q Q Q QQ Q Q +=+ nc n a n c n b n a 1n b Q Q Q Q Q Q +=+3.列出状态转换表见题表,状态转换图如图(b)所示。

图7.2(b)表7.2状态转换表CP na nbc Q Q Q 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 16 0 0 0n4.由FF a 、FF b 和FF c 构成的是六进制的计数器。

【7-3】在二进制异步计数器中,请将正确的进位端或借位端(Q 或Q )填入下表解:题表7-3下降沿触发 由 Q 端引出进位 由Q 端引出借位触发方式 加法计数器 减法计数器上升沿触发 由Q 端引出进位 由Q 端引出借位【7-4】电路如图(a)所示,假设初始状态Q 2Q 1Q 0=000。

1. 试分析由FF 1和FF 0构成的是几进制计数器;2. 说明整个电路为几进制计数器。

列出状态转换表,画出完整的状态转换图和CP 作用下的波形图。

1J 1KC11J 1KC11J 1KC1CPFF1FF2FF0CPQ 0Q 2Q 1(a) (b)图解:1、由FF 1和FF 0构成的是三进制加法计数器(过程从略)2、整个电路为六进制计数器。

状态转换表(略),完整的状态转换图 和CP 作用下的波形图如下图。

CP Q0Q1Q2【7-5】某移位寄存器型计数器的状态转换表如表所示。

请在图中完成该计数器的逻辑图,可以增加必要的门电路。

要求:写出求解步骤、画出完整的状态转换图。

(Q 3为高位) 表图解:(1) 根据状态转换表画次态卡诺图,求出状态方程。

000111100100011000000000111100´´´´´´´´11100111´´´´´´´´´´´´´´´´´´´´´´´´´´´´n 1Q n 0Q n 3Q n 2Q n+13Q n+12Q 1Q 0Q n+1n+1n+1n n 310Q Q Q =; n+1n 23Q Q =; n+1n 12Q Q =; n+1n11Q Q =(2) 由状态方程写驱动方程。

n n 310D Q Q =; n 23D Q =; n 12D Q =; n 01D Q =(3) 验证自启动,画完整状态转换图。

电路可自启动。

(4)电路图如下图。

CP【7-6】在图(a)所示电路中,由D触发器构成的六位移位寄存器输出Q6Q5Q4Q3Q2Q1的初态为010100,触发器FF的初态为0,串行输入端D SR=0。

请在图 (b)中画出A、Q及B 的波形。

CPCP(a) (b)图解:波形图如图(b)所示。

CP A Q B图(b)【7-7】分析图所示电路,说明它们是多少进制计数器?1Q D 74LS161RCO Q C Q B Q A ET EP D C B A CR LDCPCP1Q D 74LS161RCO Q C Q B Q A ET EP D C B A CR LDCPCP111(a) (b)图解:图(a),状态转换顺序[Q D Q C Q B Q A ]=01234560,是7进制计数器;图(b),[Q D Q C Q B Q A ]=67891011121314156,是10进制计数器;【7-8】分析图所示电路的工作过程1. 画出对应CP 的输出Q a Q d Q c Q b 的波形和状态转换图(采用二进制码的形式、 Q a 为高位)。

2. 按Q a Q d Q c Q b 顺序电路给出的是什么编码?3. 按Q d Q c Q b Q a 顺序电路给出的编码又是什么样的?PC图 解:1 状态转换图为2按Q a Q d Q c Q b 顺序电路给出的是5421码。

3. 按Q d Q c Q b Q a 顺序电路给出的编码如下0000→0010→0100→0110→1000→0001→0011→0101→0111→1001→0000【7-10】试用2片4位二进制计数器74LS160采用清零法和置数法分别实现31进制加法计数器。

解:答案略。

【7-9】图为由集成异步计数器74LS90、74LS93构成的电路,试分别说明它 们是多少进制的计数器。

Q Q C Q DQ A B 74LS93CP ACP B PC R 0(1)R 0(2)Q Q C Q DQ A B 74LS90CP A CP BPC R 0(1)R 0(2)S 0(1)S 0(2)(a) (b)Q D Q C Q B Q A CP BCP AR 0(1)R 0(2)74LS93CPQ D Q C Q B Q A CP BCP AR 0(1)R 0(2)74LS93(c)图解:图(a),状态转换顺序[Q D Q C Q B ]=0120,是3进制计数器; 图(b),状态转换顺序[Q D Q C Q B ]=01230,是4进制计数器;图(c),是37进制计数器。

【7-11】图所示为一个可变进制计数器。

其中74LS138为3线/8线译码器,当S 1=1且032==S S 时,进行译码操作,即当A 2A 1A 0从000到111变化时,71~Y Y 依次被选中而输出低电平。

74LS153为四选一数据选择器。

试问当MN 为各种不同取值时,可组成几种不同进制的计数器?简述理由。

Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 7E 3E 2E 1B 0B 1B 2D 0D 1D 2D 3A 0A 1SL 74LS13874LS1531J 1K C11J 1K C11J 1K C11J 1K C1CP1Q 1Q 2Q 3Q 4RRRR图解:4个JK 触发器构成二进制加法计数器,当计数到 [Q 4Q 3Q 2Q 1]=10000时,74LS138满足使能条件,对[Q3Q2Q1]的状态进行译码,译码器的输出Y经过4选1数据选择器74LS153,在[MN]的控制下,被选中的Y信号,以低电平的形式对计数器清零。

不同的[MN]即可改变图所示电路的计数进制,具体见下表。

第8章存储器【8-1】填空1.按构成材料的不同,存储器可分为磁芯和半导体存储器两种。

磁芯存储器利用来存储数据;而半导体存储器利用来存储数据。

两者相比,前者一般容量较;而后者具有速度的特点。

2.半导体存储器按功能分有和两种。

3.ROM主要由和两部分组成。

按照工作方式的不同进行分类,ROM可分为、和三种。

4.某EPROM有8条数据线,13条地址线,则存储容量为。

5.DRAM 速度 SRAM,集成度 SRAM。

6.DRAM是 RAM,工作时(需要,不需要)刷新电路;SRAM是 RAM,工作时(需要,不需要)刷新电路。

7. FIFO的中文含义是。

解:1.正负剩磁,器件的开关状态,大,快。

2.ROM ,RAM 。

3.地址译码器,存储矩阵,固定内容的ROM 、 PROM ,EPROM 三种。

4.213×8。

5.低于,高于。

6.动态,需要;静态,不需要。

7.先进先出数据存储器。

【8-2】图是16×4位ROM ,A 3A 2A 1A 0为地址输入,D 3D 2D 1D 0为数据输出,试分别写出D 3、D 2、D 1和D 0的逻辑表达式。

AA A A 2 1图解:⎪⎪⎪⎩⎪⎪⎪⎨⎧∑=⋅=∑==)m(0,5,9,13312,15)m(3,6,9,12100D A A D D A D【8-3】用16×4位ROM 做成两个两位二进制数相乘(A 1A 0×B 1B 0)的运算器,列出真值表,画出存储矩阵的阵列图。

解:图【8-4】由一个三位二进制加法计数器和一个ROM 构成的电路如图(a)所示 1.写出输出F 1、F 2和F 3的表达式;2.画出CP 作用下F 1、F 2和F 3的波形(计数器的初态为”0“)·CPQ 2Q 1Q 0F 1 F F 3F 1F 2F 3计数器地址译码器CP(a) (b)图解:1. ⎪⎪⎩⎪⎪⎨⎧⋅=⋅⋅+⋅+⋅⋅=⋅+⋅+⋅=013012012012201212011Q Q F Q Q Q Q Q Q Q Q Q F Q Q Q Q Q Q Q F2.CPF1F2F3图(b)【8-5】用ROM实现全加器。

解:mm1m2m3m4m5m6m7图第9章可编程逻辑器件及Verilog语言【9-1】简述CPLD与FPGA的结构特点?解:CPLD采用了与或逻辑阵列加上输出逻辑单元的结构形式;而FPGA的电路结构由若干独立的可编程逻辑模块组成,用户可以通过编程将这些模块连接成所需要的数字系统。

CPLD属于粗粒结构,FPGA属于细粒结构。

CPLD是基于乘积项的可编程结构,而在FPGA中,其基本逻辑单元LE是由可编程的查找表(LUT,Look-Up Table)构成的, LUT本质上就是一个RAM。

【9-2】简述手工设计与PLD设计的流程?解:答:手工设计:第一步,设计电路,画出逻辑图;第二步,选择逻辑元器件。