数字逻辑模拟试卷3答案

《数字逻辑》自测题答案

A B

,当X=1时,它的功能

。

X Y(t ) 0 A B/0

1

1/ 1

1/ 0 1/ 1

0/1

D

0/0

1/ 1

D/0 B C / 0 A /1 C D / 0 B /1 D A /1 C /1

Y(t 1) / Z(t )

X 0 Q1Q0 00 01/ 0

1

EN / CP D Q D锁存器 Q D触发器

16. 画出具有循环进位的余3码加1计数器的Moore型状态图。

其它/0

0011/0

0100/0

0101/0

0110/0

0111/0

1100/1

1011/0

1010/0

1001/0

1000/0

17. 由74LS138译码器及逻辑门构成的组合逻辑电路如下,其中输入信号A7~A0 为地址变量。试填写表格。

0

0 1

0000

0000 0110

0011

0100 1011

8421码 X3 X2 X1 X0

0

≥1 &

0 W

0

0100 0101

0110

0111 1000

1

1 1

0110

0110 0110

1100

1101 1110

X3 X2 X1 X2 X0

1001

结论:

1

0110

1111

将8421码转换为2421码

(1)F

3

(2)功能:三变量一致检测电路

x3 x2 x1 en d0 d1 d2 d3 d4 d5 d6 d7

(3)module same(A,B,C,F); input A,B,C; output F;

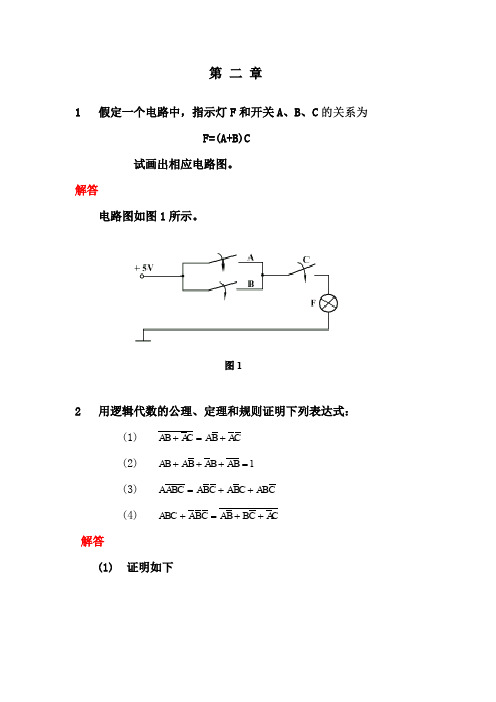

《数字逻辑》第3章习题答案

题

【3-1】填空: (1) 逻辑代数中有三种最基本运算: 与 、 或 和 非 ,在此基础上又派生出五种基本运算, 分别为 与非 、 或非 、 异或 、 同或 、和 与或非 。 (2) 与运算的法则可概述为:有 0 出 0 ,全 1 出 1 ;类似地,或运算的法则为 有”1”出”1”, 全”0”出”0” 。 (3) 摩根定理表示为: A B = A B ; A B = A B 。 (4) 函数表达式 Y= AB C D ,则其对偶式为 Y ' = ( A B)C D 。 积的形式结果应为 M ( 0,1,2,4,5,8,9,10)。 (5) 函数式 F=AB+BC+CD 写成最小项之和的形式结果应为 m ((3,6,7,11,12,13,14,15)), 写成最大项之

0 0 1 1 1 1

1 1 0 0 1 1

0 1 0 1 0 1

1 1 0 0 1 0

【3-8】写出下列函数的反函数 F ,并将其化成最简与或式。 (1) F1 ( A D )( B C D)( AB C ) (2) F2 ( A B )( BCD E )( B C E )(C A) (3) F3 A B C A D (4) F4 ( A B)C ( B C ) D 解: (1) F1 AD C (2) F2 AB A C E (3) F3 AB AC A D (4) F4 BC C D ABD A B C 【3-9】用对偶规则,写出下列函数的对偶式 F ,再将 F 化为最简与或式。 (1) F1 AB B C A C (2) F2 A B C D (3) F3 ( A C )( B C D)( A B D) ABC (4) F4 ( A B )( A C )( B C )(C D) (5) F5 AB C CD BD C 解:题中各函数对偶函数的最简与或式如下: (1) F1 A BC AB C (2) F2 A B D A C D (3) F3 AC A BD (4) F4 A BC B C CD (5) F5 ABC D (6) F6 AB C D 【3-10】已知逻辑函数 F A B C , G=A⊙B⊙C,试用代数法证明: F G 。 解:

数字逻辑模拟试卷3答案

0

1

0

0

1

1

0

1

0

0

0

1

1

1

1

1

0

1

0

0

0

0

0

1

1

0

0

1

0

1

1

1

0

1

0

1

0

1

1

0

1

1

1

1

1

1

1

0

0

0

0

1

1

1

0

1

0

1

1

1

1

1

0

1

0

1

1

1

1

1

1

1

1

精品

4.画出状态图如图 6 所示。 5.画出波形图如图 7 所示。

CP D Q1 Q2 Q3

6.说明逻辑功能。

.

图7

八、试用 4 位二进制计数器 74lLS161 接成 12 进制计数器,要求: 1. 分别采用反馈清零法实现,画出逻辑接线图(可适当添加门电路); 2. 画出状态转换图。(8 分) (74LS161 功能表如图所示)

清零 预置 使能 时钟

预置数据输入

输出

RD LD EP ET CP D0 D1 D2 D4 Q0 Q1 Q2 Q3

0

X XX X XXXX 0 0 0 0

1

0 XX

ABCDABC D

1

1 0 X X X XX X 保

持

1

1 X 0 X X X X X保

持

1

1 11

X X X X计

数

精品

数字逻辑模拟试卷附答案

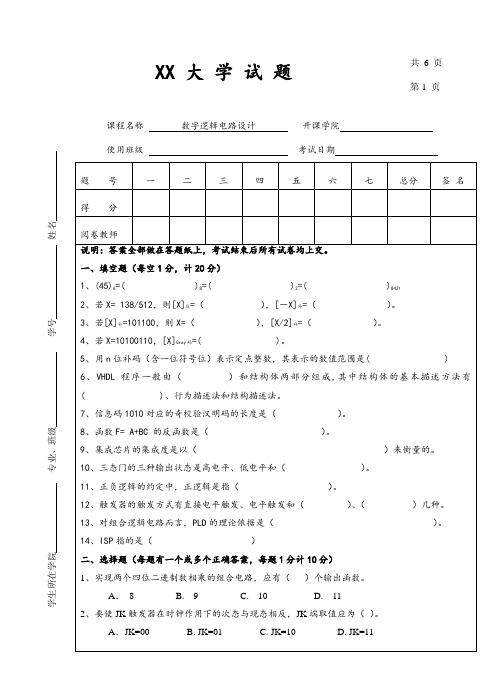

XX 大 学 试 题课程名称 数字逻辑电路设计 开课学院使用班级 考试日期苏 大 学 试题 第3 页苏大 学 试题第4 页四、根据下图波形写出其逻辑关系表达式Z=F(A,B,C) (10分)A B C Z五、分析题:某同步时序逻辑电路如图所示。

(12分)(1) 写出该电路激励函数和输出函数; (2) 画出输出矩阵和激励矩阵; (3) 画出状态表和状态图;(4)设各触发器的初态均为0,试画出下图中Q1、Q2和Z 的输出波形。

数字逻辑模拟试卷2答案一、填空题(每空1分,计20分) 1、(45)6=(35)8=(11101)2=(00101001)84212、若X= 138/512,则[X]反=(0.01000101),[-X]补=(1.10111011)。

3、若[X]补=101100,则X=(-100100),[X/2]补=(110110)。

4、若X=10100110,[X]Gray 码=(11110101)。

5、用n 位补码(含一位符号位)表示定点整数,其表示的数值范围是(-2n-1~2n-1-1)6、VHDL 程序一般由(实体)和结构体两部分组成,其中结构体的基本描述方法有(数据流描述法)、行为描述法和结构描述法。

7、信息码1010对应的奇校验汉明码的长度是(7位)。

8、函数F= A+BC 的反函数是()(C B A )。

9、集成芯片的集成度是以(等效门电路的数量)来衡量的。

10、三态门的三种输出状态是高电平、低电平和(高阻状态)。

11、正负逻辑的约定中,正逻辑是指(高电平表示1;低电平表示0)。

12、触发器的触发方式有直接电平触发、电平触发和(脉冲触发)、(边沿触发)几种。

13、对组合逻辑电路而言,PLD 的理论依据是(任何组合逻辑函数都可以用与-或式表示)。

14、ISP 指的是(在系统可编程技术)二、选择题(每题有一个或多个正确答案,每题1分计10分)1、A2、D3、B ,C4、A ,D5、A ,B ,D6、A ,B ,C7、A ,B ,C8、B9、B ,D 10、C 三、按要求化简下列函数(14分)1.用代数法求函数 F = A B + A B C + B C 的最简“与-或”表达式。

数字逻辑考题及答案

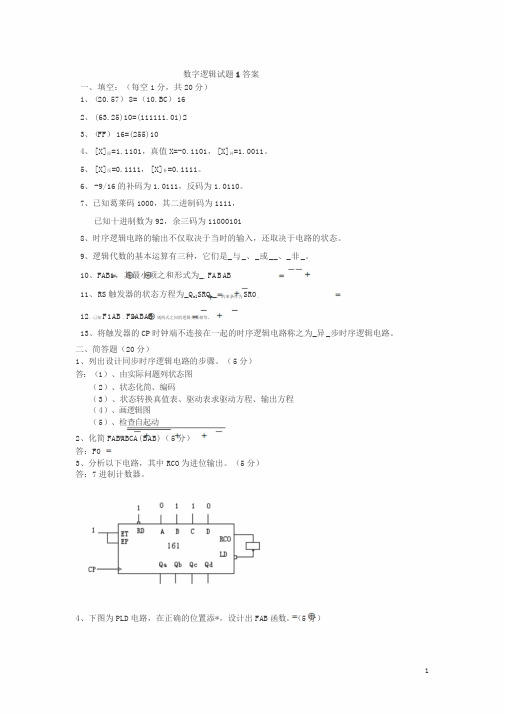

数字逻辑试题1答案一、填空:(每空1分,共20分)1、(20.57)8=(10.BC)162、(63.25)10=(111111.01)23、(FF)16=(255)104、[X]原=1.1101,真值X=-0.1101,[X]补=1.0011。

5、[X]反=0.1111,[X]补=0.1111。

6、-9/16的补码为1.0111,反码为1.0110。

7、已知葛莱码1000,其二进制码为1111,已知十进制数为92,余三码为110001018、时序逻辑电路的输出不仅取决于当时的输入,还取决于电路的状态。

9、逻辑代数的基本运算有三种,它们是_与_、_或__、_非_。

10、FAB1,其最小项之和形式为_。

FA B AB11、RS触发器的状态方程为_Q n1SRQ n_,约束条件为SR0。

12、已知F1AB、F2ABAB,则两式之间的逻辑关系相等。

13、将触发器的CP时钟端不连接在一起的时序逻辑电路称之为_异_步时序逻辑电路。

二、简答题(20分)1、列出设计同步时序逻辑电路的步骤。

(5分)答:(1)、由实际问题列状态图(2)、状态化简、编码(3)、状态转换真值表、驱动表求驱动方程、输出方程(4)、画逻辑图(5)、检查自起动2、化简FABABCA(BAB)(5分)答:F03、分析以下电路,其中RCO为进位输出。

(5分)答:7进制计数器。

4、下图为PLD电路,在正确的位置添*,设计出FAB函数。

(5分)15分注:答案之一。

三、分析题(30分)1、分析以下电路,说明电路功能。

(10分)解:XY m(3,5,6,7)m(1,2,4,7)2分ABCiXY0000000101010010111010001101101101011111该组合逻辑电路是全加器。

以上8分2、分析以下电路,其中X为控制端,说明电路功能。

(10分)解:FXA B C XABCXABCXABCXABCXABC4分FX(ABC)X(A B C ABC)4分所以:X=0完成判奇功能。

数字逻辑第3章答案

F, A B[(C D)E G]

5 (1) 如果已知 X + Y 和 X + Z 的逻辑值相同,那么 Y 和 Z 的逻

辑值一定相同。正确吗?为什么? (2) 如果已知 XY 和 XZ 的逻辑值相同,那么那么 Y 和 Z 的逻辑值

一定相同。正确吗?为什么? (3)如果已知 X + Y 和 X + Z 的逻辑值相同,且 XY 和 XZ 的逻辑

(1) F(A, B,C, D) BD AD CD CD ACD ABD

(2) F(A, B,C, D) (AB AB) C (AB AB) C

解答

G(A, B,C, D) AB BC AC (A B C) ABC

(1) 当 b a 时,令 a=1,b=0 能得到最简“与-或”表达式: F BC CD ACD (3 项)

(2) 当 a=1,b=1 时,能得到最简的“与-或”表达式:

F BC CD AC (3 项)

11 用列表法化简逻辑函数

F(A, B,C, D) m(0,2,3,5,7,8,10,11,13,15)

10

0

0

01 0 0 1 1

1

1

10 0 0 1 1

1

1

11 0 1 0 1

0

0

4 求下列函数的反函数和对偶函数: (1) F AB AB

(2) F A B A C C DE E

(3) F (A B)(C DAC)

(4) F A B CD E G

值相同,那么 Y = Z。正确吗?为什么? (4) 如果已知 X+Y 和 X·Y 的逻辑值相同,那么 X 和 Y 的逻辑值

数字逻辑课程三套作业及答案

数字逻辑课程三套作业及答案一、单选题。

1.(4分)如图某1-229(D)A.(A)B.(B)C.(C)D.(D)知识点:第五章解析第五章译码器2.(4分)如图某1-82(C)A.(A)B.(B)C.(C)D.(D)知识点:第二章解析第二章其他复合逻辑运算及描述3.(4分)N个触发器可以构成最大计数长度(进制数)为(D)的计数器。

A.NB.2NC.N2次方D.2N次方知识点:第九章解析第九章计数器4.(4分)n个触发器构成的扭环型计数器中,无效状态有(D)个。

A.A.nB.B.2nC.C.2n-1D.D.2n-2n知识点:第九章解析第九章集成计数器5.(4分)如图某1-293(A)A.(A)B.(B)C.(C)D.(D)知识点:第十一章解析第十一章数字系统概述6.(4分)如图某1-317A.(A)B.(B)C.(C)D.(D)知识点:第二章解析第二章其他复合逻辑运算及描述7.(4分)EPROM是指(C)A.A、随机读写存储器(D)B.B、只读存储器C.C、光可擦除电可编程只读存储器D.D、电可擦可编程只读存储器知识点:第十章解析第十章只读存储器8.(4分)如图某1-407(B)A.(A)B.(B)C.(C)D.(D)知识点:第十一章解析第十一章数字系统概述9.(4分)为实现将JK触发器转换为D触发器,应使(A)A.J=D,K=D非B.B.K=D,J=D非C.C.J=K=DD.D.J=K=D非知识点:第六章解析第六章各种触发器的比较10.(4分)一位8421BCD码计数器至少需要(B)个触发器。

A.3B.B.4C.C.5D.D.10知识点:第九章解析第九章计数器11.(4分)为把50Hz的正弦波变成周期性矩形波,应当选用(A)A.A、施密特触发器B.B、单稳态电路C.C、多谐振荡器D.D、译码器知识点:第六章解析第六章集成触发器12.(4分)下列描述不正确的是(A)A.a.D触发器具有两个有效状态,当Q=0时触发器处于0态B.b.移位寄存器除具有数据寄存功能外还可构成计数器。

数字逻辑试题及答案

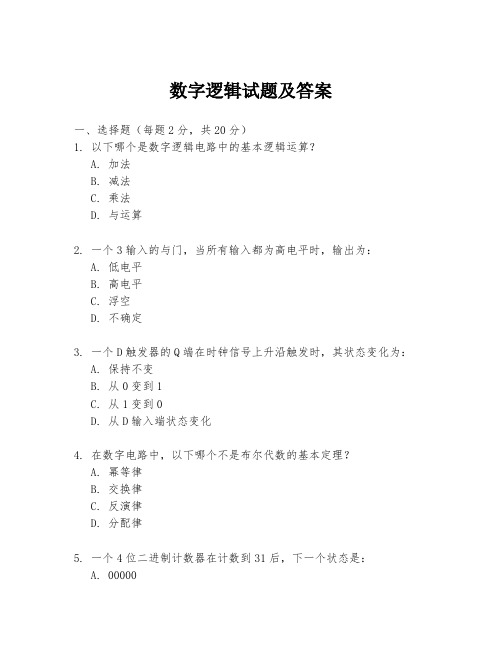

数字逻辑试题及答案一、选择题(每题2分,共20分)1. 以下哪个是数字逻辑电路中的基本逻辑运算?A. 加法B. 减法C. 乘法D. 与运算2. 一个3输入的与门,当所有输入都为高电平时,输出为:A. 低电平B. 高电平C. 浮空D. 不确定3. 一个D触发器的Q端在时钟信号上升沿触发时,其状态变化为:A. 保持不变B. 从0变到1C. 从1变到0D. 从D输入端状态变化4. 在数字电路中,以下哪个不是布尔代数的基本定理?A. 幂等律B. 交换律C. 反演律D. 分配律5. 一个4位二进制计数器在计数到31后,下一个状态是:A. 00000B. 00001C. 11111D. 不能确定6. 以下哪个不是数字逻辑电路设计中的优化方法?A. 布尔代数简化B. 逻辑门替换C. 增加冗余D. 逻辑划分7. 一个异或门的真值表中,当输入相同,输出为:A. 0B. 1C. 无法确定D. 无输出8. 在数字电路中,同步计数器与异步计数器的主要区别在于:A. 计数范围B. 计数速度C. 电路复杂度D. 计数精度9. 以下哪个不是数字逻辑电路中的存储元件?A. 触发器B. 寄存器C. 计数器D. 逻辑门10. 一个简单的数字逻辑电路设计中,如果需要实现一个2输入的或门,至少需要几个与门?A. 1B. 2C. 3D. 4答案:1. D2. B3. D4. C5. B6. C7. A8. B9. D10. A二、填空题(每空2分,共20分)1. 数字逻辑电路中最基本的逻辑运算包括______、或运算、非运算。

2. 一个2输入的与门,当输入都为高电平时,输出为______。

3. 布尔代数的基本定理包括______、结合律、分配律等。

4. 一个D触发器的Q端在时钟信号上升沿触发时,Q端状态与______相同。

5. 4位二进制计数器的计数范围是从______到1111。

6. 数字逻辑电路设计中的优化方法包括布尔代数简化、逻辑门替换、______等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

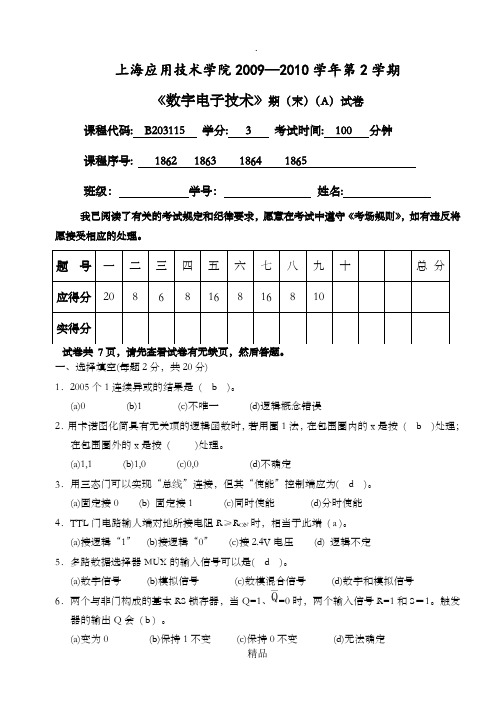

题号一 二 三 四 五 六 七 八 九 十

总分

应得分 20 8 6 8 16 8 16 8 10

实得分

试卷共 7 页,请先查看试卷有无缺页,然后答题。 一、选择填空(每题 2 分,共 20 分)

1.2005 个 1 连续异或的结果是 ( b )。

(a)0

(b)1

(c)不唯一

(d)逻辑概念错误

2.用卡诺图化简具有无关项的逻辑函数时,若用圈 1 法,在包围圈内的 x 是按 ( b )处理;

在包围圈外的 x 是按 ( )处理。

(a)1,1

(b)1,0

(c)0,0

(d)不确定

3.用三态门可以实现“总线”连接,但其“使能”控制端应为( d )。

(a)固定接 0 (b) 固定接 1

(c)同时使能

(d)分时使能

4.TTL 门电路输人端对地所接电阻 R≥RON 时,相当于此端 ( a )。 (a)接逻辑“1” (b)接逻辑“0” (c)接 2.4V 电压 (d) 逻辑不定

0

0

1

1

0

1

0

1

1

0

1

1

1

0

0

1

1

精品

.

1

1

1

0

0

1

由真值表写出其逻辑表达式

四、分析下图组合电路(要求写出输出表达式,列出真值表,说明其功能)(8 分)

&

I0

1

I1

1

&

I2

1

&

I3

1

&

解:首先写出其输出表达式

≥ Y1 1

≥ Y0 1

然后列出真值表如下

0

0

1

0

0

1

0

1

0

0

1

0

1

0

0

0

1

1

功能是:编码器

b) 画状态表和状态转换图。

c) 画出输出端 Q1、Q2、Q3 的波形。

d) 说明电路的逻辑功能。(16 分)

Q1

Q2

Q3

D

J

J

J

C

C

C

1

K

K

K

CP

CP

精品

D

Q1

.

解: 1.写出驱动方程

2.写出状态方程

3.列出状态表 D

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

1

0

1

0

0

0

0

1

1

1

1

0

0

1

0

0

0

0

0

0

1

0

1

.

上海应用技术学院 2009—2010 学年第 2 学期

《数字电子技术》期(末)(A)试卷

课程代码: B203115 学分: 3 考试时间: 100 分钟

课程序号: 1862 1863 1864 1865

班级:

学号:

姓名:

我已阅读了有关的考试规定和纪律要求,愿意在考试中遵守《考场规则》,如有违反将 愿接受相应的处理。

五、设三台用电设备(A、B、C)耗电功率分别为 10、20、30KW,这三台设备的投入是随

机的组合,而自备电源的容量为 35KW。试设计电源过载保护逻辑电路,当过载时输出 L 为

1,不过载时输出 L 为 0。 要求:

1.列出真值表;

2.写出最简逻辑表达式;

3.画出用与非门构成的逻辑电路图。

4. 画出用八选一数据选择器 74LS151 构成的逻辑电路图并写出相应输出表达式。(16 分)

(2)画出 Q,1 , 2 的波形。(8 分)

精品

.

cp

解:写出 JK 触发器的特性方程

由于 JK 均取 1,此时 JK 触发器处于翻转状态。 同时输出Φ1 和Φ2 的表达式如下

由此画出其波形图如图 5 所示。

CP Q

Q Φ1 Φ2

图5

七、图示电路中,已知 CP、D 的波形,设初态为 0,

a) 写出驱动方程、状态方程和输出方程;

5.多路数据选择器 MUX 的输入信号可以是( d )。

(a)数字信号 (b)模拟信号

(c)数模混合信号 (d)数字和模拟信号

6.两个与非门构成的基本 RS 锁存器,当 Q=1、 =0 时,两个输入信号 R=1 和 S=1。触发

器的输出 Q 会 ( b ) 。

(a)变为 0

(b)保持 1 不变

(c)保持 0 不变 精品

1

0

0

1

1

11Leabharlann 2.写出逻辑表达式并化简3.用与非门来实现如图 3 所示。

精品

.

A B C

&

&

&

图3

4.用数据选择器 74LS151 来实现如图 4 所示。

E

D7 D6 D5 D4

D3

1

D2

D1

D0

0

A

S2

B

S1

C

S0

74LS151

Y

L

图4

六、双相时钟发生器如下图所示,

(1)写出 JK 触发器的特性方程;

74LS151 功能表:

74LS151 逻辑图:

精品

.

输入

输出

G

CB A

YW

1

01

0

00 0

D0

D0

0

001

D1

D1

0

01 0

D2

D2

0

01 1

D3

D3

0

10 0

D4

D4

0

101

D5

D5

0

11 0

D6

D6

0

1 11

D7

D7

解:

1.列出真值表

A

B

C

L

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

1

1

(b)单稳态触发器

(c)多谐振荡器

(d)集成定时器

10.把模拟量转换成为相应数字量的转换器件称为( d )。

(a)数—模转换器 (b)DAC (c)D/A 转换器 (d)ADC

二、用卡诺图法化简函数(8 分) (1) 解:本题的卡诺图如图 1 所示:

C

0 11 0

011 0 B

0 111 A

0 111

其化简结果为:

D 图1

精品

.

(2) 解:本题的卡诺图如图 2 所示:

C

其化简结果为:

1 1 ××

1 ××1

B

0 1 ×0

A

0 1 ××

D 图2

三、.写出图示逻辑电路出端的逻辑表达式。(6 分)

+VC

A

&

B

C

&

&

F1

解:首先写出其真值表如下表

A

B

C

L

0

0

0

1

1

0

0

0

1

1

0

1

0

1

0

1

1

0

0

1

1

1

0

1

1

清零 预置 使能 时钟

预置数据输入

输出

RD LD EP ET CP D0 D1 D2 D4 Q0 Q1 Q2 Q3

0

X XX X XXXX 0 0 0 0

1

0 XX

ABCDABC D

1

1 0 X X X XX X 保

持

1

1 X 0 X X X X X保

持

1

1 11

X X X X计

(d)无法确定

. 7.某触发器的状态是在 CP 的下降沿发生变化,它的电路符号应为( b )。

(a)

(b)

(c)

(d)

8.欲把串行数据转换成并行数据,可用( c )。

(a)计数器

(b)分频器

(c)移位寄存器

(d)脉冲发生器

9.数字系统中,常用( a )电路,将输入缓变信号变为矩形脉冲信号。

(a)施密特触发器

0

1

0

0

1

1

0

1

0

0

0

1

1

1

1

1

0

1

0

0

0

0

0

1

1

0

0

1

0

1

1

1

0

1

0

1

0

1

1

0

1

1

1

1

1

1

1

0

0

0

0

1

1

1

0

1

0

1

1

1

1

1

0

1

0

1

1

1

1

1

1

1

1

精品

4.画出状态图如图 6 所示。 5.画出波形图如图 7 所示。

CP D Q1 Q2 Q3

6.说明逻辑功能。

.

图7

八、试用 4 位二进制计数器 74lLS161 接成 12 进制计数器,要求: 1. 分别采用反馈清零法实现,画出逻辑接线图(可适当添加门电路); 2. 画出状态转换图。(8 分) (74LS161 功能表如图所示)