基于fpga的adc采样控制电路设计

用CPLD/FPGA设计A/D采样控制器

7

.

1 引 言

CP F GA ( 杂 可 编 程 逻 辑 器 件 / 场 可 编 I D/ P 复 现

0 l

C CK LO I ' Nl l

E_ 0 G0 1

E I6 0 AD G 『 1 DA ^m A

E 【 0 G 2 J 7

^ I E

程 门 阵 列 ) 数 字 系 统 的 设 计带 来 了极 大 的灵 活 性 , 为 兼有串、 行工作方式 和高集成度、 并 高速 、 可靠 性 高 等 明 显 的 特 点 , 超 高 速 领 域 和实 时 测 控 方 面有 非 在 常 广 泛 的应 用 。 VHDl 言 主 要 用 于 描 述 数 字 系统 的 结 构 、 语 行 为 、 能 和 接 口, 其 他 的硬 件 描 述 语 言 相 比, 功 与 VHDI 有 更 强 的 行 为 描 述 能 力 , 而 决 定 它 成 具 从 为 系 统 设 计 领 域最 佳 的硬 件 描 述 语 言 用 VHD1 设

件 , 而生 成硬 件 电路 。VHDI 是 一 种 仿真 语 言 , 从 还

结 束 标 志 , 电 平 转 为 高 电 平 时 转 换 结 束 ; TART 低 S 为转换启动信号 , 升沿有效j 上 OE 为 数 据 输 出 允 许 端 , 电 平 有 救 ;DO D7 为 A, 变 换 数 据 输 出 高 [ … 3 / D 端 其工 作 时 序 如 图 2所 示 。

言 进行 描 述 。

关 键词 : LD/ PGA, CP F 采样 控 制 器 , ADC 8 9 VHDL语 言 , 限 状 态 机 0 0. 有

[ sr c ] A s mp i g c n r l ri d sg e y u ig C F GA.Ac o d n O Ab ta t a l o to l s e i n d b sn PI n e D/ P c r i g t

基于 FPGA 的 AD 采样设计

2 系统 硬 件 整 体 设 计

AD采样 控 制 的核 心 部 分 采 用 Xi l i n x公 司 的

式, 分 析原 始 数 据 和 F P GA 输 出信 号 的 幅值 和 频

率特 性 。

的数 据采 集 系统 。在本 研究 中 , 多 通道 AD 7 6 5 6采 样芯 片 实现对 模拟 信号 的转换 , 该 芯 片最 高 采样 率

2 5 0 KHz ; F P GA提 供逻 辑控 制 , 虽 然 以传 统 的 D S P 或单 片 机作 为 C P U 的 AD采 样 系 统 控 制 简 单 , 但

Ab s t r a c t Al o n g wi t h t h e d e v e l o p me n t o f t h e c o mmu n i c a t i o n t e c h n o l o g y,Re a bt i me AD S a mp l i n g a n d t h e e f f e c t i v e p r o c e s s i n g p l a y a n i mp o r t a n t r o l e i n t h e d e s i g n o f d i g i t a l s i g n a l r e c e i v e r . A k i n d o f AD S a mp l i n g b a s e d o n F P GA i s p r o p o s e d , t h e d e s i g n o f t h e s y n c h r o n o u s s a mp l i n g c l o c k a n d F P GA c o n f i g u r a t i o n me t h o d f o r t h e AD7 6 5 6 i s p r o p o s e d,t h e s a mp l i n g d a t a a r e p r o c e s s e d b y s i n e c a r r i e r mo d u l a t i o n a n d l o w- p a s s f i l t e r i n g .F i n a l l y,t h e p r o c e s s e d d a t a a r e s h o wn i n t h e Ma t l a b .Th e e x — p e r i me n t r e s u l t s s h o w t h a t t h e d e s i g n i s s i mp l e a n d e f f e c t i v e ,h i g h l y v e r s a t i l e . K e y Wo r d s F P GA ,AD7 6 5 6 ,AD s a mp l i n g,M a t l a b s i mu l a t i o n Cl a s s Nu mb e r TP 3 3 6

基于FPGA的A_D转换采样控制模块的设计

技术创新PLDCPLDFPGA应用您的论文得到两院院士关注基于FPGA的A/D转换采样控制模块的设计ADesignoftheA/DConvertionSamplingControlModuleBasedonFPGA(内蒙古工业大学)户国强房建东郭春兰HUGuo-qiangFANGJian-dongGUOChun-lan摘要:本文采用FPGA器件EP1C6T144C8芯片代替单片机控制A/D转换芯片ADC0809进行采样控制,整个设计用VHDL语言描述,在QuartusⅡ平台下进行软件编程实现正确的A/D转换的工作时序控制过程,并将采样数据从二进制转化成BCD码。

本设计可用于高速应用领域和实时监控方面。

关键词:FPGA;A/D转换;VHDL;采样控制;BCD码中图分类号:TN911.75文献标识码:AAbstract:ByusingFPGAdeviceEP1C6T144C8asthecontrollerofA/DconverterAD0809inthispaperthattaketheplaceofMCU.ThewholedesignisdescribedintheVHDL.CarryingoutthesoftprogrammingundertheQuartusⅡplatformtorealizethecorrectsequencecontrollingprocessofA/DconverterandchangetheBinarynumberintotheBCDcode.Itcanbewidelyusedinhigh-speedapplicationfieldandthereal-timesupervisorycontrolaspect.Keywords:FPGA;A/Dconvertion;VHDL;samplingcontrol;BCDcode文章编号:1008-0570(2008)07-2-0229-02在以往的A/D器件采样控制设计中,多数是以单片机或CPU为控制核心,虽然编程简单,控制灵活,但缺点是控制周期长,速度慢。

基于FPGA的多路AD自动采集系统设计初稿

基于FPGA多路A/D自动采集采集系统设计摘要:在以往AD采集中,通过微控制器控制A/D芯片复杂的逻辑,不仅增加了微控制器干预,从而影响处理器运行速度,同时由于微控制器不断介入A/D控制会影响程序正常运行。

本文概述了基于FPGA的多路数据自动采集系统的设计和实现过程。

该系统采用高速A/D转换器将多路模拟信号转换成数字信号,以FPGA为控制核心产生各种控制时序,控制A/D和模拟量开关切换,并对转换结果进行数据读取保存在双口RAM中,通过试验验证表明该系统工作稳定,能够实现对多路采集信号实时采集处理,检测效果良好。

关键词:FPGA A/D转换自动采集Design of automatic acquisition and acquisition system based on FPGA multi A/DAbstract: In the past, A/D acquisition through the micro controller to control the complexity of the A/D chip logic. That not only increased the micro controller intervention, so that affecting the operating speed of the processor, but also affected the normal operation of the program when the micro controller continuous intervention the A/D conversion. This paper Summary the design and implementation of high speed multi channel data acquisition system based on FPGA, The system uses high speed A/D converter to convert multiple analog signals into digital signals. The FPGA is used as control core to generate various control timing, which is used to control A/D and analog switch, at the same time, the data that is converted is stored in dual port RAM. Through the experiment, the system is proved to can stably real-time process for multi-channel signal acquired system, and the examination effect is good. Key words: A/D FPGA Automatic Acquisition1 引言在高速多路数据采集系统中,通常采用数字信号处理器DSP或单片机作为微控制器,控制模数转换器AD及其他外围设备的工作。

基于FPGA的高精度AD采样实现

基于FPGA的高精度AD采样实现摘要:研究了基于FPGA的高精度A/D采样实现,FPGA选用altera公司cycloneII 系列芯片,AD转换器采用AD7606-4,该转换器具有4通道16位精度。

关键词:FPGA 仿真芯片1 系统原理FPGA可以根据用户的需要将多种芯片的功能集中实现,在可靠性要求较高,电路板要求越来越小的趋势下,FPGA的应用越来越广。

在设计完后,设计者可以对芯片的功能进行仿真验证,在线修改,大大减少了设计的复杂性。

AD7606-4是ADI公司推出的新一代16位、4通道同步采样的模拟数字转换器。

它采用5V单电源供电,不再需要正负双电源,并支持真正10V或5V的双极性信号输入。

所有的通道均能以高达200kSPS的速率进行采样。

本文研究了基于FPGA的A/D转换控制,图1是A/D与FPGA 的连接框图。

A/D的转换时间最快是5us。

由FPGA发出转换控制信号AD_CONVST,A/D复位信号AD_RESET,A/D读信号AD_RD,读使能信号AD_CS。

采用并行字节方式将A/D转换的信号通过数据线DA0-DA7读到FPGA中。

AD7606-4先发高字节,再发低字节;先对通道1进行转换,再对通道2,最后对通道3进行转换。

AD_RESET为高电平时A/D复位,AD_CONVST出现上升沿时,A/D开始模拟信号转换,转换时间最快为5us,设计者可以根据应用设计转换时间,在本程序中转换时间设置为10us。

模拟信号转换完的时间是2us,本程序中设计转换开始5us后,FPGA发出AD_RD信号,可以把转换完的数字信号读到FPGA中。

图2是采用并行字节读模式的时序图。

2 VHDL实现及仿真在Quartus II 集成开发环境中,采用VHDL实现FPGA对A/D 的采集,系统时钟选用24Mhz,以下程序实现转换控制信号AD_CONVST和读使能信号AD_CS:if clk_global&acute;event and clk_global=&acute;1&acute; thencount<=count+1;if count=2 then------------------实现转换信号AD_convst<=&acute;0&acute;;elsif count>=3 and count<=239 thenAD_convst<=&acute;1&acute;;end if;if count>=120 and count<=134 then -----实现CS信号CS<=&acute;0&acute;;elseCS<=&acute;1&acute;;end if;if count>=239 then --计数器回零count<=0;end if;end if;仿真结果如图3所示,其中AD_data_in是送给FPGA的AD转换后的数字信号,AD1_data_out,AD2_data_out,AD3_data_out,表示三路通道输出的16位数字信号,在本程序中只使用3路通道。

一种基于FPGA的多通道AD射频采样设计

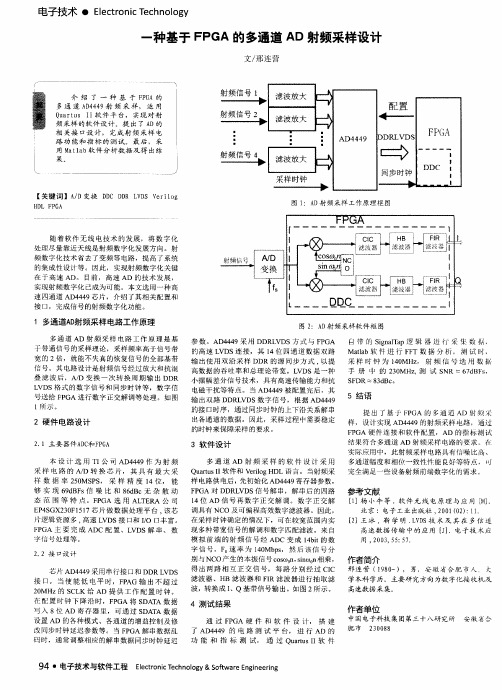

参 数 。AD4449采 用 DDRLVDS方 式 与 FPGA 的高速 LVDS连接,其 14位 四通道 数据双路 输 出使 用 双 沿 采 样 DDR 的源 同步 方 式 ,以提 高 数 据 的吞 吐 率 和 总 理 论 带 宽 。LVDS是 一 种 小 摆 幅 差 分 信 号 技 术 , 具 有 高速 传 输 能 力和 抗 电磁 干 扰 等 特 点 。当 AD4449被 配 置 完 后 , 其 输 出双路 DDRLVDS数 字信 号,根据 AD4449 的接 口时序,通 过同步时钟的上下沿 关系解 串 出 各 通 道 的 数 据 。 因 此 , 采样 过 程 中 需 要稳 定 的 时 钟 来 保 障采 样 的要 求 。

2 硬 件 电 路 设 计

2.1 主要 器 件 ADC和 FPGA

本 设 计 选 用 TI公 司 AD4449作 为 射 频 采 样 电 路 的 A/D 转 换 芯 片 , 其 具 有 最 大 采 样 数 据 率 250MSPS, 采 样 精 度 14位, 能 够 实 现 69dBFs信 噪 比 和 86dBc无 杂 散 动 态 范 围 等 特 点 。FPGA 选 用 ALTERA 公 司 EP4SGX230F1517芯 片 做 数 据 处 理 平 台 .该 芯 片 逻 辑 资 源 多 ,高速 LVDS接 口和 I/O 口丰 富 。 FPGA 主 要 完 成 ADC 配 置 、LVDS解 串 、 数 字 信 号 处 理 等 。

基于FPGA的ADC采集系统的设计_毕业设计论文

基于FPGA的ADC采集系统的设计摘要基于FPGA在高速数据采集方面有单片机和DSP无法比拟的优势,FPGA具有时钟频率高,内部延时小,全部控制逻辑由硬件完成,速度快,效率高,组成形式灵活等特点。

因此,本文研究并开发了一个基于FPGA的数据采集系统。

FPGA的IO口可以自由定义,没有固定总线限制更加灵活变通。

本文中所提出的数据采集系统设计方案,就是利用FPGA作为整个数据采集系统的核心来对系统时序和各逻辑模块进行控制。

依靠FPGA强大的功能基础,以FPGA作为桥梁合理的连接了ADC、显示器件以及其他外围电路,最终实现了课题的要求,达到了数据采集的目的。

关键词FPGA A/D转换AbstractFPGA is better than microcontroller and DSP in high speed data acquisition, FPGA has higher internal clock frequency, smaller delay than DSP,and all the control logic of FPGA is completed by hardware, FPGA has fast speed, high efficiency, and so on. Therefore, this paper introduces and develops a data acquisition system which is based on FPGA.The I/O pin of FPGA can be defined yourself without fixed limit,it’s very flexible. This design of data acquisition system use FPGA as the data acquisition system core to control the timing and the logic control module. Relying on the powerful function of FPGA, FPGA can connect ADC, display devices and other peripheral circuits, finally we can achieve the requirements of the subject, and the purpose of the data collection。

基于FPGA的高速A/D采样的实现

一

、

。GA P

F G 是 现 场 可 编 程 门 阵 列 ( id Porm b G t PA Fe rga mal a l e e

Ar ) r y 的简称 , a 是一种由用户实现芯片功能的器件 , 用户在设计 完成之后 可以进行功能和时序仿真 , 也可 以现场编程进行验证 ,

在4 K波特至 6 0 0 4 K波特之 间, 我们对信 号采用 I0解调Fra bibliotek式 , / 对

表 3 客户端速度测试结果

测试用例 同时传输会话数 传输时间( 秒) 】5 7 25 9

24 6 26 5

25 5 26 5

结果 7 MBS j2 , 43 4MBS /

C l A ry , C 由 可 配 置 逻 辑 模 块 C B( o f ual oi e r ) L A l a L C n grbe gc i L

Bok 、 l )输出输入模块 l B Ip tO tu lc ) c O (n u up tBok 和内部连线 3 类

可编 程单 元 组 成 。 其特 点 主要 有 : 用 FG 采 P A设 计 专 用 集 成 电 路 A I SC ( p l a o pcf n ga d Crut)真 正 达 到 用 户 自行 设 A pi t n S eicIt rt i i , ci i e e c s

1 " 3 , 526 节 0 144 , 字 0 9 1 " 3 , 526 节 0 144 , 字 0 9

1 I 44 5 2 0 3 .0 .96 l 3 .0 , 9 0 l 44 5 2 6

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于fpga的adc采样控制电路设计

FPGA(现场可编程门阵列)是一种高度可编程的数字电路设

计工具,可用于实现各种应用。

ADC(模拟数字转换器)是

一种电子设备,用于将模拟信号转换为数字信号。

在本文中,我们将设计一个基于FPGA的ADC采样控制电路。

首先,我们需要选择一个合适的ADC芯片,以满足我们的需求。

ADC芯片通常具有不同的分辨率(以位为单位)和采样

速率(以样本/秒为单位)。

选择适当的芯片将取决于被测信

号的频率范围和精度要求。

一旦我们选择了ADC芯片,我们

可以开始设计采样控制电路。

ADC采样控制电路的主要任务是控制ADC芯片的采样频率和

采样精度。

首先,我们需要使用FPGA来生成一个时序信号,用于控制ADC芯片的采样。

此时序信号应具有适当的频率,

以保证ADC芯片的采样和转换过程正常运行。

然后,我们需要将ADC芯片的采样结果传递给FPGA。

为此,我们可以使用串行通信接口(如SPI或I2C),在ADC芯片

和FPGA之间建立一个数据通道。

通过该通道,ADC芯片的

采样结果将传输到FPGA中进行后续处理。

一旦ADC芯片的采样结果进入FPGA,我们可以进行进一步

的数字信号处理。

我们可以使用FPGA内部的逻辑电路和存

储器来实现数字滤波、数字滤波等功能。

这些功能可以根据特定应用的需求进行定制。

最后,我们可以将FPGA处理后的数字信号输出到外部设备(如计算机)或其他电路中。

这些输出信号可以用于进一步分析、控制或存储。

总之,基于FPGA的ADC采样控制电路是一种常见的电路设计方法,可用于实现各种实时信号处理和控制应用。

通过适当选择ADC芯片和设计有效的采样控制电路,我们可以在FPGA上实现高性能、低功耗的ADC系统。

这种设计方法具有灵活性和可扩展性,适用于各种应用领域,如通信、医疗、工业控制等。