FPGA定时器24s倒计时.doc

篮球24S可控计时器

EDA设计基础实验课程论文题目篮球24S可控计时器学院通信与电子工程学院专业班级电子101学生姓名大彬哥指导教师大力会2013年6月18日摘要本次设计是基于FPGA的篮球计时器设计,利用Verilog HDL语言和Quartus II软件以及FPGA的实验操作平台来实现的。

重点是用硬件语言Verilog HDL来描述篮球计时,偏重于软件设计。

本次通过Verilog HDL语言编写一个具有显示24秒倒计时功能的计时器,计时器为24秒递减计时其计时间隔为1秒;计时器递减计时到零时,数码显示器不灭灯,同时发出光电报警信号等。

关键词:Verilog HDL语言 Quartus II软件篮球计时器AbstractThis design is the basketball timer design based on FPGA, using Verilog HDL language and Quartus II software and FPGA experimental platform to achieve. The focus is on using Verilog language HDL to describe time basketball, focused on the software design. Through this Verilog HDL language with a display timer of 24 seconds countdown timer, timer of 24 seconds decrease time the time interval of 1 second; timer decrease time to zero, digital display does not light, issued at the same time, photoelectric alarm signal.Keywords: Verilog HDL Quartus II basketball timer目录摘要 (I)Abstract (II)目录 (1)前言 (2)第一章计时器概述 (3)1.1篮球竞赛24秒计时器功能 (3)1.2 设计任务及要求 (3)1.2.1基本要求 (3)1.2.2 设计任务及目标 (3)1.2.3 主要参考器件: (3)第二章电路设计原理与单元模块 (4)2.1 设计原理 (4)2.2 设计方案 (5)2.3 单元模块 (6)2.3.1 8421BCD码递减计数器模块 (6)2.3.2 时钟模块 (8)2.3.3 辅助时序控制模块 (9)2.3.4 译码显示模块 (10)第三章安装与测试 (13)3.1 电路的安装 (13)3.2 电路的调试 (13)3.3编译和仿真波形 (13)3.3.1 仿真分析及结论 (14)3.3.2 故障分析和解决 (14)第四章实验体会 (15)结论 (16)结论 (16)致谢 (17)参考文献 (18)附录 (19)前言数字电子技术课程设计是数字电子技术学习中非常重要的一个环节,是将理论知识和实践能力相统一的一个环节,是真正锻炼学生能力的一个环节。

可控二十四秒倒计时报警及其显示电路设计

设计课题:篮球比赛二十四秒倒计时及其报警篮球比赛二十四秒倒计时及其报警一、设计任务与要求1.本设计只要用于篮球比赛中的24秒倒计时及其报警。

2.在设计完成后应该实现这样的功能:首先,按下“手动复位”弹键,使计数器回归24,当按下“手动开始”弹键时,计数器开始从24秒倒计时,直到计数为0时,报警器开始工作,此时若按下“手动复位”弹键,则报警器停止工作,计数器回归24秒。

若在计数中按下“手动复位”弹键,则计数器回归24秒,当再次按下“手动开始”弹键时,计数器再次工作。

3.总的来说,计时器的功能包括:计数、复位、暂停、报警。

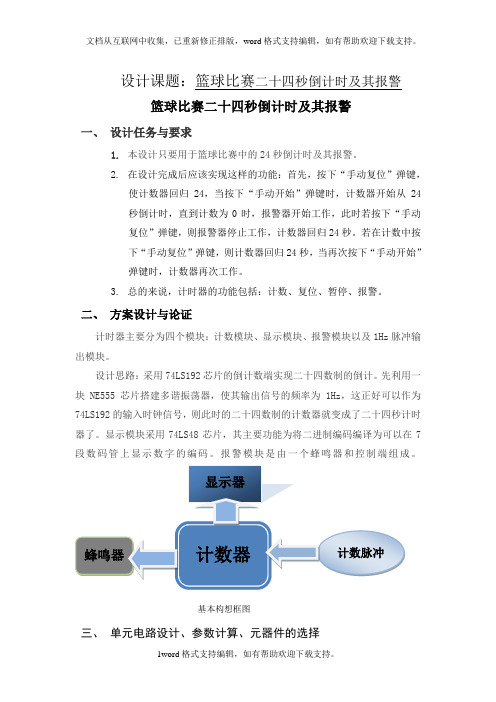

二、方案设计与论证计时器主要分为四个模块:计数模块、显示模块、报警模块以及1Hz脉冲输出模块。

设计思路:采用74LS192芯片的倒计数端实现二十四数制的倒计。

先利用一块NE555芯片搭建多谐振荡器,使其输出信号的频率为1Hz,这正好可以作为74LS192的输入时钟信号,则此时的二十四数制的计数器就变成了二十四秒计时7三、单元电路设计、参数计算、元器件的选择1.总体框图及其思路根据前面提到的设计思路可先画出总设计的基本构想框图,如上所示。

由总体框图可以清楚的看到本设计由四个最基本的模块组成,分别为:计数模块、显示模块、报警模块以及1Hz脉冲输出模块。

基本原理:计数脉冲负责产生一个频率为1Hz的脉冲信号,此信号作为计数器计数脉冲,因此,计数器就成为了最小单位为1秒的计时器了;计数器采用置数法连接,每当循环一周即24秒之后置数端有效,从而实现24秒的计时;当计时器从24倒计到0时,利用此时的输出信号特点可以控制蜂鸣器工作,从而实现报警;显示部分包括对二进制数的重新编码和显示,74LS48用来对二进制数重新编码,而此时可以用七段数码管作为显示。

综合起来就可以完成计时和报警等功能。

2. 各个模块设计○1计数模块的设计计数模块设计原理图基本原理:首先预置数,令置数状态时输出为24。

PL端为置数端,当PL 为0时,计数器输出为24。

24秒倒计时牌

1 设计任务描述1.1设计题目:24秒倒计时牌1.2设计要求1.2.1 设计目的(1)掌握24秒倒计时牌的组装方法与技巧;(2)掌握元器件的实现功能与使用;(3)能够通过对元器件组装来实现各种功能的电路;1.2.2 基本要求(1)可手动暂停,还原;(2)到0时有长报警,到倒数5秒时每秒有一声短报警;(3)可显示计数,每过十秒有一次闪烁;1.2.3 发挥部分(1)24秒可调;2 设计思路24秒倒计时器牌的核心部分是倒计时部分,我选择了两个74HC290连级来实现,因为它有置数端和预置端,可完成可调的倒计时器。

本次设计有基本要求:可手动暂停、还原;每十秒显示器闪烁一次;到倒数5秒时每秒有一声短报警,到0秒时是长报警,发挥部分是24秒可调。

首先是要给计时器提供一个秒脉冲发生器,由于555定时器内部的比较器灵敏度非常高,输出驱动电流大,功能灵活,而且采用差分电路形式,用555定时器组成的多谐振荡器的振荡频率手电源电压和温度变化的影响很小,因此采用555定时器来提供发生脉冲。

手动暂停还原中,由于需要暂时锁住显示器显示的数,所以可以在秒脉冲的输出端加一个开关,当要计数时关闭开关进行计数,需要暂停时断开开关终止秒脉冲的输入,即可实现手动暂停还原此时显示器保持原来的数字。

每十秒显示器闪烁一次,若想有闪烁效果需要给需要给显示器提供5~10赫兹的脉冲信号才能有闪烁效果,只要当个位为“0000”时闪烁即为每十秒闪烁一次,通过各种门电路把“0000”的信号与5~10赫兹的脉冲信号共同作用提供给显示器。

到5秒时开始每秒都有一次短报警,到0秒时是长报警,则十位输出是“0000”,5秒时个位的最高位也为零,使个位输出“101”、“100”、“011”、“010”、“001”时有效列真值表,通过门来连接;当为“000”时,为长报警。

给短报警一个500赫兹的脉冲信号,给长报警一个1000赫兹的脉冲信号,再通过一个或门来控制输出那个报警信号提供给报警电路。

FPGA定时器24s倒计时

设计一个用于篮球比赛的定时器。

要求:(1)定时时间为24秒,按递减方式计时,每隔1秒,定时器减1;(2)定时器的时间用两位数码管显示;(3)设置两个外部控制开关,开关K1控制定时器的直接复位/启动计时,开关K2控制定时器的暂停/连续计时;当定时器递减计时到零(即定时时间到)时,定时器保持零不变,同时发出报警信号,报警信号用一个发光二极管指示。

(4)输入时钟脉冲的频率为1kHz。

(5)用Verilog HDL语言设计,用Modelsim软件做功能仿真,用Quartus II综合。

(6)将设计代码和仿真代码写在作业本上。

module gcount(out,sel,clock_1k,clear,pause,gcon);input clock_1k,clear,pause;output [6:0] out;output sel,gcon;reg [6:0] out;reg sel,gcon;reg [3:0] cnt_sl,cnt_sh,count;reg [9:0] fenpin;wire clock_1 = fenpin[9]; // 1Hz;always @(posedge clock_1k or negedge clear)beginif (!clear)fenpin <= 10'b0;elsefenpin <= fenpin + 1;end//cnt_slalways@(posedge clock_1 or negedge clear)//always@(posedge clock_1 or negedge clear or posedge pause)beginif(!clear)cnt_sl<=4'h4;else if (!pause)cnt_sl<=cnt_sl;else if (cnt_sh == 0 && cnt_sl == 0)cnt_sl<=4'h0;else if (cnt_sl == 0)cnt_sl<=4'h9;elsecnt_sl<=cnt_sl-1;end//cnt_shalways@(posedge clock_1 or negedge clear)//always@(posedge clock_1 or negedge clear or posedge pause) beginif(!clear)cnt_sh<=4'h2;else if (!pause)cnt_sh <= cnt_sh;else if (cnt_sh == 0 && cnt_sl == 0)cnt_sh<=4'h0;else if (cnt_sl == 0)cnt_sh<=cnt_sh-1;elsecnt_sh <= cnt_sh;end//gcon//always@(posedge clock_1 or negedge clear)always@(cnt_sh or cnt_sl)beginif (cnt_sh == 0 && cnt_sl == 0)gcon<=1;elsegcon <= 0;end//regalways@(posedge clock_1k or negedge clear)beginif(!clear)sel<=0;elsesel <= ~sel;endalways @(sel)count = (sel == 0)?cnt_sh:cnt_sl;always @(count)begincase(count)4'b0000: out=7'b011_1111;4'b0001: out=7'b000_0110;4'b0010: out=7'b101_1011;4'b0011: out=7'b100_1111;4'b0100: out=7'b110_0110;4'b0101: out=7'b110_1101;4'b0110: out=7'b111_1101;4'b0111: out=7'b000_0111;4'b1000: out=7'b111_1111;4'b1001: out=7'b110_1111;default: out=7'b000_0000;endcaseendendmodule`timescale 1ns/1ns`include"./gcount.v"module test;reg Clock_1k,Clear,Pause;wire [6:0] Out;wire Sel,Gcon;initialbeginClock_1k<=0;Clear<=1;Pause<=1;#100 Clear<=0;#100 Clear<=1;#5000 Pause<=0;#5000 Pause<=1;#5000 Clear<=0;#5000 Clear<=1;endalways #1 Clock_1k<=~Clock_1k;gcount m(.out(Out),.sel(Sel),.clock_1k(Clock_1k),.clear(Clear),.pause(Pause),.gcon(Gcon));endmodule。

二十四秒倒计时器的设计(数字电子技术)

数字电子技术设计性实验方案设计题目:24秒倒计时器分院物理与电子工程学院专业物理学班级2010级物本(1)班学号2010405270姓名龙大洪2013年6月23日目录0 设计要求 (1)1 设计思路 (1)1.1 设计方框图 (1)1.2 元件选用 (2)2 电路及工作原理 (2)2.1 电路图 (2)2.2 工作原理 (3)2.2.1 预置数据 (3)2.2.2个位减计数 (3)2.2.3十位减计数 (3)2.2.4脉冲封锁电路 (3)0 设计要求一、计数开始时数码显示为24二、计时开始后数码显示由24递减三、计时到00时停止计时四、秒脉冲可直接用实验箱1HZ信号1 设计思路1.1 设计方框图十位减计数个位减计数1HZ减计数脉冲借位脉十位数码管个位数码管预置数预置数输入预置数封锁脉冲电路与非预置数减计数1.2 元件选用减计数器使用74LS192十进制可逆计数器;数码管选用实验箱带有CD4511的数码管;秒脉冲可直接用实验箱的1HZ时钟信号;与非门选用74LS00。

2 电路及工作原理2.1 电路图2.2 工作原理2.2.1 预置数据十位:D3D2D1D0=0010 数码管显示的十位是2个位D3D2D1D0=0100 数码管显示的个位是42.2.2个位减计数个位器件74LS192如下接:CR=0,LD=1,CPu=1,CPd接脉冲。

个位数字由9减到0循环2.2.3十位减计数十位器件74LS192如下接:CR=0,LD=1,CPu=1,CPd接个位BO借位端。

十位数字由2减到0。

(注:当个位十位为00时由脉冲封锁,不在进行减计数。

)2.2.4脉冲封锁电路本电路封锁脉冲直接由两个与非门构成接CPd 个位1HZ脉冲VCC5VU6A74LS00DU7A74LS00DVCC2143接BO十位当十位个位为00时,由十位BO端输出为低电平,再与1HZ脉冲经过如上电路,使得CPd(个位)输入为零。

脉冲不在起作用,显示00不在自动进行减计数,直到重新置数。

24S篮球倒计时器

Hale Waihona Puke • 泪滴化焊盘:执行菜单命令【工具】/ 【泪滴焊 盘】。 • 在PCB编辑环境下,单击菜单命令【文件】/【装

配输出】/【Generates pick and place files】。

底层和顶层电路

PCB图

总结

• 通过这次学习让我们这组人学会了如何手

工绘制元件,如何设置带子件的元器件。 通过此次项目的实施,更好的掌握了PCB 的设计方法,设计步骤。在这过程中虽然 出现过很多问题,但通过老师和同学的帮 助,也都迎刃而解了

• 布线规则:菜单命令【设计】/【规则】。要求:

VCC GND线宽40mil 安全间距15mil 信号线25mil。

• 首先局部布线电源、地线: • 执行菜单命令【自动布线】/【网络】,光标变为

十字形,单击GND / VCC网络中的任意焊盘或着 飞线,系统自动对GND / VCC布线,然后进行修 改。

• • • •

绘制带子件的元件

• (1)新建元件:执行【工具】/【新元件】/,在弹出的 • • • • • •

【New Component Name】对话框中输入新元件名。 (2)绘制第一个子件。添加第一个子件的引脚执行菜单 【放置】/【引脚】在图中放置,设置引脚属性。 注意放 置前把可视栅格、捕获栅格都设为5mil。 (3)为每个子件添加电源、地线。 (4)设置隐藏引脚。 (5)绘制第二个子件。执行【工具】/【创建元件】,然 后粘贴、复制就行了。 (6)设置元件属性。双击SCH Library面板上的【编辑】 按钮,打开元件编辑器,对元件盖属性。 (7)为元件添加封装。在属性对话框中,点右下角【追 加】,选FootPrint,弹出对话框对元件进行封装设置。

绘制的元件截图

数字电路课程设计_24秒倒计时

赣南师院物理与电子信息学院数字电路课程设计报告书姓名:班级:学号:时间:图1 总原理框图1.1 555定时器555定时器是一种多用途的数字-模拟混合集成电路,用它可以构成施密特触发器、单稳态触发器和多谐振荡器。

本设计用LM555CM定时器设计一个多谐振荡器给电路提供脉冲信号,产生的脉冲信号用由74LS192进行计数,且设置周期为1秒。

1.1.1555定时器管脚名称和功能图2 555的管脚名称1脚为接地端,也是芯片的公共端。

2脚为C2比较器的信号输入端V2l又称为触发端。

它们输入的信号可以图3 555定时器的内部结构1.1.3 555定时器的功能表输入各级输出T 1状态D RV 1l V 2L V 1C V 2C触发器输出Q 1+n输出V OT 1状态0 ⨯ ⨯ ⨯ ⨯0 低电平 导通 1 (32)V CC (31V CC ) 0 1 0 低电平 导通 1 (32)V CC (31V CC ) 0 0 1 高电平 截止 1 (32)V CC (31V CC ) 1 0 0 高电平 截止 1(32)V CC (31V CC ) 11Q不变不变表1 555定时器的功能表1.274LS192十进制同步加减计数器图5 74LS192的内部结构图1.2.374LS192的功能表表2 74LS192的功能表1.374LS48七段译码器本设计中用共阴极七段显示数码管,为使七段显示数码管能正常工作,将74LS190连接到74LS48,74LS48将高低电平信号译成数码管可读信号,从而实现数字的显示。

1.3.174LS48的引脚排列图6 74LS48的引脚排列1.3.274LS48的真值表表3 74LS48的逻辑功能真值表1.4共阴极数码管数码管有共阴和共阳之分,本设计使用共阴数码管,因为译码器使用为74LS48,相应的数码管要用相应的译码器才能实现译码和显示数字。

1.4.1共阴数码管的引脚排列和简易符号图7 八段共阴数码管图8 数码管简易图1.4.2 共阴数码管的内部结构图9 共阴数码管内部结构2电路分析和仿真结果由上对各个元件进行的简介以及相关的原理图,下面对电路进行分部分析。

基于FPGA的24小时时钟

XXXXXX课程设计报告电子线路设计课程设计报告[24小时时钟电路设计]小组成员:XXXXXXXXXXXXXX 院(系):电气信息工程学院年级专业:20XX级电子信息工程指导老师:XX XX XX 联系电话:XXXXXXXXX二〇XX年XX月摘要本设计为24小时时钟设计,具有时、分、秒计数显示功能,以24小时循环计时的时钟电路;具有时、分校准以及清零的功能。

本设计采用EDA技术,以硬件描述语言VHDL为系统逻辑描述手段设计文件,在QUARTUSⅡ工具软件环境下,采用自顶向下的设计方法,由各个基本模块共同构建了一个基于FPGA的数字钟。

系统由主控模块、分频模块、译码模块以及显示组成。

经编译和仿真所设计的程序,在可编程逻辑器件上下载验证,本系统能够完成时、分、秒的分别显示,由按键输入进行数字钟的清零功能。

关键词时钟,QUARTUSⅡ,VHDL,FPGAAbstractThe design for the 24-hour clock design, with hours, minutes, seconds count display, a 24-hour cycle of the clock timing circuit; with hours, minutes, and cleared the calibration function.This design uses EDA technology to hardware description language VHDL description of the means for the system logic design documents, software tools in QUARTUSⅡenvironment, using top-down design approach, from the various modules together to build a basic FPGA-based digital clock.System by the control module, frequency module, decoding module and display components. The compilation and simulation of the design process, in the download validation of programmable logic devices, the system can complete the hours, minutes, seconds, respectively, indicated by the key input for clear digital clock function.Keywords clock,QUARTUSⅡ,VHDL,FPGA目录摘要 (Ⅰ)ABSTRACT (Ⅱ)1 绪论 (1)1.1 题目意义 (1)1.2 设计要求 (1)2 设计的基本原理 (2)2.1 设计原理 (2)2.2 设计流程 (3)3 设计方案 (4)3.1 设计思路 (4)3.2 模块图和功能 (4)3.2.1 分频模块 (4)3.2.2 主控模块 (5)3.2.3 译码模块 (8)3.2.4 顶层模块 (10)4 测试 (11)4.1 模块仿真 (11)4.1.1 分频模块 (12)4.1.2 主控模块 (13)4.1.3 译码模块 (14)4.2 顶层模块仿真 (15)5 结论 (16)6 参考文献 (17)1 绪论1.1 题目意义现在是一个知识爆炸的新时代。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

设计一个用于篮球比赛的定时器。

要求:

(1)定时时间为 24 秒,按递减方式计时,每隔 1 秒,定时器减1;

(2)定时器的时间用两位数码管显示;

(3)设置两个外部控制开关,开关 K1 控制定时器的直接复位 / 启动计时,开关 K2 控制定时器的暂停 / 连续计时;当定时器递减计时到零(即定时时间到)时,定时器保持零不变,同

时发出报警信号,报警信号用一个发光二极管指示。

(4)输入时钟脉冲的频率为 1kHz。

(5)用 Verilog HDL语言设计,用Modelsim 软件做功能仿真,用Quartus II 综合。

(6)将设计代码和仿真代码写在作业本上。

module gcount(out,sel,clock_1k,clear,pause,gcon);

input clock_1k,clear,pause;

output [6:0] out;

output sel,gcon;

reg [6:0] out;

reg sel,gcon;

reg [3:0] cnt_sl,cnt_sh,count;

reg wire [9:0] fenpin;

clock_1 = fenpin[9]; // 1Hz;

always @(posedge clock_1k or negedge clear)

begin

if (!clear)

fenpin <= 10'b0;

else

fenpin <= fenpin + 1;

end

//cnt_sl

always@(posedge clock_1 or negedge clear)

//always@(posedge clock_1 or negedge clear or posedge pause) begin

if(!clear)

cnt_sl<=4'h4;

else if (!pause)

cnt_sl<=cnt_sl;

else if (cnt_sh == 0 && cnt_sl == 0)

cnt_sl<=4'h0;

else if (cnt_sl == 0)

cnt_sl<=4'h9;

else

cnt_sl<=cnt_sl-1;

end

//cnt_sh

always@(posedge clock_1 or negedge clear)

//always@(posedge clock_1 or negedge clear or posedge pause) begin

if(!clear)

cnt_sh<=4'h2;

else if (!pause)

cnt_sh <= cnt_sh;

else if (cnt_sh == 0 && cnt_sl == 0)

cnt_sh<=4'h0;

else if (cnt_sl == 0)

cnt_sh<=cnt_sh-1;

else

cnt_sh <= cnt_sh;

end

//gcon

//always@(posedge clock_1 or negedge clear)

always@(cnt_sh or cnt_sl)

begin

if (cnt_sh == 0 && cnt_sl == 0)

gcon<=1;

else

gcon <= 0;

end

//reg

always@(posedge clock_1k or negedge clear)

begin

if(!clear)

sel<=0;

else

sel <= ~sel;

end

always @(sel)

count = (sel == 0)?cnt_sh:cnt_sl;

always @(count)

begin

case(count)

4'b0000: out=7'b011_1111;

4'b0001: out=7'b000_0110;

4'b0010: out=7'b101_1011;

4'b0011: out=7'b100_1111;

4'b0100: out=7'b110_0110;

4'b0101: out=7'b110_1101;

4'b0110: out=7'b111_1101;

4'b0111: out=7'b000_0111;

4'b1000: out=7'b111_1111;

4'b1001: out=7'b110_1111;

default: out=7'b000_0000;

endcase

end

endmodule

`timescale 1ns/1ns

`include"./gcount.v"

module test;

reg Clock_1k,Clear,Pause;

wire [6:0] Out;

wire Sel,Gcon;

initial

begin

Clock_1k<=0;

Clear<=1;

Pause<=1;

#100 Clear<=0;

#100 Clear<=1;

#5000 Pause<=0;

#5000 Pause<=1;

#5000 Clear<=0;

#5000 Clear<=1;

end

always #1 Clock_1k<=~Clock_1k;

gcount

m(.out(Out),.sel(Sel),.clock_1k(Clock_1k),.clear(Clear),.pause(Pause),.gcon(Gco n));

endmodule。