实验四 计数器及其应用

北京科技大学数电实验四 Quartus II集成计数器及移位寄存器应用

北京科技大学实验报告学院:高等工程师学院专业:自动化(卓越计划)班级:自E181姓名:杨威学号:41818074 实验日期:2020 年5月26日一、实验名称:集成计数器及其应用1、实验内容与要求(1)用74161和必要逻辑门设计一个带进位输出的10进制计数器,采用同步置数方法设计;(2)用两个74161和必要的逻辑门设计一个带进位输出的60进制秒计数器;2、实验相关知识与原理(1)74161是常用的同步集成计数器,4位2进制,同步预置,异步清零。

引脚图功能表其中X。

3、10进制计数器(1)实验设计1)确定输入/输出变量输入变量:时钟信号CLK、复位信号CLRN;输出变量:计数输出QD、QC、QB、QA,进位输出RCO,显示译码输出OA、OB、OC、OD、OE、OF、OG2)计数范围:0000-10013)预置数值:00004)置数控制端LDN:计数到1001时输出低电平5)进位输出RCO:计数到1001时输出高电平画出如下状态转换表:CP QDQCQBQA0 00001 00012 00103 00114 01005 01016 01107 01117 10009 100110 0000(2)原理图截图仿真波形如下功能验证表格CLRN QD QC QB QA RCO0 0 0 0 0 01 0 0 0 1 01 0 0 1 0 01 0 0 1 1 01 0 1 0 0 01 0 1 0 1 01 0 1 1 0 01 0 1 1 1 01 1 0 0 0 01 1 0 0 1 11 0 0 0 0 04、60进制秒计数器(1)实验设计1)确定输入/输出变量输入变量:时钟信号CLK、复位信号CLRN;输出变量:计数十位输出QD2、QC2、QB2、QA2和计数个位输出QD1、QC1、QB1、QA1,进位输出RCO2)计数范围:0000 0000-0101 10013)预置数值:0000 00004)置数控制端LDN1(个位):计数到0101 1001时输出低电平5)清零端CLRN2(十位):计数到0110时输出低电平6)ENT:个位计数到1001时输出高电平7)进位输出RCO:计数到1001时输出高电平画出如下状态转换表CP QD2QC2QB2QA2QD1QC1QB1QA1CPQD2QC2QB2QA2QD1QC1QB1QA1CPQD2QC2QB2QA2QD1QC1QB1QA10 0000 0000 20 0010 0000 40 0100 00001 0000 0001 21 0010 0001 41 0100 00012 0000 0010 22 0010 0010 42 0100 00103 0000 0011 23 0010 0011 43 0100 00114 0000 0100 24 0010 0100 44 0100 01005 0000 0101 25 0010 0101 45 0100 01016 0000 0110 26 0010 0110 46 0100 01107 0000 0111 27 0010 0111 47 0100 01118 0000 1000 28 0010 1000 48 0100 10009 0000 1001 29 0010 1001 49 0100 100110 0001 0000 30 0011 0000 50 0101 000011 0001 0001 31 0011 0001 51 0101 000112 0001 0010 32 0011 0010 52 0101 001013 0001 0011 33 0011 0011 53 0101 001114 0001 0100 34 0011 0100 54 0101 010015 0001 0101 35 0011 0101 55 0101 010116 0001 0110 36 0011 0110 56 0101 011017 0001 0111 37 0011 0111 57 0101 011118 0001 1000 38 0011 1000 58 0101 100019 0001 1001 39 0011 1001 59 0101 100160 0000 0000 (2)设计原理图截图(3)实验仿真仿真波形:仿真结果表:5、实验思考题:(1)总结任意模计数器的设计方法。

数电实验报告:实验4-计数器及应用161

广东海洋大学学生实验报告书(学生用表)实验名称课程名称 课程号 学院(系)专业 班级 学生姓名 学号 实验地点 实验日期实验4 计数器及其应用一、实验目的1、熟悉中规模集成计数器的逻辑功能及使用方法2、掌握用74LS161构成计数器的方法3、熟悉中规模集成计数器应用二、实验原理计数器是典型的时序逻辑电路,它是用来累计和记忆输入脉冲的个数.计数是数字系统中很重要的基本操作,集成计数器是最广泛应用的逻辑部件之一。

计数器种类较多,按构成计数器中的多触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器;根据计数制的不同,可分为二进制计数器、十进制计数器和任意进制计数器;根据计数的增减趋势,又分为加法、减法和可逆计数器。

还有可预置数和可编程序功能计数器等。

本实验主要研究中规模十进制计数器74LS161的功能及应用。

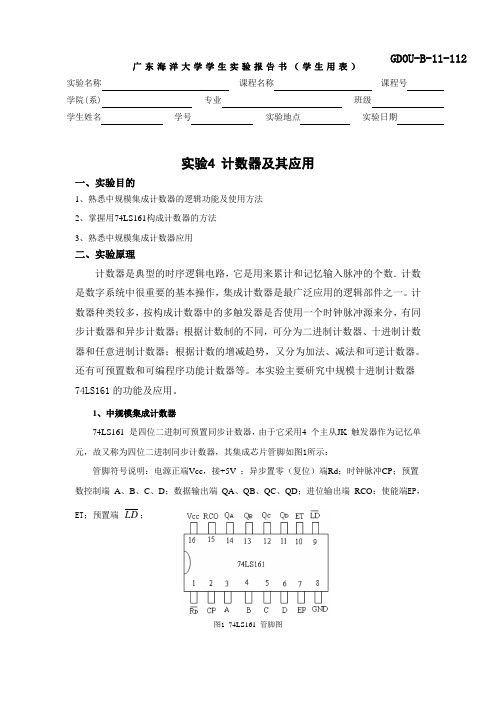

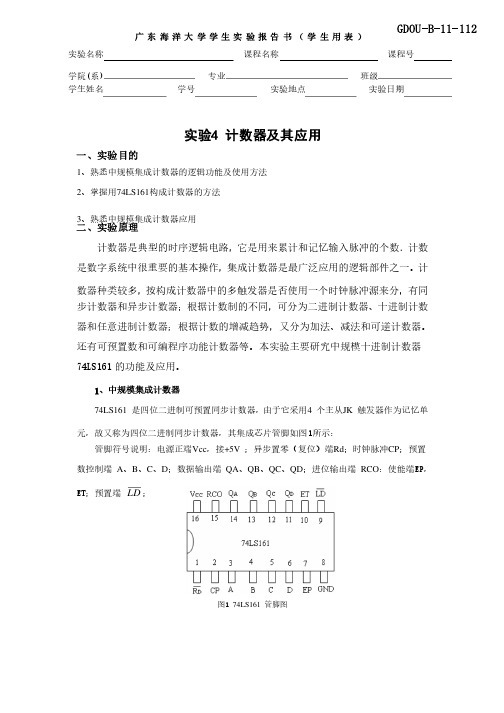

1、中规模集成计数器74LS161 是四位二进制可预置同步计数器,由于它采用4 个主从JK 触发器作为记忆单元,故又称为四位二进制同步计数器,其集成芯片管脚如图1所示:管脚符号说明:电源正端Vcc ,接+5V ;异步置零(复位)端Rd ;时钟脉冲CP ;预置数控制端 A 、B 、C 、D ;数据输出端 QA 、QB 、QC 、QD ;进位输出端 RCO :使能端EP ,ET ;预置端 LD ;图1 74LS161 管脚图GDOU-B-11-112该计数器由于内部采用了快速进位电路,所以具有较高的计数速度。

各触发器翻转是靠时钟脉冲信号的正跳变上升沿来完成的。

时钟脉冲每正跳变一次,计数器内各触发器就同时翻转一次,74LS161的功能表如表1所示:表1 74LS161 逻辑功能表2、实现任意进制计数器由于74LS161的计数容量为16,即计16个脉冲,发生一次进位,所以可以用它构成16进制以内的各进制计数器,实现的方法有两种:置零法(复位法)和置数法(置位法)。

(1) 用复位法获得任意进制计数器假定已有N进制计数器,而需要得到一个M进制计数器时,只要M<N,用复位法使计数器计数到M时置“0”,即获得M进制计数器。

实验4-计数器及其应用

实验四计数器及其应用

姓名:班级:

学号:同组人员:

一、实验目的:

(1)熟悉常用中规模计数器的逻辑功能。

(2)掌握二进制计数器和十进制计数器的工作原理和使用方法。

二、实验设备:

数字电路实验箱,数字万用表,数字双踪示波器,74LS90,74LS161及基本门电路。

三、实验原理:

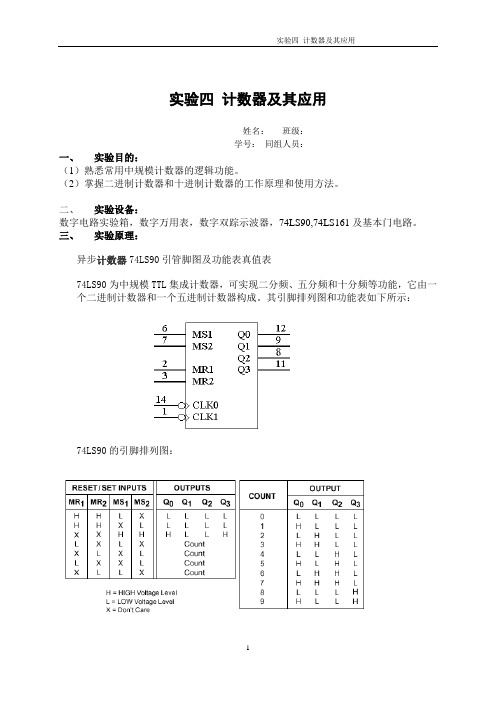

异步计数器74LS90引管脚图及功能表真值表

74LS90为中规模TTL集成计数器,可实现二分频、五分频和十分频等功能,它由一个二进制计数器和一个五进制计数器构成。

其引脚排列图和功能表如下所示:

74LS90的引脚排列图:

(1) 清除

令CR=1,其它输入为任意态,这时Q3Q2Q1Q0=0000,译码数字显示为0。

清除功能完成后,置CR=0

(2) 置数

CR=0,CP U,CP D任意,数据输入端输入任意一组二进制数,令LD= 0,观察计数

译码显示输出,予置功能是否完成,此后置LD=1。

(3) 加计数

CR=0,LD=CP D=1,CP U接单次脉冲源。

清零后送入10个单次脉冲,观察译码数字显示是否按8421码十进制状态转换表进行;输出状态变化是否发生在CP U的上升

沿。

(4) 减计数

CR=0,LD=CP U=1,CP D接单次脉冲源。

参照3)进行实验。

四、实验内容:

(1)产生10进制序列,从0~9显示。

(2)产生6进制序列,从0~5显示。

(3)产生如下序列:1,3,5,7,9,0,2,4,6,8并显示。

五、实验结果:。

数电实验报告:实验4-计数器及应用161

广东海洋大学学生实验报告书(学生用表)实验名称实验名称课程名称课程名称课程号课程号学院学院((系) 专业专业班级班级学生姓名学生姓名学号学号实验地点实验地点实验日期实验日期实验4 计数器及其应用一、实验目的1、熟悉中规模集成计数器的逻辑功能及使用方法、熟悉中规模集成计数器的逻辑功能及使用方法2、掌握用74LS161构成计数器的方法构成计数器的方法3、熟悉中规模集成计数器应用、熟悉中规模集成计数器应用二、实验原理计数器是典型的时序逻辑电路,它是用来累计和记忆输入脉冲的个数.计数是数字系统中很重要的基本操作,集成计数器是最广泛应用的逻辑部件之一。

计数器种类较多,按构成计数器中的多触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器;步计数器和异步计数器;根据计数制的不同,根据计数制的不同,根据计数制的不同,可分为二进制计数器、可分为二进制计数器、可分为二进制计数器、十进制计数十进制计数器和任意进制计数器;根据计数的增减趋势,又分为加法、减法和可逆计数器。

还有可预置数和可编程序功能计数器等。

本实验主要研究中规模十进制计数器74LS161的功能及应用。

的功能及应用。

1、中规模集成计数器74LS161 是四位二进制可预置同步计数器,由于它采用4 个主从JK 触发器作为记忆单元,故又称为四位二进制同步计数器,其集成芯片管脚如图元,故又称为四位二进制同步计数器,其集成芯片管脚如图11所示:所示:管脚符号说明:电源正端Vcc ,接+5V ;异步置零(复位)端Rd ;时钟脉冲CP ;预置数控制端数控制端 A 、B 、C 、D ;数据输出端;数据输出端 QA 、QB 、QC 、QD ;进位输出端;进位输出端 RCO :使能端:使能端EP EP EP,,ET ET;预置端;预置端;预置端LD ;图1 74LS161 管脚图管脚图GDOU-B-11-112该计数器由于内部采用了快速进位电路,所以具有较高的计数速度。

计数器及应用实验报告

计数器及应用实验报告计数器及应用实验报告引言:计数器是一种常见的电子设备,用于记录和显示特定事件或过程中发生的次数。

在实际应用中,计数器广泛用于各种领域,如工业自动化、交通管理、计时系统等。

本文将介绍计数器的原理、分类以及在实验中的应用。

一、计数器的原理计数器是由一系列的触发器组成的,触发器是一种能够存储和改变状态的电子元件。

计数器的工作原理是通过触发器的状态改变来记录和显示计数值。

当触发器的状态从低电平变为高电平时,计数器的计数值加一;当触发器的状态从高电平变为低电平时,计数器的计数值减一。

计数器可以根据需要进行正向计数、逆向计数或者同时进行正逆向计数。

二、计数器的分类根据计数器的触发方式,计数器可以分为同步计数器和异步计数器。

同步计数器是指所有触发器在同一个时钟脉冲的控制下进行状态改变,计数值同步更新;异步计数器是指触发器的状态改变不依赖于时钟脉冲,计数值异步更新。

根据计数器的位数,计数器又可以分为4位计数器、8位计数器、16位计数器等。

三、计数器的应用实验1. 实验目的本实验旨在通过设计和搭建一个简单的计数器电路,了解计数器的工作原理和应用。

2. 实验器材- 74LS74触发器芯片- 电路连接线- LED灯- 开关按钮3. 实验步骤步骤一:搭建计数器电路根据实验原理,将74LS74触发器芯片与LED灯和开关按钮连接起来,形成一个简单的计数器电路。

步骤二:测试计数器功能将电路连接到电源,并按下开关按钮。

观察LED灯的亮灭情况,记录计数器的计数值变化。

步骤三:应用实验根据实际需求,将计数器电路应用到实际场景中。

例如,可以将计数器电路连接到流水线上,用于记录产品的数量;或者将计数器电路连接到交通信号灯上,用于记录通过的车辆数量。

4. 实验结果与分析通过实验测试,我们可以观察到LED灯的亮灭情况,并记录计数器的计数值变化。

根据实验结果,我们可以验证计数器的功能是否正常。

在应用实验中,我们可以根据实际需求来设计和改进计数器电路,以满足不同场景下的计数需求。

计数器及其应用实验报告

一、实验目的1. 理解计数器的基本原理和构成方式。

2. 掌握中规模集成计数器的使用方法和功能测试。

3. 了解计数器在数字系统中的应用,如定时、分频、数字运算等。

二、实验原理计数器是一种时序逻辑电路,用于对输入脉冲进行计数。

根据计数进制、触发器翻转方式、计数功能等不同,计数器可以分为多种类型。

1. 计数进制:二进制、十进制、任意进制。

2. 触发器翻转方式:同步、异步。

3. 计数功能:加法、减法、可逆(加/减)。

常见的集成计数器有74LS161(4位二进制同步加法计数器)、74LS193(4位二进制同步可逆计数器)等。

三、实验器材1. 数字电路实验箱2. 同步十进制可逆计数器74LS1923. 2输入四与门74LS001四、实验步骤1. 搭建实验电路:根据实验要求,搭建计数器实验电路,包括计数器芯片、时钟源、复位端等。

2. 功能测试:分别对计数器进行加法计数、减法计数、可逆计数等功能的测试,观察输出波形和计数结果。

3. 应用实验:利用计数器实现定时、分频等功能,观察实际效果。

五、实验结果与分析1. 功能测试:- 加法计数:输入时钟脉冲,观察计数器输出端Q0~Q3的变化,验证加法计数功能。

- 减法计数:输入时钟脉冲,观察计数器输出端Q0~Q3的变化,验证减法计数功能。

- 可逆计数:输入时钟脉冲,观察计数器输出端Q0~Q3的变化,验证可逆计数功能。

2. 应用实验:- 定时功能:利用计数器实现定时功能,例如,通过计数器计数1000个脉冲,实现1秒定时。

- 分频功能:利用计数器实现分频功能,例如,将输入的50Hz时钟信号分频为5Hz。

六、实验总结通过本次实验,我们掌握了计数器的基本原理、构成方式和使用方法,了解了计数器在数字系统中的应用。

实验过程中,我们学会了如何搭建实验电路、进行功能测试和应用实验。

本次实验有助于提高我们对数字电路和时序逻辑电路的理解,为后续学习打下基础。

七、实验心得1. 计数器在数字系统中应用广泛,掌握计数器的基本原理和构成方式非常重要。

实验四 集成计数器及其应用(DOC)

实验四集成计数器及其应用实验性质:设计性一、实验目的⑴熟悉集成计数器的逻辑功能及各控制端的作用。

⑵掌握用集成计数器构成任意进制计数器的方法。

二、实验原理计数器是数字系统中必不可少的组成部分,它不仅用来计输入脉冲的个数,还大量用于分频、程序控制及逻辑控制等。

计数器种类繁多,其分类方式大致有以下三种:第一种:按计数器的进制分。

通常分为二进制、十进制和N进制计数器。

第二种:按计数脉冲输入方式不同,可分为同步计数器和异步计数器两大类。

同步计数器是指内部的各个触发器在同一时钟脉冲作用下同时翻转,并产生进位信号。

其计数速度快、工作频率高、译码时不会产生尖峰信号。

而异步计数器中的计数脉冲是逐级传送的,高位触发器的翻转必须等低一位触发器翻转后才发生。

其计数速度慢,在译码时输出端会出现不应有的尖峰信号,但其内部结构简单,连线少,成本低,因此,在一般低速场合中应用。

第三种:按计数加减分类。

则有递减、递加计数器和可逆计数器。

其中可逆计数器又有加减控制式和双时钟输入式两种。

针对以上计数器的特点,我们在设计电路时,可根据任务要求选用合适器件。

一些常用的计数器如表4-4-1所示。

下面我们以74LS160、74LS161、74LS190、74LS193、74LS290为例,介绍计数器的一般使用方法,对于表中的其它器件更详细功能介绍请参阅有关手册。

1. 四位二进制同步计数器74LS161其功能见表4-4-2所示,计数范围0~15。

0303端;CT T ,CT P :计数控制端;LD :同步并行置入控制端,低电平有效;CR :异步清除输入端,低电平有效。

该器件具有异步清零、同步预置数功能。

当CR =0时,计数器清零,Q 3Q 2Q 1Q 0=0000,与CP 无关;当CR =1、LD =0时,在CP 脉冲上升沿的作用下,D 3~D 0输入的数据d 3 d 2 d 1 d 0被置入计数器,即Q 3Q 2Q 1Q 0=d 3 d 2 d 1 d 0.进位输出CO= Q 3Q 2Q 1Q 0。

计数器及其应用实验报告

计数器及其应用实验报告实验目的,通过实验,掌握计数器的工作原理和应用,加深对数字电路的理解。

实验仪器,示波器、信号发生器、逻辑分析仪、计数器芯片等。

实验原理,计数器是一种能够在输入脉冲信号的作用下,按照一定规律进行计数的数字电路。

常见的计数器有二进制计数器、BCD计数器等。

在实验中,我们将使用示波器和信号发生器来观察计数器的工作状态,并利用逻辑分析仪来分析计数器的输出信号。

实验步骤:1. 连接实验电路,按照实验指导书上的电路图,连接计数器芯片、示波器、信号发生器和逻辑分析仪。

2. 设置信号发生器,将信号发生器设置为产生一定频率的脉冲信号,并输入到计数器的时钟输入端。

3. 观察示波器波形,使用示波器观察计数器的输出波形,记录下不同计数器状态下的波形特征。

4. 使用逻辑分析仪,利用逻辑分析仪来分析计数器的输出信号,观察计数器的工作状态和输出特点。

实验结果与分析:通过实验观察和分析,我们发现计数器在接收到时钟脉冲信号后,按照固定的规律进行计数。

不同类型的计数器在计数规律上有所不同,但都能够实现稳定的计数功能。

同时,我们还发现计数器的输出信号具有一定的脉冲特性,这对于数字电路的设计和应用具有重要意义。

实验应用:计数器在数字电路中有着广泛的应用,例如在计时器、频率计、脉冲计数等电路中都有计数器的身影。

通过本次实验,我们对计数器的工作原理和应用有了更深入的了解,为今后的电路设计和应用打下了良好的基础。

结论:本次实验通过观察和分析计数器的工作特性,加深了对数字电路中计数器的理解。

同时,实验还展示了计数器在数字电路中的重要应用,为今后的电路设计和应用提供了有益的参考。

通过本次实验,我们不仅掌握了计数器的工作原理和应用,还提高了实验操作能力和数据分析能力。

希望通过今后的实验学习,能够进一步深化对数字电路和计数器的理解,为将来的工程实践做好充分的准备。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验四计数器及其应用

一、实验目的

l、学习用集成触发器构成计数器的方法

2、掌握中规模集成计数器的使用及功能测试方法

3、运用集成计数计构成l位分频器

二、实验原理

计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

计数器种类很多。

按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。

根据计数制的不同,分为二进制计数器,十进制计数器和任意进制计数器。

根据计数的增减趋势,又分为加法、减法和可逆计数器。

还有可预置数和可编程序功能计数器等等。

目前,无论是TTL还是CMOS集成电路,都有品种较齐全的中规模集成计数器。

使用者只要借助于器件手册提供的功能表和工作波形图以及引出端的排列,就能正确地运用这些器件。

l、用D触发器构成异步二进制加/减计数器

图4-1是用四只D触发器构成的四位二进制异步加法计数器,它的连接特点是将每只D 触发器接成T’触发器,再由低位触发器的Q端和高—位的CP端相连接。

图4-1 四位二进制异步加法计数器

若将图4-l稍加改动,即将低位触发器的Q端与高一位的CP端相连接,即构成了一个4位二进制减法计数器。

2、中规模十进制计数器

CC40192是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,具引脚排列及逻辑符号如图4-2所示。

图4-2 CC40192引脚排列及逻辑符号

图中LD一置数端CP L一加计数端CP D一减计数端

CO一非同步进位输出端BO一非同步借位输出端

D0、D1、D2、D3一计数器输入端

Q0、Q1、Q2、Q3一数据输出端CR一清除端

CC40192(同74LS192,二者可互换使用)的功能如表4-1,说明如下:表4-1

当清除端CR为高电平“1”时,计数器直接清零;CR置低电平则执行其它功能。

当CR为低电平,置数端LD也为低电平时,数据直接从置数端D0、D1、D2、D3置入计数器。

当CR为低电平,LD为高电平时,执行计数功能。

执行加计数时,减计数端CP D接高

电平,计数脉冲由CP U输入;在计数脉冲上升沿进行842l码十进制加法计数。

执行减计数时,加计数端CPu接高电平,计数脉冲由减计数端CP D输入,表4-2为8421码十进制加、减计数器的状态转换表。

表4-2

3、计数器的级联使用

一个十进制计数器只能表示0~9十个数,为了扩大计数器范围,常用多个十进制计数器级联使用。

同步计数器往往设有进位(或借位)输出端,故可选用其进位(或借位)输出信号驱动下一级计数器。

图4-3是由CC40192利用进位输出CO控制高一位的CP U端构成的加数级联图。

图4-3 CC40192级联电路

4、实现任意进制计数

(1)用复位法获得任意进制计数器

假定已有N进制计数器,而需要得到一个M进制计数器时,只要M<N,用复位法使计数器计数到M时置“0”,即获得M进制计数器。

如图4-4所示为一个由CC40192十进制计数器接成的6进制计数器。

(2)利用预置功能获M进制计数器

图4-5为用三个CC40192组成的421进制计数器。

外加的由与非门构成的锁存器可以克服器件计数速度的离散性,保证在反馈置“0”信号作用下计数器可靠置“0”。

图4-4六进制计数器图4-5 421进制计数器

图4-6是一个特殊12进制的计数器电路方案。

在数字钟里,对时位的计数序列是1、2、…11,12、1、…是12进制的,且无0数。

如图所示,当计数到13时,通过与非门产生一个复位信号,使CC40192(2)(时十位)直接置成0000,而CC40192(1),即时的个位直接置成000l,从而实现了1—12计数。

三、实验设备与器件

1、十5V直流电源

2、双踪示波器

3、连续脉冲源

4、单次脉冲源

5、逻辑电平开关

6、逻辑电平显示器

7、译码显示器

8、CC4013×2(74LS74)CC40192×3(74LS192)

CC4011(74LS00)CC4012(74LS20)

四、实验内咨

1、用CC4013或74LS74 D触发器构成4位二进制异步加法计数器。

(1)按图4-1接线,R D接至逻辑开关输出插口,将低位CP0端接单次脉源,输出端Q3、Q2、

Q1、Q0接逻辑电平显示输入插口,各S D接高电平“1”。

(2) 清零后,逐个送入单次脉冲,观察并列表记录Q3~Q0状态。

(3) 将单次脉冲改为1HZ的连续脉冲,观察Q3~Q0的状态。

(4) 将1Hz的连续脉冲改为1KHz,用双踪示波器观察CP、Q3、Q2、Q1、Q0端波形,描绘之。

(5)将图4-1电路中的低位触发器的Q端与高一位的CP端相连接,构成减法计数器,按实验内容2),3),4)进行实验,观察并列表记录Q3~Q0的状态。

2、测试CC40192或74LSl92同步十进制可逆计数器的逻辑功能

计数脉冲由单次脉冲源提供,清除端CR、置数端LD、数据输入端D3、D2、D1、D0分别接逻辑开关,输出端Q3、Q2、Q1、Q0接实验设备的一个译码显示输入相应插口A、B、C、D;CO和BO接逻辑电平显示插口。

按表4-1逐项测试并判断该集成块的功能是否正常。

(1) 清除

令CR=1,其它输入为任意态,这时Q3Q2Q1Q0=0000,译码数字显示为0。

清除功能完成后,置CR=0

(2) 置数

CR=0,CP U,CP D任意,数据输入端输入任意一组二进制数,令LD=0,观察计数译码显示输出,予置功能是否完成,此后置面LD=1。

(3) 加计数

CR=0,LD=CP D=l,CP U接单次脉冲源。

清零后送入10个单次脉冲,观察译码数字显示是否按8421码十学制状态转换表进行:输出状态变化是否发生在CP U的上升沿。

(4) 减计数

CR=0,LD=CP U=l,CP D接单次脉冲源。

参照3)进行实验。

3、图4-3所示,用两片CC40192组成两位十进制加法计数器,输入1Hz连续计数脉冲,进行由00---99累加计数,记录之。

4、将两位十进制加法计数器改为两位十进制减法计数器,实现由99—00递减计数,记录之。

5、按图4-4电路进行实验,记录之。

6、按图4-5进行实验,记录之。

7、选作:设计一个数字钟移位60进制计数器并进行实验。

五、实验预习要求

1、复习有关计数器部分内容

2、绘出各实验内容的详细线路图

3、拟出各实验内容所需的测试记录表格

4、查手册,给出并熟悉实验所用各集成块的引脚排列图

六、实验报告

1、画出实验线路图,记录、整理实验现象及实验所得的有关波形。

对实验结果进行分析。

2、总结使用集成计数器的体会。