IEEE_745浮点数标准

(4) IEEE754标准浮点格式

2.1.3 数的定点表示与浮点表示2、浮点表示法(4) IEEE754标准浮点格式前面讨论的是原理性浮点格式,但实际计算机的浮点格式与此有一些差异。

下面简要介绍在当前主流微机中广泛采用的IEEE754标准浮点格式。

按IEEE754标准,常用的浮点数的格式如图2-3所示。

IEEE754有3种浮点表示格式,分别称为: 短浮点数(或称短实数)、长浮点数(或称长实数)、临时浮点数(或称临时实数)。

它们的具体格式如表2-4所示。

表2-4 IEEE754的3种浮点表示格式短浮点数又称为单精度浮点数,长浮点数又称为双精度浮点数,它们都采用隐含尾数最高数位(20)的方法,这样,无形中又增加了一位尾数,因此,相应地尾数真值实际上等于1+(23位尾数数值或52位尾数数值)。

临时浮点数又称为扩展精度浮点数,它没有隐含位,尾数真值就等于64位尾数数值。

下面以32位短浮点数为例,最高位是数符,其后是8位阶码,以2为底,采用移码表示,但偏置量为127,例如阶码真值为1,则阶码的代码值为128,这点与前述原理性偏置量(128)有点差异。

其余23位尾数为纯小数,因此,尾数位数实际上是:1位隐含位+23位尾数=24位。

注意:隐含的“1”是一位整数(即权位为20)。

在浮点格式中表示出来的23位尾数是纯小数,用原码表示。

例如: (15)10 =(1111)2 ,将它规格化后结果为1.111×2 3 ,其中整数部分的“1”将不存储在23位尾数内。

阶码是以移码形式存储的。

短浮点数的偏置值为十进制127或十六进制7FH ;长浮点数的偏置值为十进制1023或十六进制3FFH ;临时浮点数的偏置值为十进制16383或十六进制3FFFH 。

存储浮点数阶码部分之前,偏置值先要加到阶码真值上。

若阶码真值为3,在短浮点数中,移码表示的阶码为:十进制127+3=130或十六进制82H ;长浮点数中,移码表示的阶码为:十进制1023+3=1026或十六进制402H ;临时浮点数中,移码表示的阶码为:十进制16383+3=16386或十六进制4002H 。

IEEE 745浮点数标准

IEEE 745浮点数标准解读IEEE标准754:浮点数表示如须转载请注明作者为Lolita@,并请保持文章的完整和提供转载出处。

N的实际值n由下列式子表示:其中:★ n,s,e,m分别为N,S,E,M对应的实际数值,而N,S,E,M仅仅是一串二进制位。

★ S(sign)表示N的符号位。

对应值s满足:n>0时,s=0; n<0时,s=1。

★ E(exponent)表示N的指数位,位于S和M之间的若干位。

对应值e值也可正可负。

★ M(mantissa)表示N的尾数位,恰好,它位于N末尾。

M也叫有效数字位(sinificand)、系数位(coefficient), 甚至被称作“小数”。

三、浮点数格式IEEE标准754规定了三种浮点数格式:单精度、双精度、扩展精度。

前两者正好对应C语言里头的float、double或者FORTRAN里头的real、double精度类型。

限于篇幅,本文仅介绍单精度、双精度浮点格式。

★ 单精度:N共32位,其中S占1位,E占8位,M占23位。

★ 双精度:N共64位,其中S占1位,E占11位,M占52位。

上图中,|E|表示E的二进制序列表示的整数值,例如E为"10000100",则|E|=132,e=132-127=5 。

k则表示E的位数,对单精度来说,k=8,则bias=127,对双精度来说,k=11,则bias=1023。

此时m的计算公式如下图所示:标准规定此时小数点左侧的隐含位为1,那么m=|1.M|。

如M="101",则|1.M|=|1.101|=1.625,即 m=1.6252、非规格化:当E的二进制位全部为0时,N为非规格化形式。

此时e,m 的计算都非常简单。

注意,此时小数点左侧的隐含位为0。

为什么e会等于(1-bias)而不是(-bias),这主要是为规格化数值、非规格化数值之间的平滑过渡设计的。

后文我们还会继续讨论。

计算机系统结构课后习题答案(第2版)

习题一1、解释下列术语计算机系统的外特性:通常所讲的计算机系统结构的外特性是指机器语言程序员或编译程序编写者所看到的外特性,即由他们所看到的计算机的基本属性(概念性结构和功能特性)。

计算机系统的内特性:计算机系统的设计人员所看到的基本属性,本质上是为了将有关软件人员的基本属性加以逻辑实现的基本属性。

模拟:模拟方法是指用软件方法在一台现有的计算机上实现另一台计算机的指令系统。

可移植性:在新型号机出台后,原来开发的软件仍能继续在升级换代的新型号机器上使用,这就要求软件具有可兼容性,即可移植性。

可兼容性是指一个软件可不经修改或只需少量修改,便可由一台机器移植到另一台机器上运行,即同一软件可应用于不同环境。

Amdahl定律:系统中对于某一部件采用某种更快的执行方式所能获得的系统性能改进程度,取决于这种执行方式被使用的频度或占总执行时间的比例。

虚拟机(Virtual Machine):指通过软件模拟的具有完整硬件系统功能的、运行在一个完全隔离环境中的完整计算机系统。

6、7、假定求浮点数平方根的操作在某台机器上的一个基准测试程序中占总执行时间的20%,为了增强该操作的性能,可采用两种不同的方法:一种是增加专门的硬件,可使求浮点数平方根操作的速度提高为原来的20倍;另一种方法是提高所有浮点运算指令的速度,使其为原来的2倍,而浮点运算指令的执行时间在总执行时间中占30%。

试比较这两种方法哪一种更好些。

答:增加硬件的方法的加速比Sp1=1.23, 另一种方法的加速比Sp2=1.176,经计算可知Sp1=方法更好些。

Sp2>Sp2第一种9、假设高速缓存Cache的工作速度为主存的5倍,且Cache被访问命中的概率T=为90%,则采用Cache能使整个存储系统获得多高的加速比?答:加速比,其中tm=5tc,代入公式、得到加速比S=3.33。

11、Flynn分类法的依据是什么,它与按“并行级”和“流水级”的分类方法有什么不同?答:Flynn分类法的依据是指令流和数据流多倍性概念进行分类的。

ieee标准浮点数

ieee标准浮点数

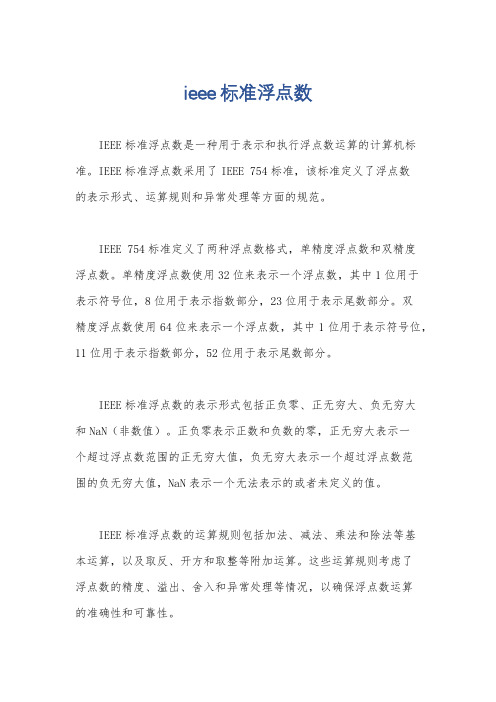

IEEE标准浮点数是一种用于表示和执行浮点数运算的计算机标准。

IEEE标准浮点数采用了IEEE 754标准,该标准定义了浮点数

的表示形式、运算规则和异常处理等方面的规范。

IEEE 754标准定义了两种浮点数格式,单精度浮点数和双精度

浮点数。

单精度浮点数使用32位来表示一个浮点数,其中1位用于

表示符号位,8位用于表示指数部分,23位用于表示尾数部分。

双

精度浮点数使用64位来表示一个浮点数,其中1位用于表示符号位,11位用于表示指数部分,52位用于表示尾数部分。

IEEE标准浮点数的表示形式包括正负零、正无穷大、负无穷大

和NaN(非数值)。

正负零表示正数和负数的零,正无穷大表示一

个超过浮点数范围的正无穷大值,负无穷大表示一个超过浮点数范

围的负无穷大值,NaN表示一个无法表示的或者未定义的值。

IEEE标准浮点数的运算规则包括加法、减法、乘法和除法等基

本运算,以及取反、开方和取整等附加运算。

这些运算规则考虑了

浮点数的精度、溢出、舍入和异常处理等情况,以确保浮点数运算

的准确性和可靠性。

在使用IEEE标准浮点数时,需要注意浮点数的精度损失和舍入误差。

由于浮点数的表示形式是有限的,因此在进行浮点数运算时可能会出现精度损失。

此外,由于浮点数的运算结果需要舍入到最接近的可表示值,因此可能会出现舍入误差。

总结来说,IEEE标准浮点数是一种用于表示和执行浮点数运算的计算机标准,它定义了浮点数的表示形式、运算规则和异常处理等方面的规范。

使用IEEE标准浮点数时需要注意精度损失和舍入误差。

IEEE 754关于浮点数的规定

把十进制数100.25转换成协处理器中的 例1 把十进制数 转换成协处理器中的 浮点数 解:1、进制转换: 、进制转换: (100.25)10=(1100100.01)2 2、规格化: 、规格化: (1100100.01)2=1.10010001×26 × =1.10010001×2110 × 3、计算阶码: 、计算阶码: 110+01111111=10000101 = 4、数值的符号位为:0, 、数值的符号位为: , 阶码为: 阶码为:10000101, , 尾数为: 尾数为: 1001 0001 0000 0000 0000 000

一、 IEEE754对阶码作如下规定 对阶码作如下规定

偏移阶码E 0 1 2 … 127 128 129 … 254 255 实际阶码值 保留做操作数 -126 -125 0 1 2 127 保留做操作数

ቤተ መጻሕፍቲ ባይዱ

二、对上溢和下溢的处理 当运算结果小于规格化浮点数所能表示的 最小值时,以前硬件处理策略,或者结果置0 最小值时,以前硬件处理策略,或者结果置 或者产生一个下溢陷阱, 或者产生一个下溢陷阱 , 这两种方案均不能 令人满意。 令人满意。 IEEE754处理方法是使用非规格化数 。 处理方法是使用非规格化数。 处理方法是使用非规格化数 这时阶码为0(即移码-127),尾数没有隐含 这时阶码为 (即移码 ) 最高位是0。 位,最高位是 。 这样的结果是降低精度,扩大表示范围。 这样的结果是降低精度,扩大表示范围。 如原来规格化单精度最小值是1.0x2-126,而非 如原来规格化单精度最小值是 而非 规格化单精度最小值是2 只有1 规格化单精度最小值是 -23 x2-126=2-149(只有 只有 位有效位) 位有效位 。

ieee 754-1985 浮点数表示方法

IEEE 754-1985 浮点数表示方法一、背景介绍IEEE 754-1985是一种用于计算机系统中浮点数表示的标准。

这一标准定义了浮点数的格式、表示范围、精度以及运算规则,是科学计算、工程计算和数据处理中广泛使用的一种标准。

它的出现改变了以往各种不同计算机系统之间浮点数表示的不一致性,促进了软件开发和数据交换的统一和规范化。

二、基本结构IEEE 754-1985标准定义了三种不同的浮点数格式:单精度、双精度和扩展双精度。

其中,单精度浮点数占用32位,双精度浮点数占用64位,扩展双精度浮点数占用80位。

这三种浮点数格式都包括三个部分:符号位(S)、指数位(E)和尾数位(M)。

具体的格式如下:1. 单精度浮点数符号位:1位指数位:8位尾数位:23位2. 双精度浮点数符号位:1位指数位:11位尾数位:52位3. 扩展双精度浮点数符号位:1位指数位:15位尾数位:64位三、浮点数表示范围根据IEEE 754-1985标准,不同格式的浮点数可以表示的范围也不同。

以双精度浮点数为例,它可以表示的范围大约是1.7 x 10^(-308)到1.7 x 10^308,而单精度和扩展双精度浮点数的表示范围也可以根据其格式类似地计算出来。

四、浮点数表示精度除了表示范围之外,IEEE 754-1985标准还规定了浮点数的表示精度。

双精度浮点数具有大约15位有效数字,这意味着它的表示精度可以达到小数点后15位。

单精度和扩展双精度浮点数的表示精度也可以通过类似的方式得出。

五、浮点数运算规则IEEE 754-1985标准还规定了浮点数的运算规则,包括加减乘除、开方、取模等一系列运算。

这些运算规则不仅规定了浮点数之间的运算规则,还规定了特殊值(如正无穷、负无穷、NaN)的处理方式,以及溢出、下溢等异常情况的处理方式。

六、浮点数表示的优缺点根据IEEE 754-1985标准,浮点数可以表示大范围的数值,并且具有较高的精度,这使得它在科学计算和工程计算中得到了广泛的应用。

ieee 754标准的浮点数表示方法

ieee 754标准的浮点数表示方法

IEEE 754标准定义了浮点数的表示方法,包括单精度和双精

度浮点数。

单精度浮点数(32位)的表示方法如下:

- 1位符号位(S),用来表示正负号,0表示正数,1表示负数。

- 8位指数位(E),用来表示指数部分,采用偏移表示法,即

真正的指数值等于E - 127,其中E的取值范围为1到254,保留了0和255两个特殊值。

- 23位尾数位(M),用来表示尾数部分,在计算机内部以二

进制表示的小数部分。

双精度浮点数(64位)的表示方法如下:

- 1位符号位(S),用来表示正负号,0表示正数,1表示负数。

- 11位指数位(E),用来表示指数部分,采用偏移表示法,

即真正的指数值等于E - 1023,其中E的取值范围为1到2046,保留了0和2047两个特殊值。

- 52位尾数位(M),用来表示尾数部分,在计算机内部以二

进制表示的小数部分。

根据上述规定,浮点数的数值表示为:(-1)^S * (1.M) * 2^(E-

偏移值)。

其中,(1.M)表示1加上尾数M的二进制表示值,偏移值为

127(对于单精度浮点数)或1023(对于双精度浮点数)。

例如,对于单精度浮点数0.15625,其二进制表示为:

- 符号位S为0表示正数。

- 指数位E为3,表示指数部分为3 - 127 = -124。

- 尾数位M为10000000000000000000000(二进制表示),表示尾数部分。

因此,浮点数0.15625的IEEE 754标准单精度表示为:0 01111100 10000000000000000000000。

ieee754浮点数的标准运算

IEEE 754标准是浮点数运算中广泛使用的一种标准,它定义了浮点数的表示和算术运算规则。

使用IEEE 754标准的浮点数在计算机科学和工程中扮演着重要的角色,因此对其标准运算进行深入的学习和理解具有重要意义。

1. IEEE 754浮点数的表示IEEE 754标准定义了浮点数的表示方式,它主要由三部分组成:符号位、指数位和尾数位。

具体而言,对于单精度浮点数,其总位数为32位,其中1位表示符号位,8位表示指数位,23位表示尾数位;对于双精度浮点数,其总位数为64位,其中1位表示符号位,11位表示指数位,52位表示尾数位。

通过这种表示方式,可以表示从非常小的数到非常大的数,以及在这些数之间的所有可能数值。

2. IEEE 754浮点数的算术运算IEEE 754标准定义了浮点数的算术运算规则,包括加法、减法、乘法和除法。

在这些算术运算中,需要考虑到浮点数的表示方式和精度限制,以及可能出现的溢出和舍入误差。

在进行浮点数的算术运算时,需要特别注意以下几点:a. 舍入误差由于浮点数的表示精度是有限的,因此在进行算术运算时往往会产生舍入误差。

这种误差可能会在多次运算后累积,导致最终结果的精度下降。

为了尽可能减小舍入误差,可以使用一些数值稳定的算法和技巧,例如Kahan算法和扩展精度算法等。

b. 溢出和下溢在进行加法、减法、乘法和除法运算时,需要考虑到可能出现的溢出和下溢情况。

当两个大数相加或相乘时,很可能会超出浮点数所能表示的范围,导致溢出;而当两个小数相减或相除时,很可能会得到一个接近于零的结果,导致下溢。

为了避免这些情况的发生,可以采用一些有效的方法,例如对数据进行归一化处理、使用大数运算库等。

3. IEEE 754浮点数的特殊值在IEEE 754标准中,还定义了一些特殊的浮点数值,例如正无穷大、负无穷大、NaN(Not a Number)等。

这些特殊值在实际计算中往往需要特别处理,以避免产生不确定的结果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

标题: 解读IEEE标准754:浮点数表示

一、背景

在IEEE标准754之前,业界并没有一个统一的浮点数标准,相反,很多计算机制造商都设计自己的浮点数规则,以及运算细节。

那时,实现的速度和简易性比数字的精确性更受重视。

直到1985年Intel打算为其的8086微处理器引进一种浮点数协处理器的时候,聪明地意识到,作为设计芯片者的电子工程师和固体物理学家们,也许并不能通过数值分析来选择最合理的浮点数二进制格式。

于是Intel在请加州大学伯克利分校的 William Kahan教授──最优秀的数值分析家之一来为8087 FPU设计浮点数格式; 而这个家伙又找来两个专家来协助他,于是就有了KCS组合(Kahn, Coonan, and Stone)。

他们共同完成了Intel的浮点数格式设计,而且完成地如此出色,以致于IEEE组织决定采用一个非常接近KCS的方案作为IEEE的标准浮点格式。

目前,几乎所有计算机都支持该标准,大大改善了科学应用程序的可移植性。

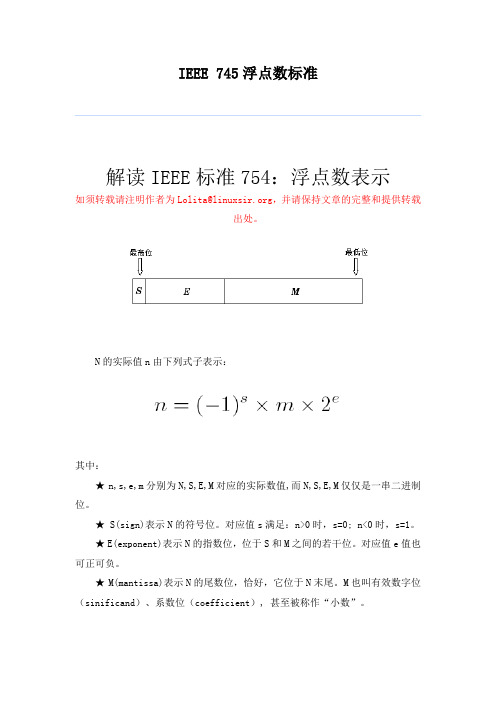

二、表示形式

从表面上看,浮点数也是一串0和1构成的位序列(bit sequence),并不是三头六臂的怪物,更不会咬人。

然而IEEE标准从逻辑上用三元组{S,E,M}表示一个数N,如下图所示:

N的实际值n由下列式子表示:

其中:

★ n,s,e,m分别为N,S,E,M对应的实际数值,而N,S,E,M仅仅是一串二进制位。

★ S(sign)表示N的符号位。

对应值s满足:n>0时,s=0; n<0时,s=1。

★ E(exponent)表示N的指数位,位于S和M之间的若干位。

对应值e值也可正可负。

★ M(mantissa)表示N的尾数位,恰好,它位于N末尾。

M也叫有效数字位(sinificand)、系数位(coefficient), 甚至被称作“小数”。

三、浮点数格式

IEEE标准754规定了三种浮点数格式:单精度、双精度、扩展精度。

前两者正好对应C语言里头的float、double或者FORTRAN里头的real、double精度类型。

限于篇幅,本文仅介绍单精度、双精度浮点格式。

★ 单精度:N共32位,其中S占1位,E占8位,M占23位。

★ 双精度:N共64位,其中S占1位,E占11位,M占52位。

值得注意的是,M虽然是23位或者52位,但它们只是表示小数点之后的二进制位数,也就是说,假定 M为“010110011...”, 在二进制数值上其实是“.010110011...”。

而事实上,标准规定小数点左边还有一个隐含位,这个隐含位通常,哦不,应该说绝大多数情况下是1,那什么情况下是0呢?答案是N

对应的n非常小的时候,比如小于 2^(-126)(32位单精度浮点数)。

不要困惑怎么计算出来的,看到后面你就会明白。

总之,隐含位算是赚来了一位精度,于是M对应的m最后结果可能是"m=1.010110011...”或者“m=0.010110011...”三、计算e、m

首先将提到令初学者头疼的“规格化(normalized)”、“非规格化(denormalized)”。

噢,其实并没有这么难的,跟我来!掌握它以后你会发现一切都很优雅,更美妙的是,规格化、非规格化本身的概念几乎不怎么重要。

请牢记这句话:规格化与否全看指数E!

下面分三种情况讨论E,并分别计算e和m:

1、规格化:当E的二进制位不全为0,也不全为1时,N为规格化形式。

此时e被解释为表示偏置(biased)形式的整数,e值计算公式如下图所示:

上图中,|E|表示E的二进制序列表示的整数值,例如E为"10000100",则

|E|=132,e=132-127=5 。

k则表示E的位数,对单精度来说,k=8,则bias=127,对双精度来说,k=11,则bias=1023。

此时m的计算公式如下图所示:

标准规定此时小数点左侧的隐含位为1,那么m=|1.M|。

如M="101",则

|1.M|=|1.101|=1.625,即 m=1.625

2、非规格化:当E的二进制位全部为0时,N为非规格化形式。

此时e,m 的计算都非常简单。

注意,此时小数点左侧的隐含位为0。

为什么e会等于(1-bias)而不是(-bias),这主要是为规格化数值、非规格化数值之间的平滑过渡设计的。

后文我们还会继续讨论。

有了非规格化形式,我们就可以表示0了。

把符号位S值1,其余所有位均置0后,我们得到了 -0.0; 同理,把所有位均置0,则得到 +0.0。

非规格化数还有其他用途,比如表示非常接近0的小数,而且这些小数均匀地接近0,称为“逐渐下溢(gra dually underflow)”属性。

3、特殊数值:当E的二进制位全为1时为特殊数值。

此时,若M的二进制位全为0,则n表示无穷大,若S为1则为负无穷大,若S为0则为正无穷大; 若M的二进制位不全为0时,表示NaN(Not a Number),表示这不是一个合法实数或无穷,或者该数未经初始化。

四、范例

仔细研读第四点后,再回忆一下文章开头计算n的公式,你应该写出一个浮点编码的实际值n了吧?还不能吗?不急,我先给你示范一下。

我们假定N是一个8位浮点数,其中,S占1位,E占4位,M占3位。

下面这张表罗列了N 可能的正数形式,也包含了e、m等值,请你对照着这张表,重温一下第四点,你会慢慢明白的。

说实在的,这张表花了我不少功夫呢,幸好TeX画表格还算省事!

这张表里头有很多有趣的地方,我提醒一下:

★ 看 N 列,从上到下,二进制位表示是均匀递增的,且增量都是一个最小二进制位。

这不是偶然,正是巧妙设计的结果。

观察最大的非规格数,发现恰好就是M全为1, E全为0的情况。

于是我们求出最大的非规格数为:

上面的公式中,h为M的位数(如范例中为3)。

注意,公式等号右边的第一项同时又是最小规格数的值(如范例中为 8/512 );第二项则正是最小非规格数的值(如范例中为1/512)即该浮点数能表示的最小正数。

★ 看 m 列,规格化数都是 1+ x 的形式,这个1正是隐含位1; 而非规格化数隐含位为0, 所以没有 "1+" 。

★ 看 n 列,非规格化数从上到下的增量都是 1/512, 且过渡到规格化数时,增量是平滑的,依旧是1/512。

这正是非规格化数中e等于(1-bias)而不是(-bias)的缘故,也是巧妙设计的结果。

再继续往下看,发现增量值逐渐增大。

可见,浮点数的取值范围不是均匀的。

五、实战

我们用一小段汇编来测试一下,浮点数在内存中是如何表示的。

测试环境:GentooLinux2006.0/GNU assembler version 2.16.1/GNU gdb 6.4/AMD XP1600+。

如下所示

代码:

(gdb) x/f &f20x80490a8 <f2>: 0.100000001

(gdb) x/xw &f20x80490a8 <f2>: 0x3dcccccd

(gdb)

从上面的gdb命令结果可以看出,浮点数5被表示为 0x40a00000,二进制形式为( 0100 0000 1010 0000 ... 0000 0000)。

红色数字为E,可以看出|E|=129>0, 则e=129-bias=129-127=2 ;蓝色数字为M, 且|E|>0,说明是规格化数,则

m=|1.M|=|1.01000..000|=1.25 ; 由n的计算公式可以求得 n=(-1)^0 * 1.25 * 2^2 = 5,结果被验证了。

同样,你也可以验证一下十进制浮点数0.1的二进制形式是否正确,你会发现,0.1不能表示为有限个二进制位,因此在内存中的表示是舍入(rounding)以后的结果,即 0x3dcccccd, 十进制为0.100000001,误差0.000000001由此产生了。

六、未完成

关于浮点数,还有很多东西(比如舍入误差、除零异常等等)值得我们深入探讨,但已经无法在此继续。

这篇文章的目的仅在初步解释IEEE标准754对浮点数的规定以及一些奇妙的地方。

写这篇文章花掉了我整天的时间,但也使我彻底记住了以前让我胆怯的东西──最重要的是,希望这篇文章对大家有点用处,也算我为计算机科学基础理论版以及做的一点贡献。