CameraLink转接板

CameraLink接口数字相机图像显示装置解读

Camera Link接口数字相机图像显示装置(技术)摘要:由于目前基于CameraLink接口的各种相机都不能直接显示,因此本文基于Xilinx公司的Spartan3系列FPGA XC3S1000-6FG456I设计了一套实时显示系统,该系统可以在不通过系统机的情况下,完成对相机CameraLink信号的接收、缓存、读取并显示。

系统采用两片SDRAM作为帧缓存,将输入的CameraLink信号转换成帧频为75Hz,分辨率为1,024×768的XGA格式信号,并采用ADV7123JST芯片实现数模转换,将芯片输出的信号送到VGA接口,通过VGA显示器显示出来。

设计的系统可以应用于各种基于CameraLink接口的相机输出信号的实时显示。

关键词:CameraLink; FPGA; SDRAM控制器;实时显示Research on the Real-time Display Technology Based on CameraLinkAbstract: All cameras based on the CameraLink interface cannot be displayed directly at present. Therefore, we designed a real-time display system based on the Xilinx Spartan3 FPGA XC3S1000-6FG456I.Our system could receive, store, read and display the CameraLink signal without the system computer. Two SDRAMs were used as frame storage. Input CameraLink signal was converted to XGA signal with 1024×768 pixles/frame at 75 frame/s. The ADV7123JST was used as D/A convertor. Its output signal was transmitted to the VGA interface and displayed on the screen of the VGA monitor. Our system could display the output signal of all cameras based on the CameraLink interface.Keywords: CameraLink; FPGA; SDRAM controller; real-time display目录第一章绪论 (3)1.1 引言 (3)1.2数字图像处理的发展 (3)1.3 目的及意义 (4)1.4 国内外研究现状 (5)第2章视频显示原理和显示格式的转换算法综述 (7)2.1视频显示的原理 (7)2.2目前视频显示格式转换算法综述 (8)2.2.1图像尺寸变换的插值方法综述 (9)2.2.2每秒帧数变换方法综述 (11)2.2.3插值算法选择判断的原则 (11)第三章视频显示格式转换的插值算法方案 (12)3.1图像尺寸变换采用的算法方案 (12)3.2每秒帧数变换采用的算法方案 (14)3.3视频显示格式转换中的像素处理方案 (16)第四章实时显示系统装置 (17)4.1.实时显示系统总体设计 (18)4.2 FPGA概述 (18)4.3 Camera Link结构与原理 (20)4.4 SDRAM控制器设计 (22)4.5 VGA显示接口设计 (24)参考文献 (25)第一章绪论1.1 引言Cameralink相机以其可靠性高,稳定性好,独立性好和易用等优势,成为现阶段工业大分辨率数字相机的必配接口,相机LVDS信号由专业图像采集卡解码通过一台性能良好的计算机计算最后在计算机显示器上完成图像显示或在计算机硬盘上存储等后续数字图像处理操作。

北京大恒图像视觉有限公司产品手册说明书

定制化产品手册北京大恒图像视觉有限公司Beijing Daheng Image Vision Co.,Ltd.产品介绍About UsIntroductionCooperation公司简介行业合作大恒图像像像大恒图像大恒图像大恒码:������)。

公司是中国最早成立的专注于视觉图像技术的企业,自成立之日起,一直坚持以技术开发为主的发展道路,连续十六年被中关村科技园区认定为高新技术企业。

公司于���� 年通过ISO����:���� 质量管理体系认证。

商。

我们的印刷检测系列产品已广泛应用于国内各类印刷企业,市场占有率稳居第一,并出口欧洲、美洲、亚洲、大洋洲等海外国家和地区。

目前,已有超过����台/套印刷检测设备服务于各类客户现场。

大恒图像像像大恒图像大恒图像大恒恒久品质大家风范大恒图像像像大恒图像大恒图像大恒着“伙伴”的责任,以唯有为客户创造价值才能实现自身价值的合作共赢模式,踏实前行,与客户共同成长。

我们希望能够发挥自己的力量,为中国机器视觉行业的发展带来新的探索和思路,为信任和支持我们的客户创造更高的价值,赢得经久不息的掌声。

大像像北京大恒图像视觉有限公司AIA证书高层�%其他EMVA证书质量体系证书质量体系证书中国机器视觉产业联盟发起单位大恒图像像像大恒图像大恒图像大恒Chromasens、MVTec、Schneider,瑞士AOS,日本BlueVision,加拿大Osela等。

视觉部件直接厂商供货,引进国际最先进的产品和技术,保护客户投资,保障售后维保。

大恒图像像像大恒图像大恒图像大产品介绍INTRODUCTION大恒图像像像大恒图像大恒图像大像系统参数:02可检缺陷类型短路、断路、线宽、线细、绝缘间距不足、线缺口、线凸起、浆料上异物、多图形、少图形、异物、脏污图像采集分辨率�.�um/像素(特殊需求可定制)检测速度≤��s/片(�英寸(���*���mm)料片,含机构运行时间)缺陷检测精度��um (特殊需求可定制)适应料片尺寸≤�英寸(���*���mm)大恒图像像像大恒图像大恒图像大恒03缺陷图例:断路缺口墨点缺口缺图形多图形浆料金属化绝缘间距不足脏污绝缘间距不足异物线宽不足大恒图像像像大恒图像大恒图像大恒04全自动化检测,在线离线可选,检测精度高达�um;自适应识别,自动规划路径,根据大小自主拍照检测;高效率,快速检测不停线,维护方便。

一种TLK2711传输接口与Camera-Link传输接口的转换电路[发明专利]

![一种TLK2711传输接口与Camera-Link传输接口的转换电路[发明专利]](https://img.taocdn.com/s3/m/cbc8d71b4a73f242336c1eb91a37f111f1850db8.png)

(19)中华人民共和国国家知识产权局(12)发明专利申请(10)申请公布号 (43)申请公布日 (21)申请号 201810215519.X(22)申请日 2018.03.15(66)本国优先权数据201810186505.X 2018.03.07 CN(71)申请人 中国科学院西安光学精密机械研究所地址 710119 陕西省西安市高新区新型工业园信息大道17号(72)发明人 闫鹏 孔亮 李立波 温志刚 刘永征 胡炳樑 魏文鹏 刘文龙 张昕 刘宏 (74)专利代理机构 西安智邦专利商标代理有限公司 61211代理人 杨引雪(51)Int.Cl.G06F 13/38(2006.01)G06F 13/40(2006.01)(54)发明名称一种TLK2711传输接口与Camera-Link传输接口的转换电路(57)摘要本发明提供一种T L K 2711传输接口与Camera-Link传输接口的转换电路,包括数据串行输入单元、FPGA单元及数据输出单元;数据串行输入单元包括对外连接器及至少一片TLK2711接收芯片;FPGA单元包括与TLK2711接收芯片一一对应的处理单元,处理单元包括输入逻辑单元、FIFO及输出逻辑单元;数据输出单元包括与TLK2711接收芯片一一对应的Camera-Link发送芯片及Camera-Link接口;TLK2711接收芯片与对外连接器串联;输入逻辑单元的输入端与TLK2711接收芯片的输出端连接;FIFO的输入端与输入逻辑单元的输出端连接;输出逻辑单元的输入端与FIFO的输出端连接,输出逻辑单元的输出端与Camera-Link发送芯片的输入端连接,Camera-Link接口与Camera-Link发送芯片串联。

本发明解决了TLK2711数据传输接口向Camera-Link标准图像传输接口转换的实际应用问题。

权利要求书1页 说明书4页 附图2页CN 108319560 A 2018.07.24C N 108319560A1.一种TLK2711传输接口与Camera -Link传输接口的转换电路,其特征在于:包括数据串行输入单元、FPGA单元及数据输出单元;所述数据串行输入单元包括对外连接器及至少一片TLK2711接收芯片;所述FPGA单元包括与TLK2711接收芯片一一对应的处理单元,所述处理单元包括输入逻辑单元、FIFO及输出逻辑单元;所述数据输出单元包括与TLK2711接收芯片一一对应的Camera -Link发送芯片及Camera -Link接口;所述TLK2711接收芯片与对外连接器串联;所述输入逻辑单元的输入端与TLK2711接收芯片的输出端连接,将传输的数据转化为以像素为单元的数据形式;所述FIFO的输入端与输入逻辑单元的输出端连接,按像素进行数据缓存;所述输出逻辑单元的输入端与FIFO的输出端连接,输出逻辑单元的输出端与Camera -Link发送芯片的输入端连接,输出逻辑单元将数据按照实际图像的大小和量化位数,产生行同步、帧同步、数据有效信号及数据并按Camera -Link数据传输协议发送给Camera -Link 发送芯片;所述Camera -Link接口与Camera -Link发送芯片串联。

CameraLink 图像采集接口电路1 (2)

CameraLink 图像采集接口电路1.Camera Link标准概述Camera Link 技术标准是基于 National Semiconductor 公司的 Channel Link 标准发展而来的,而 Channel Link 标准是一种多路并行 LVDS 传输接口标准。

低压差分信号( LVDS )是一种低摆幅的差分信号技术,电压摆幅在 350mV 左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在 1.923Gbps 。

90 年代美国国家半导体公司( National Semiconductor )为了找到平板显示技术的解决方案,开发了基于 LVDS 物理层平台的 Channel Link 技术。

此技术一诞生就被进行了扩展,用来作为新的通用视频数据传输技术使用。

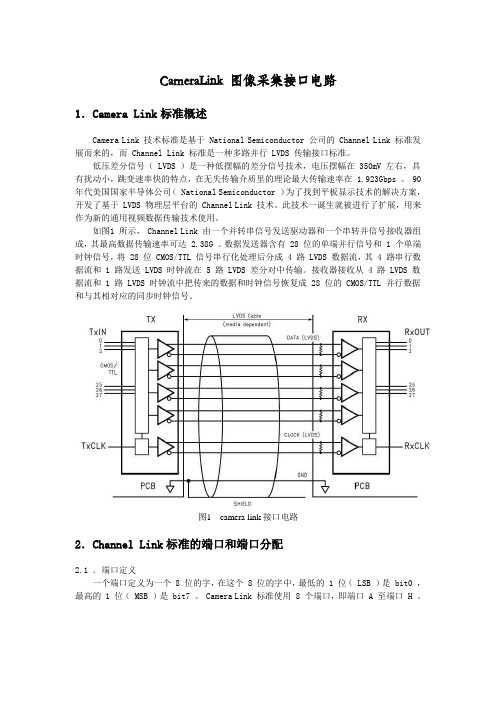

如图1 所示, Channel Link 由一个并转串信号发送驱动器和一个串转并信号接收器组成,其最高数据传输速率可达 2.38G 。

数据发送器含有 28 位的单端并行信号和 1 个单端时钟信号,将 28 位 CMOS/TTL 信号串行化处理后分成 4 路 LVDS 数据流,其 4 路串行数据流和 1 路发送 LVDS 时钟流在 5 路 LVDS 差分对中传输。

接收器接收从 4 路 LVDS 数据流和 1 路 LVDS 时钟流中把传来的数据和时钟信号恢复成 28 位的 CMOS/TTL 并行数据和与其相对应的同步时钟信号。

图1 camera link接口电路2.Channel Link标准的端口和端口分配2.1 .端口定义一个端口定义为一个 8 位的字,在这个 8 位的字中,最低的 1 位( LSB )是 bit0 ,最高的 1 位( MSB )是 bit7 。

Camera Link 标准使用 8 个端口,即端口 A 至端口 H 。

2.2 .端口分配在基本配置模式中,端口 A 、 B 和 C 被分配到唯一的 Camera Link 驱动器 / 接收器对上;在中级配置模式中,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上;在完整配置模式中,端口 A 、 B 和 C 被分配到第一个驱动器 / 接收器对上,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上,端口 G 和 H 被分配到第三个驱动器 / 接收器对上(见图2 )。

3-CameraLink接口-时序控制 (2)

CameraLink接口1.CameraLink接口简介1.1CameraLink标准概述Camera Link 技术标准是基于 National Semiconductor 公司的 Channel Link 标准发展而来的,而 Channel Link 标准是一种多路并行 LVDS 传输接口标准。

低压差分信号( LVDS )是一种低摆幅的差分信号技术,电压摆幅在 350mV 左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在 1.923Gbps 。

90 年代美国国家半导体公司( National Semiconductor )为了找到平板显示技术的解决方案,开发了基于 LVDS 物理层平台的 Channel Link 技术。

此技术一诞生就被进行了扩展,用来作为新的通用视频数据传输技术使用。

如图1.1所示, Channel Link 由一个并转串信号发送驱动器和一个串转并信号接收器组成,其最高数据传输速率可达 2.38G 。

数据发送器含有 28 位的单端并行信号和 1 个单端时钟信号,将 28 位 CMOS/TTL 信号串行化处理后分成 4 路 LVDS 数据流,其 4 路串行数据流和 1 路发送 LVDS 时钟流在 5 路 LVDS 差分对中传输。

接收器接收从 4 路 LVDS 数据流和 1 路 LVDS 时钟流中把传来的数据和时钟信号恢复成 28 位的 CMOS/TTL 并行数据和与其相对应的同步时钟信号。

图1.1 camera link接口电路1.2CameraLink端口和端口分配1.2.1端口分配在基本配置模式中,端口 A 、 B 和 C 被分配到唯一的 Camera Link 驱动器 / 接收器对上;在中级配置模式中,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上;在完整配置模式中,端口 A 、 B 和 C 被分配到第一个驱动器 / 接收器对上,端口 D 、 E 和F 被分配到第二个驱动器 / 接收器对上,端口 G 和 H 被分配到第三个驱动器 / 接收器对上。

3-CameraLink接口-时序控制

CameraLink接口

1.CameraLink接口简介

1.1CameraLink标准概述

CameraLink技术标准是基于NationalSemiconductor公司的ChannelLink标准发展而来的,而ChannelLink标准是一种多路并行LVDS传输接口标准。

低压差分信号(LVDS)是一种低摆幅的差分信号技术,电压摆幅在350mV左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在1.923Gbps。

90年代美国国家半导体公司(NationalSemiconductor)为了找到平板显示技术的解决方案,开发了基于LVDS物理层平台的

如图

位

5路LVDS

恢复成

A、B 和C

口G和芯

E和H,

那么

H的8

从

中读取处FPGA DDR 包括2RAM 另外,

子模块来完成位宽的转换。

2.4modelsim仿真结果

图2.4modelsim仿真结果

如图2.4,被测FPGA每来一个行同步,CameraLink模块获取行地址后读取DDR2中的数据写入缓存模块,等到下一个行同步来的时候把所读的数据从缓存模块中输出。

实际要求的是每个行同步来后要读取一行数据,大小为2048x12bit,为了缩小仿真时间,仿真时没一行的数据长度为:80x12bit。

图2.5五路CameraLink仿真输出

如图2.5,当下个行同步来的时候缓存数据输出,输出的数据时连续的。

CameraLink图像采集接口电路1(2)详解

CameraLink 图像采集接口电路1.Camera Link标准概述Camera Link 技术标准是基于 National Semiconductor 公司的 Channel Link 标准发展而来的,而 Channel Link 标准是一种多路并行 LVDS 传输接口标准。

低压差分信号( LVDS )是一种低摆幅的差分信号技术,电压摆幅在 350mV 左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在 1.923Gbps 。

90 年代美国国家半导体公司( National Semiconductor )为了找到平板显示技术的解决方案,开发了基于 LVDS 物理层平台的 Channel Link 技术。

此技术一诞生就被进行了扩展,用来作为新的通用视频数据传输技术使用。

如图1 所示, Channel Link 由一个并转串信号发送驱动器和一个串转并信号接收器组成,其最高数据传输速率可达 2.38G 。

数据发送器含有 28 位的单端并行信号和 1 个单端时钟信号,将 28 位 CMOS/TTL 信号串行化处理后分成 4 路 LVDS 数据流,其 4 路串行数据流和 1 路发送 LVDS 时钟流在 5 路 LVDS 差分对中传输。

接收器接收从 4 路 LVDS 数据流和 1 路 LVDS 时钟流中把传来的数据和时钟信号恢复成 28 位的 CMOS/TTL 并行数据和与其相对应的同步时钟信号。

图1 camera link接口电路2.Channel Link标准的端口和端口分配2.1 .端口定义一个端口定义为一个 8 位的字,在这个 8 位的字中,最低的 1 位( LSB )是 bit0 ,最高的 1 位( MSB )是 bit7 。

Camera Link 标准使用 8 个端口,即端口 A 至端口 H 。

2.2 .端口分配在基本配置模式中,端口 A 、 B 和 C 被分配到唯一的 Camera Link 驱动器 / 接收器对上;在中级配置模式中,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上;在完整配置模式中,端口 A 、 B 和 C 被分配到第一个驱动器 / 接收器对上,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上,端口 G 和 H 被分配到第三个驱动器 / 接收器对上(见图2 )。

CameraLink图像采集接口电路1(2)

CameraLink 图像采集接口电路1.Camera Link标准概述Camera Link 技术标准是基于 National Semiconductor 公司的 Channel Link 标准发展而来的,而 Channel Link 标准是一种多路并行 LVDS 传输接口标准。

低压差分信号( LVDS )是一种低摆幅的差分信号技术,电压摆幅在 350mV 左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在 1.923Gbps 。

90 年代美国国家半导体公司( National Semiconductor )为了找到平板显示技术的解决方案,开发了基于 LVDS 物理层平台的 Channel Link 技术。

此技术一诞生就被进行了扩展,用来作为新的通用视频数据传输技术使用。

如图1 所示, Channel Link 由一个并转串信号发送驱动器和一个串转并信号接收器组成,其最高数据传输速率可达 2.38G 。

数据发送器含有 28 位的单端并行信号和 1 个单端时钟信号,将 28 位 CMOS/TTL 信号串行化处理后分成 4 路 LVDS 数据流,其 4 路串行数据流和 1 路发送 LVDS 时钟流在 5 路 LVDS 差分对中传输。

接收器接收从 4 路 LVDS 数据流和 1 路 LVDS 时钟流中把传来的数据和时钟信号恢复成 28 位的 CMOS/TTL 并行数据和与其相对应的同步时钟信号。

图1 camera link接口电路2.Channel Link标准的端口和端口分配2.1 .端口定义一个端口定义为一个 8 位的字,在这个 8 位的字中,最低的 1 位( LSB )是 bit0 ,最高的 1 位( MSB )是 bit7 。

Camera Link 标准使用 8 个端口,即端口 A 至端口 H 。

2.2 .端口分配在基本配置模式中,端口 A 、 B 和 C 被分配到唯一的 Camera Link 驱动器 / 接收器对上;在中级配置模式中,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上;在完整配置模式中,端口 A 、 B 和 C 被分配到第一个驱动器 / 接收器对上,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上,端口 G 和 H 被分配到第三个驱动器 / 接收器对上(见图2 )。