VCS使用介绍

VCS仿真指南

VCS仿真指南1.安装和设置VCS2.创建仿真环境- 源文件:将被测设计的源代码保存为以“.v”或“.sv”为扩展名的文件。

可以使用Verilog或SystemVerilog进行描述。

- 测试文件:编写一些测试文件来测试被测设计的功能。

可以使用Verilog或SystemVerilog进行编写,并将其保存为以“.v”或“.sv”为扩展名的文件。

```-vcs -debug_all -R +vcs+lic+wait```3.编译和仿真一旦仿真环境创建好了,就可以开始进行编译和仿真了。

首先,使用VCS的编译器将源文件和测试文件编译成一个可执行文件。

可以使用以下命令进行编译:```vcs -f <source_file_list> <test_file_list> -o <output_file> ```其中,`<source_file_list>`和`<test_file_list>`分别是包含被测设计和测试文件路径的文本文件,`<output_file>`是编译后生成的可执行文件的名称。

编译成功后,可以使用以下命令运行仿真:```./<output_file> -l <log_file> -gui```其中,`<log_file>`是仿真日志文件的名称。

4.调试仿真在进行仿真时,可能会遇到很多问题,如设计错误、仿真停滞等。

为了解决这些问题,可以使用VCS提供的一些调试工具和功能。

- Dump Variables:在仿真过程中,可以使用`+dumpvars`命令行选项来跟踪和显示特定的变量值。

例如,输入以下命令:```./<output_file> -l <log_file> +dumpvars=<variable_name>```这将在仿真日志中显示`<variable_name>`的值。

版本控制系统的作用与使用

版本控制系统的作用与使用版本控制系统(Version Control System,简称VCS)是软件开发中用于管理和跟踪文件变化的工具。

它可以帮助团队协作开发,追踪代码变更历史,恢复历史版本,并提供分支管理和合并的功能。

简单来说,版本控制系统就是一个记录文件变化的数据库。

它能够追踪文件的每一个版本,包括创建时间、修改时间、贡献者等等。

在软件开发中,版本控制系统被广泛应用于代码管理。

版本控制系统有两种类型:集中式版本控制系统(Centralized Version Control System,简称CVCS)和分布式版本控制系统(Distributed Version Control System,简称DVCS)。

CVCS是较早的版本控制系统,常见的代表是Subversion(SVN)。

它的设计思路是将文件集中存放在一个服务器上,开发者通过检出(Checkout)和提交(Commit)操作与服务器进行交互。

CVCS存在的问题是依赖于一个中央服务器,如果服务器宕机或者网络中断,开发者无法进行版本控制。

而DVCS是一种去中心化的版本控制系统,常见的代表是Git和Mercurial。

每个开发者都有完整的代码仓库,可以在本地进行版本控制操作,仅在需要时与其他开发者同步。

这种设计理念使得开发者在断网环境下仍可进行版本控制,并且可以方便地进行分支管理和合并操作。

下面我将详细介绍版本控制系统的作用和使用。

一、版本控制系统的作用1.追踪代码变化:版本控制系统能够记录每一次代码修改的详细信息,包括修改内容、修改时间、修改人等。

这样开发者可以清楚地了解代码的演变历史,便于排查问题和理解代码的发展。

2.多人协作开发:在团队协作开发中,多个开发者可以通过版本控制系统共享代码,并在发生冲突时进行解决。

系统记录了每个人的修改历史,完善了代码的协作开发流程。

3.回溯历史版本:在开发过程中,可能需要回退到之前的某一个版本,版本控制系统可以方便地实现回滚操作。

vcs用户手册

vcs用户手册一、概述本手册旨在为使用VCS(VersionControlSystem,版本控制系统)的用户提供全面的指南,帮助用户了解VCS的基本概念、功能和使用方法。

本手册适用于各种使用场景,包括软件开发、项目管理、文档管理等领域。

二、VCS基本概念VCS是一种用于跟踪和管理代码、文档、配置文件等版本信息的工具。

它可以帮助用户有效地管理多个版本的相同文件,并记录文件的变化历史。

通过VCS,用户可以轻松地回滚到以前的版本,比较不同版本的差异,以及协作开发。

三、VCS功能和使用方法1.安装和配置:介绍如何安装和配置VCS,包括选择合适的版本控制系统(如Git、SVN等)以及设置本地环境。

2.初始化仓库:介绍如何创建一个新的VCS仓库,并设置仓库的基本结构和权限。

3.添加文件:介绍如何将文件添加到VCS仓库中,包括添加单个文件和添加整个目录。

4.提交变更:介绍如何提交对文件的变更,包括添加注释和描述变更内容。

5.版本控制:介绍如何管理文件的版本,包括创建分支、合并分支、回滚变更等操作。

6.协作开发:介绍如何与他人协同开发,包括协同编辑文件、跟踪冲突等操作。

7.工具和插件:介绍常用的VCS工具和插件,以及如何使用它们提高效率。

8.安全性和最佳实践:强调在VCS使用中的安全性和最佳实践,包括隐私保护、备份数据、遵循版本控制规则等。

四、示例和操作指南提供一些实际操作示例,帮助用户更好地理解和掌握VCS的使用方法。

例如:1.如何使用Git进行版本控制,包括创建仓库、添加文件、提交变更、管理版本等操作。

2.如何与他人协同开发,包括协同编辑文件、解决冲突等操作。

3.如何使用Git的分支和合并功能,以及如何查看变更历史等。

五、常见问题和故障排除列举在使用VCS过程中可能遇到的问题和解决方法,例如:1.无法连接到远程仓库怎么办?2.提交变更时出现冲突如何解决?3.如何恢复到以前的版本?4.如何避免VCS的使用误区?六、附录和资源推荐提供一些有用的附录和资源推荐,包括:1.VCS的常见问题和故障排除技巧。

vcs使用手册

vcs使用手册版本控制系统(Version Control System,简称VCS)是软件开发中非常重要的工具,用于管理和跟踪代码的版本和变更。

本手册将介绍VCS的基本概念、常用命令和最佳实践,以帮助开发人员更好地使用版本控制系统。

一、基本概念1. 仓库(Repository)仓库是VCS存储代码的地方,包括所有版本的代码和历史记录。

2. 分支(Branch)分支是仓库中的一个独立的代码副本,用于开展不同的开发工作,例如新功能开发、修复bug等。

3. 提交(Commit)提交是对代码进行的修改操作,每次提交都会记录代码的状态和变更信息。

4. 标签(Tag)标签是用于标记特定版本的标识符,通常用于发布版本。

二、常用命令1. 初始化仓库:`git init`2. 添加文件到仓库:`git add <file>`3. 提交变更:`git commit -m "commit message"`4. 查看提交历史:`git log`5. 切换分支:`git checkout <branch>`6. 创建分支:`git branch <branch>`7. 合并分支:`git merge <branch>`8. 标签管理:`git tag <tag>`9. 查看标签:`git tag`10. 推送分支到远程仓库:`git push origin <branch>`11. 拉取远程仓库的分支:`git pull origin <branch>`三、最佳实践1. 遵循简洁的提交信息:在提交信息中简要描述变更内容,方便日后查看和理解。

2. 分支管理规范:合理使用分支,避免在主分支上进行日常开发,及时合并分支。

3. 定期推送和拉取代码:保持本地仓库与远程仓库同步,避免出现冲突。

4. 使用标签管理版本:为每个发布版本打上标签,方便回溯和发布。

VCS双机软件使用与维护

VCS双机软件使用与维护

其次,在安装和配置VCS双机软件时,我们需要针对具体的业务需求

进行设置。

例如,我们可以根据客户所在地区的语言和时区来设置软件的

界面语言和时间显示方式。

此外,还可以设置自动回复、排队系统等功能,以提升客户支持的效率和质量。

另外,为了确保VCS双机软件的正常运行,我们需要定期对软件进行

更新和升级。

软件的开发商通常会不断优化和改进软件的功能,以提升用

户体验和安全性。

因此,我们需要定期查看软件的更新信息,并按照指引

进行更新和升级操作。

此外,在进行更新和升级操作之前,务必要备份所

有的数据和配置文件,以避免意外丢失。

另外,为了保证VCS双机软件的安全性,我们需要定期检查和维护服

务器和软件的安全性。

这包括定期更改管理员密码、限制用户访问权限、

配置防火墙等。

此外,还需要定期检查软件日志,以发现和解决潜在的安

全问题。

综上所述,VCS双机软件的使用和维护是一个综合性的工作,需要对

硬件设备、网络连接、软件配置、安全性和人员培训等方面进行全面考虑

和管理。

只有合理使用和维护VCS双机软件,才能够实现高效的客户支持

和卓越的用户体验。

vcs使用——精选推荐

vcs使⽤(⼀)编译$vcs file_name 加各种开关选项1.基本选项-Mupdate :增量编译再次编译时只编译改变的⽂件-R :编译后继续进⾏仿真-gui :打开DVE图形界⾯-l<filename>:set log file name,⽤于写编译信息⽣成log⽂件⼀般在仿真⼤型⽂件时⽤到-sverilog :⽀持system verilog 语⾔+v2k :⽀持verilog语⾔2.⼯艺库相关选项-v lib_file :RTL代码⾥涉及到这个⼯艺库-y dir_file :告诉vcs去哪⾥找这个⼯艺库⼯艺库的路径+libext+lib_ext :当⽤到很多库,代替-v+incdir+inc_dir :代码⾥如果有include,使⽤这个命令告诉vcs包含⽂件的位置。

verilog代码⾥⾯写`include "filename.vh" 3.⽂件可选项-f file :有很多⽂件时把多个⽂件整合到这⼀个⽂件夹中4.修改⽂件名-o foo :修改可执⾏⽂件的名字⽂件原名为simv⽂件5.define 定义⼀个宏+define +<macro_name>=<value> :macro_name 宏名;value 初始化值;如+define+INCR_COUNTER(⼆)仿真$simv 加⼀些仿真开关选项./sim -gui &(./指在当前⽂件,sim指编译得到的可执⾏⽂件,gui指打开vcs的gui界⾯-dve,&指后台执⾏)将会得到执⾏的PID值 -s 结束仿真时间$plusargs()动态接收参数-E echo-l logfile 把仿真信息写⼊logfile⽂件⾥(三)VCS Debug的三种⽅法1.系统任务法 system task calls $display 打印变量赋值前值 $montor 打印变量赋值后值,变量值改变,打印值也变 $time 仿真时间 $readmemb 将⽂件⾥的内容读⼊存储器中,读⼆进制binary $readmemh 将⽂件⾥的内容读⼊存储器中,读⼗六进制hexadmecimal2.UCLI命令⾏法$vcs filename +v2k -ucli -R 3.VCS DVE。

VCS仿真指南

VCS仿真指南

VCS(Verification Continuity Simulator)是一款由Synopsys开发的仿真工具,用于验证硬件设计的正确性。

本指南旨在帮助初学者快速上手VCS仿真工具,完成硬件设计的验证工作。

本指南为第二版,对于第一版中的错误和不足之处进行了修正和补充。

一、VCS概述

1.什么是VCS?

VCS是一款基于Verilog和SystemVerilog硬件描述语言的仿真器,用于验证硬件设计的正确性。

VCS提供了高性能的仿真引擎和全面的仿真调试功能。

2.安装VCS

请参考VCS官方的安装指导手册进行安装,确保安装正确。

3.编写测试代码

使用Verilog或SystemVerilog语言编写测试代码,设计测试用例来验证硬件模块的功能。

可以使用assert语句来检查设计是否满足预期行为。

二、编译和仿真流程

1.编译测试代码

使用vcs命令将测试代码编译成仿真可执行文件。

例如:

```

vcs -sverilog testbench.sv design.sv -o simv

```

其中,testbench.sv为测试代码,design.sv为设计代码,simv为编译后的仿真执行文件。

2.运行仿真

运行编译后的仿真可执行文件,启动仿真。

例如:

```

./simv

```

3.调试仿真

在仿真过程中,可以使用一些命令对仿真进行调试,例如:

```

finish - 结束仿真

restart - 重新开始仿真

```。

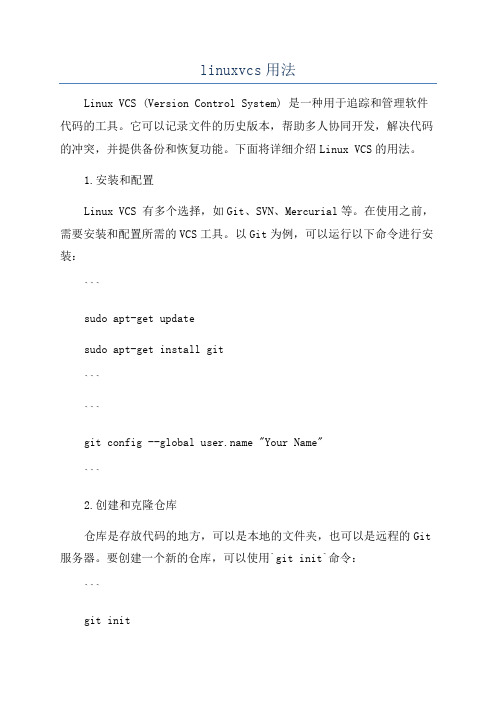

linuxvcs用法

linuxvcs用法Linux VCS (Version Control System) 是一种用于追踪和管理软件代码的工具。

它可以记录文件的历史版本,帮助多人协同开发,解决代码的冲突,并提供备份和恢复功能。

下面将详细介绍Linux VCS的用法。

1.安装和配置Linux VCS 有多个选择,如Git、SVN、Mercurial等。

在使用之前,需要安装和配置所需的VCS工具。

以Git为例,可以运行以下命令进行安装:```sudo apt-get updatesudo apt-get install git``````git config --global "Your Name"```2.创建和克隆仓库仓库是存放代码的地方,可以是本地的文件夹,也可以是远程的Git 服务器。

要创建一个新的仓库,可以使用`git init`命令:```git init```要克隆一个已存在的仓库,可以使用`git clone`命令,并提供仓库的URL:```git clone <repository_url>```3.添加和提交文件可以使用`git add`命令将文件添加到代码库中:```git add <file>`````````4.分支管理分支是可以同时进行多个任务和版本开发的实体。

可以使用`git branch`命令创建新分支:```git branch <branch_name>```可以使用`git checkout`命令切换到指定分支:```git checkout <branch_name>```还可以使用`git merge`命令将一个分支合并到另一个分支:```git merge <branch_name>```5.远程仓库操作可以使用`git remote`命令与远程仓库进行交互。

例如,可以使用`git remote add`命令添加远程仓库:```git remote add origin <repository_url>```可以使用`git push`命令将本地分支推送到远程仓库:```git push origin <branch_name>```可以使用`git pull`命令从远程仓库拉取最新的代码:```git pull origin <branch_name>```6.版本回滚如果需要回滚到先前的代码版本,可以使用`git log`命令查看提交记录,并找到要回滚的版本号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

J. M. Williams 2006-09-19

VCS Simulator Summary

Your startup environment includes this alias:

alias vcs='vcs -RI +charge_decay +memcbk +pathpulse +v2k' To remove this alias (you usually would not want to), invoke \vcs instead of vcs.

You must provide a valid verilog file name when you invoke VCS; if the file has a serious syntax error, VCS will exit immediately with an informative error message.

For one verilog file, invoke vcs filename

To invoke VCS on a design of several files, the names (with path if necessary) must be listed top-down in a file. Then, invoke VCS on the file (using -f):

vcs -f file_with_design_files_listed

Graphical UI hints (for Introductory Lab 1):

Immediately after invoking vcs -f Intro_Top.vcs

notice in the GUI that the current simulation time of 0 appears at the bottom of the

Interactive Window; it is in 100-ps units, as specified in TestBench.v. VCS always pauses at time 0. Also notice that the scope is TestBench, which contains the top of the design as a verilog module instance.

To run the Intro simulation,

1. Open a Hierarchy Browser window, using the menu bar along the top. On the left of the

new window, pick [+] to display the design hierarchy. If no [+] appears, pick [Sim] on the menu bar and [Rebuild & re-exec] to reestablish communication.

Note: We shall not be concerned with the Register Window or Logic Browser.

2. Use the top menu bar to open a Wave Window. Then, holding down the middle mouse button,

drag the text "TestBench" from the Hierarchy Browser window into the Wave Window.

The dragged image should turn color in the area where it is allowed to drop the text.

3. Pick [continue] or [=>] with the mouse. This runs the simulation. Notice that the time now is

5,540 x 100 ps = 554 ns.

4. View the simulation results. To zoom on the entire simulation waveform, in the Wave

Window, pick the small [z%] button and choose "100%" on the popup menu. You should see the initially unknown 'x' and 'z' states on the left, and the various top-level input and

output wave shapes as the simulation proceeded.

5. Reminder: If you change anything in a design, always run Rebuild & re-exec from the

Sim menu to compile and view your changes. Try this now.

6. After seeing that the simulation has run again, use the File/[Exit] menu choice to close all

VCS windows at once. Don't bother saving configuration when prompted.

Special hints (for labs after Lab 1):

When simulating a netlist using a verilog library file of numerous component models, it is useful to add "-v " before the library line in the .vcs file: VCS compiles only those models actually in the design. Use vcs -help to see all available VCS options.

On exitting the VCS GUI, if you save configuration to a some_name.cfg configuration file, you can program the VCS GUI to start with the saved window setup and waveform signals by adding

"+cfgfile+some_name.cfg" to your VCS command alias. "+cfgfile+default.cfg" works well.。