Verilog编写的3-8译码器电路代码

8-3编码器,3-8译码器的verilog实现

8-3编码器,3-8译码器的verilog实现在数字系统中,由于采⽤⼆进制运算处理数据,因此通常将信息变成若⼲位⼆进制代码。

在逻辑电路中,信号都是以⾼,低电平的形式输出。

编码器:实现编码的数字电路,把输⼊的每个⾼低电平信号编成⼀组对应的⼆进制代码。

设计⼀个输⼊为8个⾼电平有效信号,输出代码为原码输出的3位⼆进制编码器。

化简逻辑表达式:由逻辑表达式可以得出,普通的8-3编码器⽤或门即可实现。

对应的verilog程序如下:module mb_83(x,y);input [7:0]x;output [2:0]y;reg [2:0]y;always@(x)begincase (x)8'b00000001:y=3'b000; //当当 x=8 ’b00000001,则则 y 输出为 3 ’b0008'b00000010:y=3'b001; //当当 x=8 ’b00000010,则则 y 输出为 3 ’b0018'b00000100:y=3'b010; //当当 x=8 ’b00000100,则则 y 输出为 3 ’b0108'b00001000:y=3'b011; //当当 x=8 ’b00001000,则则 y 输出为 3 ’b0118'b00010000:y=3'b100; //当当 x=8 ’b00010000,则则 y 输出为 3 ’b1008'b00100000:y=3'b101; //当当 x=8 ’b00100000,则则 y 输出为 3 ’b1018'b01000000:y=3'b110; //当当 x=8 ’b01000000,则则 y 输出为 3 ’b1108'b10000000:y=3'b111; //当当 x=8 ’b10000000,则则 y 输出为 3 ’b111default: y=3'b000;endcaseendendmodule上述编码器有⼀个缺点,即在某⼀个时刻只允许有⼀个有效的输⼊,⽽同时若⼜有两个或两个以上的输⼊信号要求编码,输出端⼀定会发⽣混乱,出现错误。

数字电路应用之Verilog HDL语言常用经典程序例题(Quartus II软件)

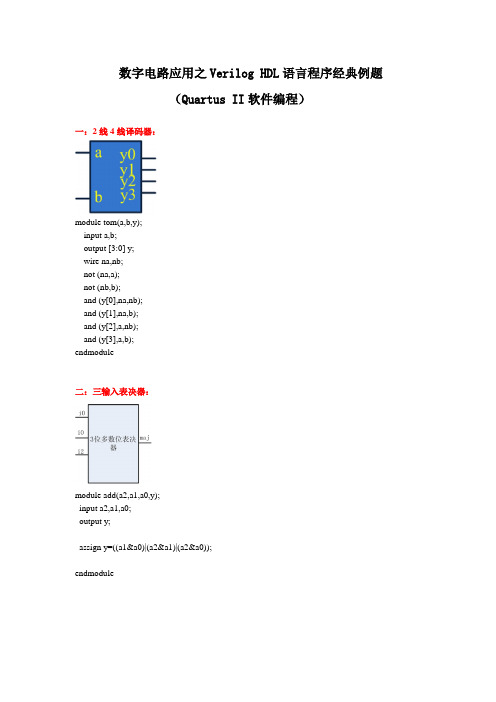

数字电路应用之Verilog HDL语言程序经典例题(Quartus II软件编程)一:2线4线译码器:module tom(a,b,y);input a,b;output [3:0] y;wire na,nb;not (na,a);not (nb,b);and (y[0],na,nb);and (y[1],na,b);and (y[2],a,nb);and (y[3],a,b);endmodule二:三输入表决器:module add(a2,a1,a0,y);input a2,a1,a0;output y;assign y=((a1&a0)|(a2&a1)|(a2&a0));endmodule三:3线8线译码器:module fulladd(a2,a1,a0,y);input a2,a1,a0;output [7:0] y;assign y[0]= ~( ~a2 & ~a1 & ~a0); assign y[1]= ~( ~a2 & ~a1 & a0); assign y[2]= ~( ~a2 & a1 & ~a0); assign y[3]= ~( ~a2 & a1 & a0); assign y[4]= ~( a2 & ~a1 & ~a0); assign y[5]= ~( a2 & ~a1 & a0); assign y[6]= ~( a2 & a1 & ~a0); assign y[7]= ~( a2 & a1 & a0);endmodule四:BIN2BCD码制转换:module fulladd(y,d,e);input [6:0] y;output [3:0] d,e;assign d=y/10;assign e=y%10;endmodule五:4位比较器:module tom(y,x,d);input [3:0] y,x;output [2:0] d;assign d[2]=(x>y)?1:0;assign d[1]=(x==y)?1:0;assign d[0]=(x<y)?1:0;endmodule六:四位全加器:法一:(调用程序法)module fulladd4(sum,c_in,c_out,a,b); output [3:0] sum;output c_out;input [3:0] a,b;input c_in;wire c1,c2,c3;fulladd fa0(sum[0],c1,a[0],b[0],c_in); fulladd fa1(sum[1],c2,a[1],b[1],c1); fulladd fa2(sum[2],c3,a[2],b[2],c2); fulladd fa3(sum[3],c_out,a[3],b[3],c3); endmodule//程序调用module fulladd(sum, c_out, a, b, c_in); output sum, c_out;input a, b, c_in;wire s1, c1, c2;xor (s1, a, b);and (c1, a, b);xor (sum, s1, c_in);and (c2, s1, c_in);xor (c_out, c2, c1);endmodule法二:(通用法)module fulladd4(A,B,Cin,SUM,Cout); input [3:0] A,B;input Cin;output [3:0] SUM;output Cout;assign {Cout,SUM}=A+B+Cin; endmodule七:七段显示译码器:法一:module bbc(a,d,g);input [3:0] a;output [6:0] d;output [3:0] g;reg [6:0] d;assign g=4'b0001;always @(a)begincase(a)4'b0000 :d=7'b100_0000;4'b0001 :d=7'b111_1001;4'b0010 :d=7'b010_0100;4'b0011 :d=7'b011_0000;4'b0100 :d=7'b001_1001;4'b0101 :d=7'b001_0010;4'b0110 :d=7'b000_0010;4'b0111 :d=7'b111_1000;4'b1000 :d=7'b000_0000;4'b1001 :d=7'b001_0000;default :d=7'b000_0000;endcaseendendmodule法二:module bbc(a,d,g);input [3:0] a;output [6:0] d;output [3:0] g;reg [6:0] d;assign g=4'b0001;always @(a)beginif (a==4'b0000) d=7'b100_0000;else if (a==4'b0001) d=7'b111_1001;else if (a==4'b0010) d=7'b010_0100;else if (a==4'b0011) d=7'b011_0000;else if (a==4'b0100) d=7'b001_1001;else if (a==4'b0101) d=7'b001_0010;else if (a==4'b0110) d=7'b000_0010;else if (a==4'b0111) d=7'b111_1000;else if (a==4'b1000) d=7'b000_0000;else if (a==4'b1001) d=7'b001_0000;else d=7'b000_0000; endendmodule八:8—3优先编码器:法一:module qq (y,d,g);input [7:0] y;output [2:0] d;output [3:0] g;reg [2:0] d;assign g=4'b0001;always @ ybeginif (y[7]==1) d=3'b111;else if (y[6]==1) d=3'b110;else if (y[5]==1) d=3'b101;else if (y[4]==1) d=3'b100;else if (y[3]==1) d=3'b011;else if (y[2]==1) d=3'b010;else if (y[1]==1) d=3'b001;else if (y[0]==1) d=3'b000;endendmodule法二:module encoder(none_on,outcode,a, b, c, d, e, f, g, h); output[2:0] outcode;output none_on;input a, b, c, d, e, f, g, h;reg[3:0] outtemp;assign {none_on, outcode} = outtemp;always @(a or b or c or d or e or f or g or h)begincasex ({a, b, c, d, e, f, g, h})8'B????_???1 : outtemp=4'b0_111;8'B????_??10 : outtemp=4'b0_110;8'B????_?100 : outtemp=4'b0_101;8'B????_1000 : outtemp=4'b0_100;8'B???1_0000 : outtemp=4'b0_011;8'B??10_0000 : outtemp=4'b0_010;8'B?100_0000 : outtemp=4'b0_001;8'B1000_0000 : outtemp=4'b0_000;8'B0000_0000 : outtemp=4'b1_000;endcaseendendmodule九:计数器:module bbc(clk,set,reset,d,y);input set,reset,clk;input [3:0] d;output [7:0] y;reg [7:0] y;always@(posedge clk or negedge reset or posedge set) if(~reset) y<=8'b0;else if (set) y[3:0]<=d[3:0];else y<=y+1'b1;endmodule十:移位寄存器:module asd (clk,set,reset,d,y,cin);input clk,set,reset,cin;input [3:0] d;output [7:0] y;reg [7:0] y;always@(posedge clk)beginif(~reset) y=0;else if(set)beginy[7:4]=y[3:0] ;y[3:0]=d[3:0];endelsebeginy=y<<1;y[0]=cin;endendendmodule十一:4位乘法:法一:module bbc(y,a,b);input [3:0] a;input [3:0] b;output [7:0] y;reg [7:0] y;reg[7:0] temp_a;reg[3:0] temp_b;integer i;always @(a or b)beginy=0;temp_a=a;temp_b=b;beginfor(i=0;i<=3;i=i+1)beginif(temp_b[0]) y=y+temp_a;temp_a=temp_a<<1;temp_b=temp_b>>1;endendendendmodule法二:module qq(outcome,a,b);output [8:1] outcome;input [4:1] a,b;reg [8:1] outcome;integer i;always@(a or b)beginoutcome=0;for(i=1;i<=4;i=i+1)if (b[1]) outcome=outcome + (a<<(i-1)); endendmodule十二:数码管跑马灯:module asd(cr,clk,a,b,c,d,e,f,g);input cr,clk;output a,b,c,d,e,f,g;reg a,b,c,d,e,f,g;integer i=0;always @ (posedge clk or negedge cr)beginif(~cr)begin{a,b,c,d,e,f,g}=7'b111_1111;i=0;endelse if(clk)begini=i+1;if(i==1) {a,b,c,d,e,f,g}=7'b011_1111;if(i==2) {a,b,c,d,e,f,g}=7'b101_1111;if(i==3) {a,b,c,d,e,f,g}=7'b110_1111;if(i==4) {a,b,c,d,e,f,g}=7'b111_0111;if(i==5) {a,b,c,d,e,f,g}=7'b111_1011;if(i==6) {a,b,c,d,e,f,g}=7'b111_1101;if(i==7) {a,b,c,d,e,f,g}=7'b111_1110;if(i==8) {a,b,c,d,e,f,g}=7'b000_0000;if(i==9)begin{a,b,c,d,e,f,g}=7'b111_1111;i=0;endendendendmodule十三:LED跑马灯:module add(cr,clk,y);input cr,clk;output [7:0] y;reg [7:0] y;integer i;always@(posedge clk or negedge cr) beginif(~cr)beginy=0;i=-1;endelse if (clk)begini=i+1;y=0;y[i]=1;beginif(i==7)i=-1;endendendendmodule。

3-8译码器代码

END IF;

END PROCESS;

END rtl;

七段显示

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

BEGIN

IF(g1='1' AND g2b='0' AND g2a='0')THEN

CASE INDATA IS

WHEN"000"=>Y<="11111110";

WHEN"001"=>Y<="11111101";

ENTITY decled1 IS

PORT(AIN:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

DOUT:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END DECLED1;

ARCHITECTURE BEHAV OF DECLED1 IS

WHEN"0111"=>DOUT<="0000111";

WHEN"1000"=>DOUT<="1111111";

WHEN"1001"=>DOUT<="1101111";

WHEN"1010"=>DOUT<="1110111";

WHEN"1111"=>DOUT<="1110001";

verilog实现输入三个8bit数,输出三个数据的中间数据。注意考虑资源优化的方式。 -回复

verilog实现输入三个8bit数,输出三个数据的中间数据。

注意考虑资源优化的方式。

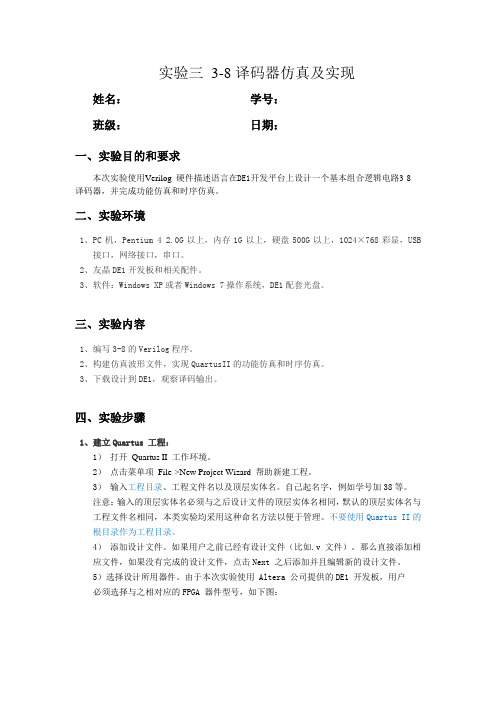

-回复题目要求我们使用Verilog实现输入三个8位数,输出这三个数的中间数据,并且需要考虑资源优化的方式。

在本文中,我们将从以下几个方面进行讨论和实现:1. Verilog语言概述:我们将简要介绍Verilog语言的基本结构和特点,为后续的具体实现做好铺垫。

2. 输入三个8位数:通过使用Verilog的输入输出端口,我们可以实现将三个8位数作为输入写入Verilog代码中。

3. 输出中间数据:我们将介绍如何通过Verilog的内部变量来计算并输出三个8位数的中间数据。

具体实现的方式取决于我们对中间数据的定义和计算公式。

4. 资源优化:通过使用Verilog中的一些优化技术,如信号复用、指定可优化的结构以及使用FPGA资源分配得当等,我们可以在实现这个功能的同时尽量减少硬件资源的使用。

现在,让我们逐步回答这些问题。

1. Verilog语言概述Verilog是一种硬件描述语言(HDL),用于描述和模拟数字电路。

它是一种行为级(Behavioral)语言,并使用了逻辑门的概念来描述电路的功能和行为。

Verilog具有高度的可移植性和可扩展性,因此被广泛应用于数字电路设计和验证。

2. 输入三个8位数在Verilog中,我们可以通过使用input关键字定义输入端口,并指定位宽来实现输入三个8位数的功能。

具体的代码示例如下:verilogmodule input_module(input [7:0] num1,input [7:0] num2,input [7:0] num3);在上面的代码中,我们使用[num:low]的形式来定义位宽为8的输入端口num1、num2和num3。

3. 输出中间数据为了输出三个数的中间数据,在Verilog中,我们可以使用reg或wire 关键字定义内部变量,并使用assign关键字将这些变量与输出端口相连。

实验三 3-8译码器仿真及实现

实验三3-8译码器仿真及实现一、实验目的和要求本次实验使用Verilog 硬件描述语言在DE1开发平台上设计一个基本组合逻辑电路3-8 译码器,并完成功能仿真和时序仿真。

二、实验环境1、PC机,Pentium 4 2.0G以上,内存1G以上,硬盘500G以上,1024×768彩显,USB接口,网络接口,串口。

2、友晶DE1开发板和相关配件。

3、软件:Windows XP或者Windows 7操作系统,DE1配套光盘。

三、实验内容1、编写3-8的Verilog程序。

2、构建仿真波形文件,实现QuartusII的功能仿真和时序仿真。

3、下载设计到DE1,观察译码输出。

四、实验步骤1、建立Quartus 工程:1)打开Quartus II 工作环境。

2)点击菜单项File->New Project Wizard 帮助新建工程。

3)输入工程目录、工程文件名以及顶层实体名。

自己起名字,例如学号加38等。

注意:输入的顶层实体名必须与之后设计文件的顶层实体名相同,默认的顶层实体名与工程文件名相同,本类实验均采用这种命名方法以便于管理。

不要使用Quartus II的根目录作为工程目录。

4)添加设计文件。

如果用户之前已经有设计文件(比如.v 文件)。

那么直接添加相应文件,如果没有完成的设计文件,点击Next 之后添加并且编辑新的设计文件。

5)选择设计所用器件。

由于本次实验使用 Altera 公司提供的DE1 开发板,用户必须选择与之相对应的FPGA 器件型号,如下图:6)设置 EDA 工具。

设计中可能会用到的EDA 工具有综合工具、仿真工具以及时序分析工具。

本次实验中不使用这些工具,因此点击Next 直接跳过设置。

7)查看新建工程总结。

在基本设计完成后,Quartus II 会自动生成一个总结让用户核对之前的设计,确认后点击Finish 完成新建。

8)培养良好的文件布局。

Quartus II 默认把所有编译结果放在工程的根目录,为了让Quartus II 像Visual Studio 等IDE 一样把编译结果放在一个单独的目录中,需要指定编译结果输出路径。

实验三+3-8译码器仿真及实现

实验三3-8译码器仿真及实现姓名:学号:班级:日期:一、实验目的和要求本次实验使用Verilog 硬件描述语言在DE1开发平台上设计一个基本组合逻辑电路3-8 译码器,并完成功能仿真和时序仿真。

二、实验环境1、PC机,Pentium 4 2.0G以上,内存1G以上,硬盘500G以上,1024×768彩显,USB接口,网络接口,串口。

2、友晶DE1开发板和相关配件。

3、软件:Windows XP或者Windows 7操作系统,DE1配套光盘。

三、实验内容1、编写3-8的Verilog程序。

2、构建仿真波形文件,实现QuartusII的功能仿真和时序仿真。

3、下载设计到DE1,观察译码输出。

四、实验步骤1、建立Quartus 工程:1)打开Quartus II 工作环境。

2)点击菜单项File->New Project Wizard 帮助新建工程。

3)输入工程目录、工程文件名以及顶层实体名。

自己起名字,例如学号加38等。

注意:输入的顶层实体名必须与之后设计文件的顶层实体名相同,默认的顶层实体名与工程文件名相同,本类实验均采用这种命名方法以便于管理。

不要使用Quartus II的根目录作为工程目录。

4)添加设计文件。

如果用户之前已经有设计文件(比如.v 文件)。

那么直接添加相应文件,如果没有完成的设计文件,点击Next 之后添加并且编辑新的设计文件。

5)选择设计所用器件。

由于本次实验使用 Altera 公司提供的DE1 开发板,用户必须选择与之相对应的FPGA 器件型号,如下图:6)设置 EDA 工具。

设计中可能会用到的EDA 工具有综合工具、仿真工具以及时序分析工具。

本次实验中不使用这些工具,因此点击Next 直接跳过设置。

7)查看新建工程总结。

在基本设计完成后,Quartus II 会自动生成一个总结让用户核对之前的设计,确认后点击Finish 完成新建。

8)培养良好的文件布局。

Quartus II 默认把所有编译结果放在工程的根目录,为了让Quartus II 像Visual Studio 等IDE 一样把编译结果放在一个单独的目录中,需要指定编译结果输出路径。

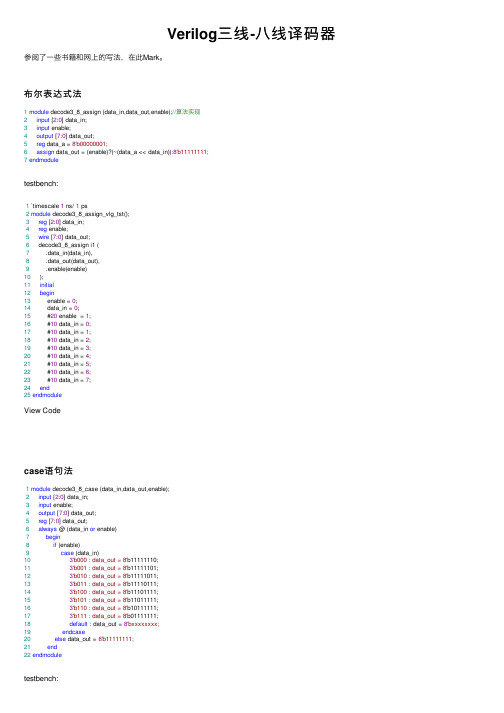

Verilog三线-八线译码器

11

3'b001 : data_out = 8'b11111101;

12

3'b010 : data_out = 8'b11111011;

13

3'b011 : data_out = 8'b11110111;

14

3'b100 : data_out = 8'b11101111;

15

3'b101 : data_out = 8'b11011111;

2 input [2:0] data_in;

3 input enable;

4 output [7:0] data_out;

5 reg [7:0] data_out;

6 always @ (data_in or enable)

7

begin

8

if (enable)

9

case (data_in)

10

3'b000 : data_out = 8'b11111110;

如有错误还请指出如有侵权还请告知如需转载请注明出处

Verilog三线 -八线译码器

参阅了一些书籍和网上的写法,在此Mark。

布尔表达式法

1 module decode3_8_assign (data_in,data_out,enable);//算法实现 2 input [2:0] data_in; 3 input enable; 4 output [7:0] data_out; 5 reg data_a = 8'b00000001; 6 assign data_out = (enable)?(~(data_a << data_in)):8'b11111111; 7 endmodule

Verilog八线-三线优先编码器设计(74LS148)

Verilog⼋线-三线优先编码器设计(74LS148)if语句法1//8线-3线优先编码器设计(74LS148)2//3//EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO4//0 | 0 x x x x x x x | 0 0 0 0 15//0 | 1 0 x x x x x x | 0 0 1 0 16//0 | 1 1 0 x x x x x | 0 1 0 0 17//0 | 1 1 1 0 x x x x | 0 1 1 0 18//0 | 1 1 1 1 0 x x x | 1 0 0 0 19//0 | 1 1 1 1 1 0 x x | 1 0 1 0 110//0 | 1 1 1 1 1 1 0 x | 1 1 0 0 111//0 | 1 1 1 1 1 1 1 0 | 1 1 1 0 112//0 | 1 1 1 1 1 1 1 1 | 1 1 1 1 013//1 | x x x x x x x x | 1 1 1 1 1141516module encoder_83 (din, EI, GS, EO, dout);17input [7:0] din; //编码输⼊端data_in,低电平有效18input EI; //使能输⼊端EI(选通输⼊端),EI为 0 时芯⽚⼯作,即允许编码19output [2:0] dout; //编码输出端data_out20output GS; //⽚优先编码输出端,优先编码器⼯作⼯作状态标志GS,低电平有效21output EO; //使能输出端EO(选通输出端)22reg [2:0] dout;23reg GS, EO;24always @(din or EI)25if(EI) begin dout <= 3'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在⾼电平26else if (din[7] == 0) begin dout <= 3'b000; GS <= 0; EO <= 1; end27else if (din[6] == 0) begin dout <= 3'b001; GS <= 0; EO <= 1; end28else if (din[5] == 0) begin dout <= 3'b010; GS <= 0; EO <= 1; end29else if (din[4] == 0) begin dout <= 3'b011; GS <= 0; EO <= 1; end30else if (din[3] == 0) begin dout <= 3'b100; GS <= 0; EO <= 1; end31else if (din[2] == 0) begin dout <= 3'b101; GS <= 0; EO <= 1; end32else if (din[1] == 0) begin dout <= 3'b110; GS <= 0; EO <= 1; end33else if (din[0] == 0) begin dout <= 3'b111; GS <= 0; EO <= 1; end34else if (din == 8'b11111111) begin dout <= 3'b111; GS <= 1; EO <= 0; end//芯⽚⼯作,但⽆编码输⼊35else begin dout <= 3'b111; GS <= 1; EO <= 1; end //消除锁存器(latch)36endmodule3738//EI = 0 表⽰允许编码,否则所有输出端被封锁在⾼电平(控制芯⽚⼯作)39//EO = 0 表⽰电路⼯作,但⽆编码输⼊(⽤于级联)40//GS = 0 表⽰电路⼯作,且有编码输⼊(判断输⼊端是否有输⼊)testbench:1 `timescale 1 ps/ 1 ps2module encoder_83_vlg_tst();3reg EI;4reg [7:0] din;5wire EO;6wire GS;7wire [2:0] dout;8 encoder_83 i1 (.EI(EI), .EO(EO), .GS(GS), .din(din), .dout(dout));9initial10begin11 EI = 1;12 din = 8'b11111111;13 #10 EI = 0;14 #10 din = 8'b01010101;15 #10 din = 8'b10101010;16 #10 din = 8'b11010101;17 #10 din = 8'b11101010;18 #10 din = 8'b11110101;19 #10 din = 8'b11111010;20 #10 din = 8'b11111101;21 #10 din = 8'b11111110;22 #10 din = 8'b11111111;23end24endmoduleView Codecase语句法1//8线-3线优先编码器设计(74LS148)2//3//EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO4//0 | 0 x x x x x x x | 0 0 0 0 15//0 | 1 0 x x x x x x | 0 0 1 0 16//0 | 1 1 0 x x x x x | 0 1 0 0 17//0 | 1 1 1 0 x x x x | 0 1 1 0 18//0 | 1 1 1 1 0 x x x | 1 0 0 0 19//0 | 1 1 1 1 1 0 x x | 1 0 1 0 110//0 | 1 1 1 1 1 1 0 x | 1 1 0 0 111//0 | 1 1 1 1 1 1 1 0 | 1 1 1 0 112//0 | 1 1 1 1 1 1 1 1 | 1 1 1 1 013//1 | x x x x x x x x | 1 1 1 1 1141516module encoder_83_case (din, EI, GS, EO, dout);17input [7:0] din; //编码输⼊端data_in,低电平有效18input EI; //使能输⼊端EI(选通输⼊端),EI为 0 时芯⽚⼯作,即允许编码19output [2:0] dout; //编码输出端data_out20output GS; //⽚优先编码输出端,优先编码器⼯作⼯作状态标志GS,低电平有效21output EO; //使能输出端EO(选通输出端)22reg [2:0] dout;23reg GS, EO;24always @(din or EI)25if(EI)26begin dout <= 3'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在⾼电平27else28casez (din) //建议⽤casez语句,casez把z/?匹配成任意。