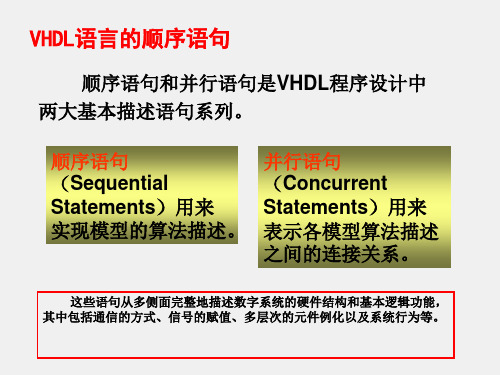

VHDL语言的主要描述语句

第19讲VHDL顺序描述语句

END rsff; ARCHITECTURE rtl OF rsff IS BEGIN

PROCESS(s,r) VARIABLE last_state :BIT;

BEGIN ASSERT(NOT(s =‘1’AND r =‘1’)) REPORT “Both s and r equal to‘1’.” SEVERITY ERROR; IF(s =‘0’AND r =‘0’)THEN last_state := last_state; ELSIF(s =‘0’AND r =‘1’)THEN last_state := 0; ELSE last_state := 1; END IF; q <= last_state; qb <= not(last_state);

q <= tmp2;

END PROCESS;

END rtl;

上例是一个取三个输入位矢量最大值的功能描述, 它在结构体中的进程语句中使用了两个过程调用语 句。

B. 函数调用语句

函数调用与过程调用是十分相似的,不同之处是, 调用函数将返还一个指定数据类型的值,函数的参 量只能是输入值。

函数语句分为两个部分,函数首和函数体。 (1)函数首的格式为: FUNCTION 函数名称(参数列表) RETURN 数据类型名; (2)函数体的格式为: FUNCTION 函数名称(参数列表) RETURN 数据类型名 IS

RETURN语句是一段子程序结束后,返回主程序的控制 语句。它只能用于函数与过程体内,并用来结束当前最内层 函数或过程体的执行。

RETURN语句的书写格式为:

RETURN; RETURN 表达式;

chap6VHDL语言的主要描述语句

qout<=d ;

--清零端无效,则时钟上升沿时输出为d

END IF;

〈EDA技术教程〉第6章

VHDL语言构造体的描述方法

3 CASE语句

CASE 语句常用来描写总线、编码或译码等功能,它可 以从不同语句中选择其中之一执行,与 IF 语句功能相似, CASE语句的可读性比if语句强。CASE语句的一般格式如下:

〈EDA技术教程〉第6章

VHDL语言构造体的描述方法

WHEN 13 => z2<='1' ; WHEN 4 To 72 => z3<='1'; WHEN OTHERS => z4<='1' ; END CASE ; END PROCESS ; END activ ;

-- 当sel为1或3时选中 -- 当sel为2、4、5、6或7时选中 -- 当sel为8~15中任一值时选中

【例2】 SIGNAL value : INTEGER RANGE 0 TO 15; SIGNAL out1 : STD_LOGIC ; ... CASE value IS -- 缺少以WHEN引导的条件句 END CASE; ... CASE value IS WHEN 0 => out1<= '1' ; -- value2~15的值未包括进去 WHEN 1 => out1<= '0' ; END CASE ... CASE value IS WHEN 0 TO 10 => out1<= '1'; -- 选择值中5~10的值有重叠 WHEN 5 TO 15 => out1<= '0'; END CASE;

第17讲VHDL主要描述语句case语句

END PROCESS;

END rtl;

练习:

用多选择结构实现如下问题: 1.求三个数中的最大数。 输入:整数a,b,c 输出:最大数max

2. Y= 1(X>0)

0 (X=0) -1 (X<0)

CASE语句

CASE语句根据满足的条件直接选择多项顺序语句中的一项执行。

CASE语句的结构为: CASE 表达式 IS WHEN 条件选择值 => 顺序语句, ┇

WHEN 条件选择值 => 顺序语句,

END CASE; 功能:先计算表达式的值,然后根据条件句中的选择值 执行相对应的顺序语句。 注意:条件句中的“=>”不是操作符,它相当于THEN作用。

其中WHEN条件选择值可以有四种表达方式;

① 单个普通数值,如:5; ② 数值选择范围,如:(1 TO 3); ③ 并列值,如:4 | 6,表示取值为4或6; ④ WHEN OTHERS => 顺序语句

例[A] PROCESS

BEGIN

y <= a AND b; WAIT ON a,b; END PROCESS; 例[B]PROCESS(a,b)

BEGIN

y <= a AND b; END PROCESS; 在例[A]中执行所有语句后,进程将在WAIT语句处被挂起,

直到a或b中任何一个信号发生变化,进程才重新开始。例 [A]与例[B]是等价的。

用二选一结构实现求两数中的较大数。 输入:整数a,b; 输出:较大数C

3.多选择控制语句

这种语句的书写格式为:

IF 条件 THEN 顺序语句 ELSIF 顺序语句

ELSIF

顺序语句 ┇ ELSE 顺序语句

END IF;

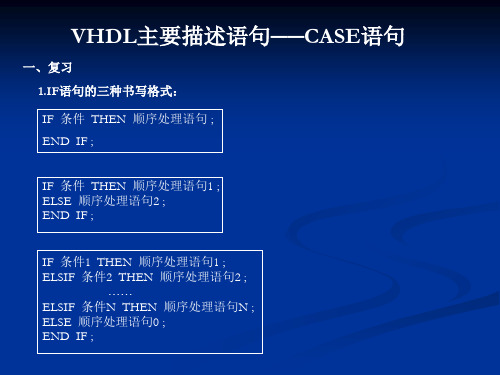

VHDL主要描述语句――CASE语句

使能端G 使能端

I0 I1 I2 I3

四 选 一 数 据 选 择 器

Q

公共通道

(同一时间内只可允许一个信号通过)

信 号 传 输 目 的 地

信号选择控制端AB 信号选择控制端

VHDL主要描述语句 主要描述语句――CASE语句 主要描述语句 语句

一、复习 1.IF语句的三种书写格式: 语句的三种书写格式: 语句的三种书写格式 IF 条件 THEN 顺序处理语句 ; END IF ;

IF 条件 THEN 顺序处理语句1 ; ELSE 顺序处理语句2 ; END IF ;

IF 条件1 THEN 顺序处理语句1 ; ELSIF 条件2 THEN 顺序处理语句2 ; …… ELSIF 条件N THEN 顺序处理语句N ; ELSE 顺序处理语句0 ; END IF ;

(同一时间内只可允许一个信号通过)

信 号 传 输 目 的 地

信号选择控制端AB 信号选择控制端

LIBRARY IEEE; USE IEEE.STD-LOGIC-1164.ALL; ENTITY 4SEL IS PORT ( I0,I1,I2,I3: IN STD-LOGIC ; , , , A,B:IN STD-LOGIC ; , : Q:OUT STD-LOGIC ) ; END 4SEL ; ARCHITECTURE A OF 4SEL IS SIGNAL D : STD-LOGIC-VECTOR(2 DOWNTO 0); D<=A & B ; PROCESS( D ) CASE D IS WHEN “00” => Q <= I0 ; WHEN “01” => Q <= I1 ; WHEN “10” => Q <= I2 ; WHEN “11” => Q <= I3 ; WHEN OTHER => NULL ; END CASE ; END A;

第五章(VHDL主要描述语句)

(4) CASE语句执行中必须选中,且只能选中所列条件语

句中一条。这表明CASE语句中至少要包含一个条件语句。

CASE语句常用来描写总线行为、编码器和译码器的结构。CASE语句 与IF语句功能相似但CASE语句的可读性好,非常简洁。

CASE语句的误用:

SIGNAL value : INTEGER RANGE 0 TO 15 ; SIGNAL out_1 : BIT ; CASE value IS -- 缺少 WHEN条件语句 END CASE ; -- 分支条件不包含2到15 CASE value IS WHEN 0 => out_1 <= „1‟; WHEN 1 => out_1 <=„0‟; END CASE ; -- 在5到10上发生重叠 CASE value IS WHEN 0 TO 10 => out_1 <= „1‟; WHEN 5 TO 15 => out_1 <= „0‟; END CASE ;

IF语句不仅可用于选择器设计,还可用于比较 器,译码器等进行条件控制的逻辑设计。IF语句 中至少应有一个条件句,条件句必须由布尔表达 式构成,条件表达式中能使用关系运算操作及逻 辑运算操作的组合表达式。 IF语句颠倒条件判别次序,会引起在综合时逻辑 功能的变化,即IF语句判别条件不可颠倒。 IF语句中,先处理最起始的条件;如果不满足, 再处理下一个条件。一般把条件约束最多的作为 起始条件。

例

用IF语句描述一个二位等值比较器

ARCHITECTURE a OF compare IS LIBRARY IEEE; BEGIN PROCESS(a,b) USE IEEE.STD_LOGIC_1164.ALL; BEGIN ENTITY compare IS IF(a>b) THEN eater<='1';equal<='0';less<='0'; generic(n:natural:=2); ELSIF (a=b) THEN PORT( greater<='0';equal<='1';less<='0'; ELSE a,b:IN STD_LOGIC_VECTOR(n-1 DOWNTO 0); greater<='0';equal<='0';less<='1'; greater,equal,less:OUT STD_LOGIC); END IF; END PROCESS; END; END;

硬件描述语言第七讲 VHDL语言的主要描述语句

举例:

P1:PROCESS(a) VARIABLE tmp: STD_LOGIC;

BEGIN tmp := '0' ;

WHEN 1 => q <= d1; WHEN 2 => q <= d2; WHEN 3 => q <= d3; END CASE;

CASE语句使用说明

(1)选择值不可重复或重叠。 (2)当CASE语句的选择值无法覆盖所有

情况时,要用OTHERS指定未能列出的其 他所有情况的输出值。 (3)在进程中用CASE语句描述组合逻辑 电路时,务必覆盖所有的情况;否则综合 后将引入锁存器,违背设计初衷。

CASE语句与IF语句的比较:

IF语句是有序的,先处理最起始、最优先的条件, 后处理次优先的条件。

case语句是无序的,所有表达式值都并行处理。 case语句中的条件表达式的值必须举穷尽,又

不能重复。不能穷尽的条件表达式的值用 OTHERS表示。

带有WHEN OTHERS项的 CASE语句举例:

上述语句中满足以下条件中的一个或多个时,进程 将再次启动,继续执行WAIT 语句的后继语句。 (1)信号量nmi和interrupt任何一个有一次新的变化; (2)信号量nmi或interrupt任何一个取值为“真”; (3)该语句已等待5us。

超时等待

在设计的程序模块中,等待语句所等待的条 件,在实际执行时不能保证一定会碰到,为 了防止该等待语句进行无限期的等待状态, 等待语句通常要加一项超时等待项。

第10章VHDL基本语句

END LOOP L2; ...

11

11

10.1.4 LOOP语句

(2) FOR_LOOP语句,语法格式如下: [LOOP标号:] FOR 循环变量 IN 循环次数范围 顺序语句

LOOP

END LOOP [LOOP标号];

SIGNAL tmp :STD_LOGIC ;

BEGIN

奇校验就是看2进制数旳1旳个数为奇数

PROCESS(a)

就在校验位填0 偶数就填1 使1旳个数

BEGIN

变成奇数个. 偶校验相反 把1旳个数变

tmp <='0';

成偶数.

FOR n IN 0 TO 7 LOOP 然后传送数据,接受后在做相应旳奇偶

FOR后旳”循环变量”是一种临时变量,属LOOP语句旳局 部变量,不必事先定义. 这个变量只能作为赋值源,不能被赋值,它 由LOOP语句自动定义. 使用时应该注意,在LOOP语句范围内不 要再使用其他与此循环变量同名旳标识符.

“循环次数范围”要求LOOP语句中旳顺序语句被执行次数. 循环变量从范围初值开始,每执行完一次顺序增1,直至最大值.

第 10 章 VHDL基本语句

1

1

10.1 顺序语句

VHDL有6种基本顺序语句:赋值语句、流程控制语句、等待 语句、子程序调用语句、返回语句、空操作语句.

10.1.1 赋值语句

信号赋值语句

10.1.2 IF语句

10.1.3 CASE语句

变量赋值语句

多条件选择

值体现式旳 4种形式

单个一般数值,如6。

数值选择范围,如(2 TO 4)。

VHDL的主要描述语句

CASE语句。

使用CASE语句需注意以下几点:

· CASE语句中每一条语句的选择值只能出现一次,即不能有相同选择值 的条件语句出现。

· CASE 语句执行中必须选中,且只能选中所列条件语句中的一条,即 CASE语句至少包含一个条件语句。 · 除非所有条件语句中的选择值能完全覆盖CASE语句中表达式的取值, 否则最末一个条件语句中的选择必须用“OTHERS”表示,它代表已给 出的所有条件语句中未能列出的其他可能的取值。关键词OTHERS只能 出现一次,且只能作为最后一种条件取值。使用OTHERS是为了使条件 语句中的所有选择值能覆盖表达式的所有取值,以免综合过程中插入 不必要的锁存器。这一点对于定义为STD_LOGIC和STD_LOGIC_VECTOR 数据类型的值尤为重要,因为这些数据对象的取值除了1、0之外,还 可能出现输入高阻态Z,不定态X等取值。

&

减

并置

VHDL语言运算符号(二)

优先级顺序 操作符类型 操作符

+ 正负运算符 * 乘法运算符 负 乘法

功能

正

/

MOD REM ** ABS

除法

求模 取余 指数 取绝对值

NOT

取反

INDEX

数据类型及运算符

顺序语句

并行语句 其它语句

VHDL顺序语句

顺序语句是指完全按照程序中书写的顺序执行各语 句,并且在结构层次中前面的语句执行结果会直接影 响后面各语句的执行结果。顺序描述语句只能出现在 进程或子程序中,用来定义进程或子程序的算法。顺 序语句可以用来进行算术运算、逻辑运算、信号和变 量的赋值、子程序调用等,还可以进行条件控制和迭 代。 注意,这里的顺序是从仿真软件的运行和顺应VHDL语 法的编程逻辑思路而言的,其相应的硬件逻辑工作方 式未必如此。应该注意区分VHDL语言的软件行为与描 述综合后的硬件行为的差异。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

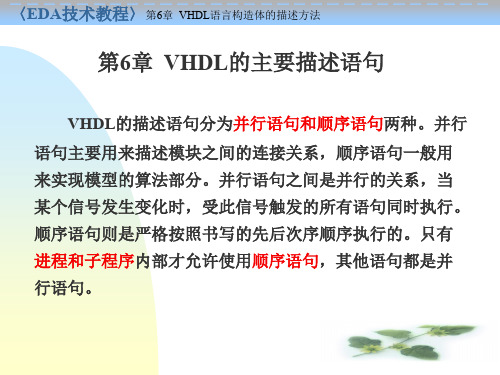

VHDL语言的主要描述语句按照语句的执行顺序对VHDL语言进行分类,包含两类语句:并行描述语句该语句的执行与书写顺序无关,总是同时被执行顺序描述语句从仿真的角度,该语句是顺序执行的进程语句(PROCESS)是最典型的并行语句,一个构造体内可以有几个进程语句同时存在,而且并发执行。

但是进程内部的所有语句都是顺序语句。

一、顺序描述语句顺序描述语句只能用在进程和子程序中,它和其他高级语言一样,其语句是按照语句的出现的顺序加以执行的。

如下分别介绍有关的顺序描述语句.1.WAIT语句进程在执行过程中总是处于两种状态:执行或挂起,进程的状态变化受等待语句的控制,当进程执行到等待语句,就被挂起,并等待再次执行进程.等待语句的格式:*WAIT 无限等待*WAIT ON 敏感信号变化*WAIT UNTIL 条件满足*WAIT FOR 时间到(1)WAIT ON格式:WAIT ON 信号[,信号]例5-1PROCESS(a,b)BEGINy<=a AND b;END PROCESS;该例中的进程与下例中进程相同:例5-1PROCESSBEGINy<=a AND b;WAIT ON a,b;END PROCESS;例5-2PROCESS(a,b)BEGINy<=a AND b;WAIT ON a,b;END PROCESS;(2)WAIT UNTIL 直到条件满足格式: WAIT UNTIL 布尔表达式当进程执行到该语句时,被挂起;若布尔表达式为真时,进程将被启动.例: WAIT UNTIL ((x*10)<100)(3)WAIT FOR等到时间到格式: WAIT FOR 时间表达式当进程执行到该语句时,被挂起;等待一定的时间后,进程将被启动.例: WAIT FOR 20 ns;WAIT FOR (a*(b+c);(4)多条件WAIT 语句例: WAIT ON nmi,interrupt UNTIL ((nmi=TRUE) OR (interrupt=TRUE)) FOR 5 us 该等待有三个条件:第一,信号nmi和interrupt 任何一个有一次刷新动作第二, 信号nmi和interrupt 任何一个为真第三, 已等待5 us只要一个以上的条件被满足,进程就被启动.*注意:多条件等待时,表达式的值至少应包含一个信号量的值。

(5) 超时等待例5-3例5-42.断言语句(ASSERT)(主要用于仿真、调试)格式: ASSERT 条件[REPORT 输出信息][SEVERITY 级别]执行到断言语句时,判断条件,若条件满足就继续执行,否则输出文字串和错误级别信息.例: ASSERT (tiaojian=’1’)REPORT “some thing wrong”SEVERITY ERROR;3.信号代入语句格式: 目的信号量<=信号量表达式例: a<=b;(注意区别小于等于)4.变量赋值语句格式: 目的变量:=表达式例: c:=a+d5.IF 语句三种书写格式:1) IF的门闩控制格式:IF 条件THEN顺序执行语句;END IF;例5-5IF (a=’1’) THENc<=b;END IF;例5-62)IF 语句的二选择控制格式:IF 条件THEN顺序执行语句;ELSE顺序执行语句;END IF;例5-7ARCHITECTURE rt1 OF mux2 ISBEGINPROCESS(a,b,sel)BEGINIF(sel=’1’) THENc<=a;ELSEc<=b;END IF;END PROCESS;END rt1;3)IF 语句的多选择控制格式:IF 条件THEN顺序执行语句ELSIF 条件THEN顺序执行语句::ELSIF 条件THEN顺序执行语句ELSIF 条件THEN顺序执行语句END IF;例如:5-8LIBRARY IEEE;USE ENTITY mux4 ISPORT(input :IN STD_LOGIC_VECTOR(3 DOWNTO 0);sel: IN STD_LOGIC_VECTOR(1 DOWNTO 0);q: OUT STD_LOGIC);END mux4;ARCHITECTURE rt1 OF mux4 ISBEGINnn: PROCESS(input,sel)BEGINIF (sel='00') THENq<=input(0);ELSIF (sel='01') THENq<=input(1);ELSIF (sel='10') THENq<=input(2);ELSEq<=input(3);ENDIF;END PROCESS nn;END rt1;注意:条件判断输出是布尔量。

6.CASE 语句常用来描述总线、编码和译码的行为。

格式:CASE 表达式ISWHEN 条件表达式=>顺序处理语句END CASE;其中WHEN的条件表达式可以有4种形式:WHEN 值=>顺序处理语句WHEN 值|值|值|…|值=>顺序处理语句WHEN 值TO 值=>顺序处理语句WHEN OTHERS=>顺序处理语句例:5-9LIBRARY IEEE;USE ENTITY mux43 ISPORT(a,b,i0,i1,i2,i3 :IN STD_LOGIC;q : OUT STD_LOGIC); END mux43;ARCHITECTURE mux4_behave OF mux43 ISSIGNAL sel: INTEGER RANGE 0 TO 3;BEGINnn: PROCESS(a,b,i0,i1,i2,i3)BEGINsel<=0;IF (a='1') THENsel<=sel+1;END IF;IF (b='1') THENEND IF;CASE sel ISWHEN 0 =>q<=i0;WHEN 1 =>q<=i1;WHEN 2 =>q<=i2;WHEN 3 =>q<=i3;END CASE;END PROCESS nn;END mux4_behave;例5-10 3-8译码器LIBRARY ieee;USE decoder38 isport(a,b,c,g1,g2a,g2b: in std_logic;y: out std_logic_vector(7 downto 0)); end decoder38;architecture behave38 OF decoder38 is signal indata: std_logic_vector(2 downto 0); beginindata<=c&b&a;process(indata,g1,g2a,g2b)beginif(g1='1' and g2a='0' and g2b='0') thenwhen "000"=>y<="11111110";when "001"=>y<="11111101";when "010"=>y<="11111011";when "011"=>y<="11110111";when "100"=>y<="11101111";when "101"=>y<="11011111";when "110"=>y<="10111111";when "111"=>y<="01111111";when others=>y<="XXXXXXXX";end case;elsey<="11111111";end if;end process;end behave38;例5-11LIBRARY ieee;USE encoder isport(input: in std_logic_vector(7 downto 0);y: out std_logic_vector(2 downto 0)); end encoder;architecture behave OF encoder isbeginprocess(input)begincase input iswhen”01111111” => y <= “111”;when”10111111” => y <= “110”;when”11011111” => y <= “101”;when”11101111” => y <= “100”;when”11110111” => y <= “011”;when”11111011” => y <= “010”;when”11111101” => y <= “001”;when”11111110” => y <= “000”;when others => y <= “xxx”;end case;end process;end behave;表5-1 优先级编码器的真值表例5-12LIBRARY ieee;USE prior isport( input: in std_logic_vector(7 downto 0);y: out std_logic_vector(2 downto 0)); end prior;architecture be_prior OF prior isbeginprocess(input)beginif(input(0)='0') theny<="111";elsif (input(1)='0') theny<="110";elsif (input(2)='0') theny<="101";elsif (input(3)='0') theny<="100";elsif (input(4)='0') theny<="011";elsif (input(5)='0') theny<="010";elsif (input(6)='0') theny<="001";elsey<="000";end if;end process;end be_prior;7. LOOP语句格式一:[标号]: FOR循环变量IN离散范围LOOP顺序处理语句;END LOOP [标号];例: ASUM: FOR i IN 1 TO 9 LOOPsum=1+sum;END LOOP ASUM;例5-13:8位奇偶校验电路LIBRARY IEEE;USE ENTITY pc ISPORT(a : IN STD_LOGIC_VECTOR(7 DOWNTO 0);y : OUT STD_LOGIC);END pc;ARCHITECTURE behave OF pc ISBEGINcbc: PROCESS(a)VARIABLE tmp: STD_LOGIC;BEGINtmp:='0';FOR i IN 0 TO 7 LOOPtmp:=tmp XOR a(i);END LOOP;y<=tmp;END PROCESS cbc;END behave;格式二:[标号]: WHILE 条件LOOP顺序处理语句;END LOOP [标号];在该语句中,如果条件为真,则进行循环,否则结束循环.例:I:=1;sum:=0abcd: WHILE (I<10) LOOPsum:=I+sum;I:=I+1;END LOOP abcd;例5-14:LIBRARY IEEE;USE ENTITY pc ISPORT(a : IN STD_LOGIC_VECTOR(7 DOWNTO 0);y : OUT STD_LOGIC);END pc;ARCHITECTURE behave OF pc ISBEGINcbc: PROCESS(a)VARIABLE tmp: STD_LOGIC;BEGINtmp:='0';i:=0;WHILE (i<8) LOOPtmp:=tmp XOR a(i);i=i+1;END LOOP;y<=tmp;END PROCESS cbc;END behave;8. NEXT语句在LOOP语句中用NEXT语句跳出循环.格式: NEXT [标号][WHEN 条件]; NEXT语句用于控制内循环的结束.例5-15:PROCESS (a,b)CONSTANT max_limit: INTEGER:=255 BEGINFOR I IN 0 TO max_limit LOOPIF (done(I)=TRUE) THENNEXT;ELSE done(I):=TRUE;END IF;q(I)<=a(I) AND b(I);END LOOP;END PROCESS;9. EXIT 语句EXIT语句用于结束LOOP循环状态.格式: EXIT [标号] [WHEN 条件]例5-16:PROCESS(a)VARIABLE int_a :INTEGER; BEGINint_a:=aFOR I=0 IN 0 TO max_limit LOOPIF (int_a<=0) THENEXIT;ELSEint_a:=int_a-1;q(I)<=REAL(a*I);END IFEND LOOP;y<=q;END PROCESS;二、并发描述语句1.进程语句在一个构造体中多个PROCESS语句可以同时并行的执行,该语句有如下特点:1)可以和其它进程语句同时执行,并可以存取构造体和实体中所定义的信号2)进程中的所有语句都按照顺序执行3)为启动进程,在进程中必须包含一个敏感信号表或WAIT语句4)进程之间的通信是通过信号量来实现的2.并发信号代入代入语句在进程中使用是顺序语句,但是在进程外即在构造体中使用就是并发语句,相当于一个进程.例:ARCHITECTURE behave OF a_var ISBEGINOutput<=a(I);END behave;可以等效于:ARCHITECTURE behave OF a_var ISBEGINss PROCESS(a,I)BEGINOutput<=a(I);END PROCESS ss;END behave;信号代入语句的右边可以是算数表达式,也可以是逻辑表达式,还可以是关系表达式,所以可以仿真加法器、乘法器、除法器、比较器和各种逻辑电路。