MOS模拟开关

mos开关电路原理图

mos开关电路原理图MOS开关电路原理图。

MOS开关电路是一种常用的电子电路,它具有高速开关和低功耗的特点,广泛应用于数字电路、模拟电路和功率电子领域。

本文将介绍MOS开关电路的原理图及其工作原理。

MOS开关电路由MOS管组成,MOS管是一种场效应晶体管,由金属氧化物半导体构成。

MOS管有N沟道型和P沟道型之分,分别用于NMOS和PMOS开关电路。

NMOS开关电路的原理图如下图所示:[图1,NMOS开关电路原理图]在NMOS开关电路中,当输入端施加高电平时,MOS管导通,输出端接地;当输入端施加低电平时,MOS管截止,输出端高阻。

PMOS开关电路的原理图如下图所示:[图2,PMOS开关电路原理图]在PMOS开关电路中,当输入端施加低电平时,MOS管导通,输出端接地;当输入端施加高电平时,MOS管截止,输出端高阻。

MOS开关电路的工作原理是基于MOS管的导通特性。

当MOS管的栅极施加一定电压时,形成电场,使得沟道导电。

通过控制栅极电压,可以实现MOS管的导通和截止,从而实现开关功能。

MOS开关电路具有高速开关和低功耗的特点,适用于数字信号处理、模拟信号开关和功率控制等领域。

在数字电路中,MOS开关电路可以实现逻辑门、触发器和寄存器等功能;在模拟电路中,MOS开关电路可以实现信号开关、模拟开关和运算放大器等功能;在功率电子领域,MOS开关电路可以实现电源开关、逆变器和变换器等功能。

总之,MOS开关电路是一种功能强大的电子电路,具有广泛的应用前景。

通过合理设计和优化,可以实现高性能、低功耗的电子系统。

希望本文对MOS开关电路的原理和应用有所帮助,谢谢阅读!。

基于CMOS模拟开关实现平衡混频器

c a c rt fo p we cnu t nadh d ge fierT e x r dx s r mesrdadaa zda teed T ett hr t i co w o r o smpi i ere a. h e i ee a a e n l e th n . h s a es i l o n 曲 ol n mi n e u n y e

P d o rso o ts bv 3B whntep we p  ̄ vlg . n urn o sm t nil s h 0 d lB cmpe i p i o e1d m e o r up ot eii 33 a dcr t nu p o s ta 1mA a s n n ia h s a sn V e c i s e n n

中 图分 类 号 :T 9 18 文 献 标识 码 : A 文 章 编 号 : 0 8 1 3 ( 0 2 1 — 0 3 N 1. 1 0 — 7 9 2 1 )5 7 -

De i n o l n e i e s d o sg fBa a c d M x r Ba e n CM OS An l g S t h a o wic

技 术 论 坛

7 0 计 算 机 与 网 络 创 新 生 活

基于 C MOS模拟开关 实现 平衡 混频器

王 迎栋 孙 明杰

( 中国电子科技 集 团公 司第五 十四研 究所 河 北 石 家庄 00 8) 50 1

【 要】 详 细介绍 了有源单平衡混频器的电路 组成 , 摘 分析 了有 源平衡混频器的工作原理。基于 C MOS模拟开关设 计实 现 了一种( 低功耗、 高线性度的) 关平衡 混频 器, 开 最后 对混频 器的指标进行 了测量和分析。 测试结果表 明( 3 在 . 3V电源电压下 ,

模拟开关和多路复用器基本知识

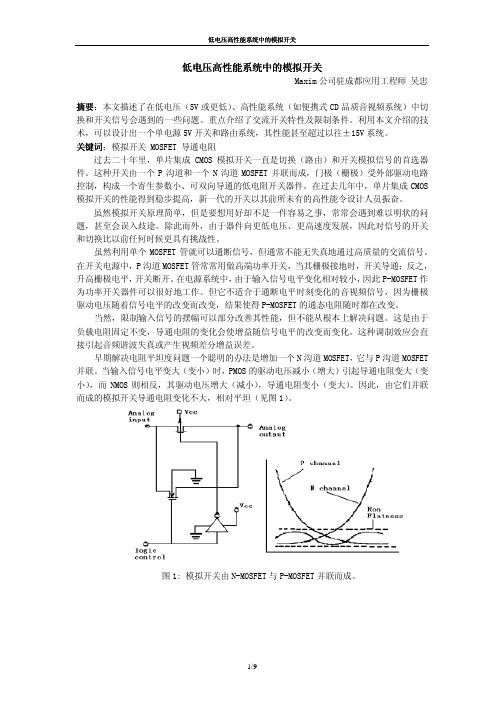

PMOS NMOSALTERNATE SYMBOLS图1:MOSFET开关导通电阻与信号电压之间的关系工艺(CMOS)可以产出优异的P沟道和N沟道MOSFET。

并联连接器件,结果会形成如图2所示的基本双向CMOS开关。

这种组合有利于减少导通电阻,同时也可能产生随信号电压变化小得多的电阻。

SWITCHDRIVERSWITCH图2:基础CMOS 开关用互补对来减少信号摆幅引起的R ON 变化COMBINED TRANSFERFUNCTION图3:CMOS 开关导通电阻与信号电压之间的关系展示的是N 型和P 型器件的导通电阻随通道电压的变化。

这种非线性电阻可能给直流精度和交流失真带来误差。

双向CMOS 开关可以解决这个问题。

导通电阻大幅降低,线性度也得到了提升。

图3底部曲线展示的是改进后的开关导通电阻特性的平坦度。

ADG8xx 系列CMOS 开关是专门针对导通电阻低于0.5 Ω的应用而设计的,采用亚微米工艺制成。

这些器件可以传导最高400 mA 的电流,采用1.8 V 至5.5 V 单电源供电(具体视器件而定),额定扩展工作温度范围为–40°C 至+125°C 。

典型的导通电阻与温度和输入信号电平之间的关系如图4所示。

图5:两个相邻CMOS开关的等效电路:影响导通开关条件下直流性能的因素:RON 、RLOADLeakage current creates error voltage at V OUT equal to: V OUT= I LKG×R LOAD图7:影响关断开关条件下直流性能的因素:ILKG 和R当开关断开时,漏电流可能引起误差,如图7所示。

流过负载电阻的漏电流会在输出端产生一个对应的电压误差。

图8:动态性能考虑:传输精度与频率的关系会在传递函数A(s)的分子中形成一个零点。

该零通常出现在高频下,因在等效电路中,CDS和负载电容的函数。

该频率极点为开关导通电阻很小。

常用模拟开关芯片型号与功能和应用介绍-PPT精选文档

注意:

AD7501,AD7502,AD7503 芯片都是单向多到

一的多路开关,即信号只允许从多个 (8个) 输入端向

一个输出端传送。

单八路模拟开关CD4051

• CD4051相当于一个单刀八掷开关,开关接通哪一通 道,由输入的3位地址码ABC来决定。

当选通E为 1 时,而输入端A为0时,则 S2 端为 1 , S1端为0,这时VT1截止,VT2导通,输出端B为0, A=B,也相当于输入端和输出端接通。 当选通端E为0时,这时VT1和VT2均为截止状 态,电路输出呈高阻状态。 从上面的分析可以看出,只有当选通端E为高电 平时,模拟开关才会被接通,此时可从A向B传送信 息;当输入端A为低电平时,模拟开关关闭,停止传 送信息。

AD 7501

14 13 12 11 10 9

... ...

S1 S8

图3.7 AD7501(AD7503)芯片结构及引脚功能

片上所有逻辑输入与TTL/DTL及CMOS 电路兼容。

表3.1 AD7501真值表

A2

0 0 0 0 1 1 1 1 ×

A1

0 0 1 1 0 0 1 1 ×

A0

0 1 0 1 0 1 0 1 ×

二、常用的CMOS模拟开关集成电路

在模拟开关的集成过程中,晶体三极管和场效应 晶体管均可用来做模拟开关的有源器件,实际上,由 于场效应晶体管特性的对称性不存在残余电压等优点, 所以在模拟开关中用的最多的还是场效应晶体管。 • 开关在电路中起接通信号或断开信号的作用。最常见的 可控开关是继电器,当给驱动继电器的驱动电路加高电 平或低电平时,继电器就吸合或释放,其触点接通或断 开电路。 • CMOS模拟开关是一种可控开关,它不象继电器那样可 以用在大电流、高电压场合,只适于处理幅度不超过其 工作电压、电流较小的模拟或数字信号。

模拟开关电路介绍

模拟开关是一种三稳态电路,它可以根据选通端的电平,决定输人端与输出端的状态。

当选通端处在选通状态时,输出端的状态取决于输人端的状态;当选通端处于截止状态时,则不管输人端电平如何,输出端都呈高阻状态。

模拟开关在电子设备中主要起接通信号或断开信号的作用。

由于模拟开关具有功耗低、速度快、无机械触点、体积小和使用寿命长等特点,因而,在自动控制系统和计算机中得到了广泛应用。

一、模拟开关的电路组成及工作原理模拟开关电路由两个或非门、两个场效应管及一个非门组成,如图一所示。

模拟开关的真值表见表一。

表一模拟开关的工作原理如下:当选通端E和输人端A同为1时,则S2端为0,S1端为1,这时VT1导通,VT2截止,输出端B输出为1,A=B,相当于输入端和输出端接通。

当选通E为0时,而输人端A为0时,则S2端为1,S1端为0,这时VT1截止,VT2导通,输出端B为0,A=B,也相当于输人端和输出端接通。

当选通端E为0时,这时VT1和VT2均为截止状态,电路输出呈高阻状态。

从上面的分析可以看出,只有当选通端E为高电平时,模拟开关才会被接通,此时可从A向B传送信息;当输人端A为低电平时,模拟开关关闭,停止传送信息。

二、常用的CMOS模拟开关集成电路根据电路的特性和集成度的不同,MOS模拟开关集成电路可分为很多种类。

现将常用的模拟开关集成电路的型号、名称及特性列入表二中。

表二常用的模拟开关三、CD4066模拟开关集成电路的应用举例CD4066是一种双向模拟开关,在集成电路内有4个独立的能控制数字及模拟信号传送的模拟开关。

每个开关有一个输人端和一个输出端,它们可以互换使用,还有一个选通端(又称控制端),当选通端为高电平时,开关导通;当选通端为低电平时,开关截止。

使用时选通端是不允许悬空的。

下面介绍CD4066模拟开关的两个应用实例。

1.采样信号保持电路采样信号保持电路如图二所示。

图二采样信号保持电路模拟信号Ui从运算放大器的同相输人端输人。

CMOS集成模拟开关的选用及工程设计中的一些问题

25 0

P CHAN NEL -

1 0 9 8

P CIAN  ̄EL - I J

I

20 0 10 5

Z

/

、

, 、

= V ;

7 6

5

a

j{ ,

0

l0 0

l

- _ - 一

、 / \

—

● } _

体 积小 和使用 寿命 长等特 点 。它 是按 时间分 割方式 在多 路输入 信号 中选通 1 到输 出端 的 路 器 件 。同时 ,由于 它具有双 向特性 ,可 将输 入 、输 出端互换 ,即将输 入端 信号 分配 到某一

输 出端 。所 以 N选 l 路模 拟 开关 ,也 可 以用作 l到 N 的多 路模 拟分 配 器 。多 路模 拟开 多 关分 为 2选 l 、4选 l 、8选 l 6选 l等 类 型 。它 们 的结 构 与 原理 相 似 , 是 路数 不 同 。 、l 只 作 为数 字与模 拟不 同信息 相互连 通 的接 口器件 。C S集 成模 拟开 关被 广泛 应用 在各 种 电 MO 子 系统 中。近 年来 ,C S集成模 拟开 关 已经提 供 了更好 的开关 特 性 ,更低 的供 电电压 和 MO 更 小 的封 装 形式 ,为用 户 提供 了更 好 的性 能 和更 多 的 功能 选择 。实 际使 用 C S集 成模 MO 拟 开关 时 ,应 根据具 体用途 做 出合 理选 择 ,并 依据 其 电特 性 ,增 设各 种保 护措施 ,合 理设

O八一 科技

CMoS 集成 模拟 开关 的选用 及工 程设计 中的一些 问题

2 7

是衡 量模 拟 开关性 能 的一 个重 要指 标 。模拟 开 关 的导通 电阻 R N 为两个 MO F T导 通 电 O SE 阻的并 联值 。

模拟开关使用指南-使用模拟开关必读

可推算出 Cfeed=0.07pF。因此两个系统中开关的 Cfeed 大致相等。所以,虽然音频信号比视频 信号的频率低得多,但是由于前者要求的隔离度比后者高得多,结果造成两个系统需要性能

相当的模拟开关。

现代高速系统需要宽带低电压模拟开关,因此要求ON 反比于栅源电压与门槛电压之差,低电压时 RON 自然会变大。 当然,增大 FETS 管芯面积可以减小 RON,但这却使寄生电容变大,因而,在许多场合,并不 会真正改善开关性能。

最终,我们决定采用如 MAX323 一类的高性能模拟开关。根据其 Cfeed=0.8pF, RLOAD=47K Ω,推导出隔离度=46dB,仍不理想,距要求还有一定距离。不过由于 MAX323 导通电阻平坦 度好,因而信号失真小,该项指标满足要求。

既然负载电阻也是影响开关隔离度的一个主要因素,那么设计者可能会想到采用运放缓 冲模拟开关信号,使开关驱动低阻负载。当模拟开关的负载电阻减小到 470Ω时,隔离度增 加 20dB。但采用运放后,产生了几个新问题。其一是,运放和低阻负载会消耗更多功率。2V 的信号在 100Ω的负载上就要消耗 20mA 电流,这还不包括运放自身消耗的功率。另一个更敏 感问题是,由于负载电阻大大减小,△RON 与负载电阻的比值增大许多,结果产生很大的谐波 失真,大约 10%,这样的开关真可谓低保真系统,产品自然不会有市场。

上式中:VISO=开关隔离度、f=信号频率、RLOAD =负载电阻、Cfeed=馈通电容

通常,产品数据表中不会直接列出 Cfeed 大小,而是给出在某一频率和负载条件下的隔离

度。因此需要通过下式推导 Cfeed:

C FEED

=

1

2π fR LOAD

V ISO

10 20

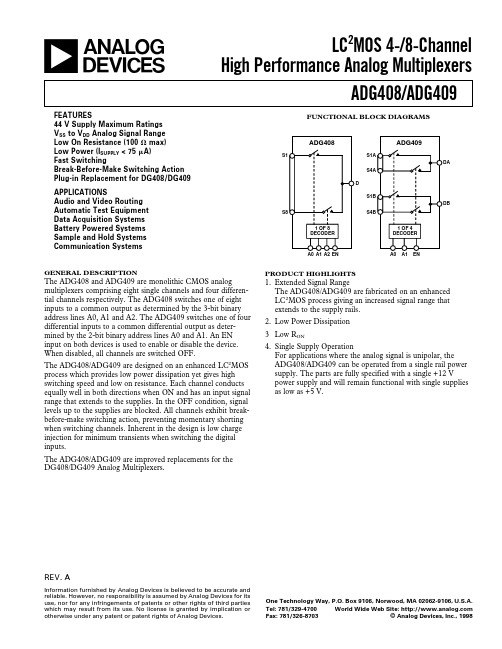

ADG408、409(模拟开关)

REV.AInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aLC 2MOS 4-/8-ChannelHigh Performance Analog MultiplexersADG408/ADG409FEATURES44 V Supply Maximum Ratings V SS to V DD Analog Signal Range Low On Resistance (100 ⍀ max)Low Power (I SUPPLY < 75 A)Fast SwitchingBreak-Before-Make Switching Action Plug-in Replacement for DG408/DG409APPLICATIONSAudio and Video Routing Automatic Test Equipment Data Acquisition Systems Battery Powered Systems Sample and Hold Systems Communication Systems GENERAL DESCRIPTIONThe ADG408 and ADG409 are monolithic CMOS analogmultiplexers comprising eight single channels and four differen-tial channels respectively. The ADG408 switches one of eight inputs to a common output as determined by the 3-bit binary address lines A0, A1 and A2. The ADG409 switches one of four differential inputs to a common differential output as deter-mined by the 2-bit binary address lines A0 and A1. An EN input on both devices is used to enable or disable the device.When disabled, all channels are switched OFF.The ADG408/ADG409 are designed on an enhanced LC 2MOS process which provides low power dissipation yet gives high switching speed and low on resistance. Each channel conducts equally well in both directions when ON and has an input signal range that extends to the supplies. In the OFF condition, signal levels up to the supplies are blocked. All channels exhibit break-before-make switching action, preventing momentary shorting when switching channels. Inherent in the design is low charge injection for minimum transients when switching the digital inputs.The ADG408/ADG409 are improved replacements for the DG408/DG409 Analog Multiplexers.PRODUCT HIGHLIGHTS1.Extended Signal RangeThe ADG408/ADG409 are fabricated on an enhanced LC 2MOS process giving an increased signal range that extends to the supply rails.2.Low Power Dissipation 3Low R ON4.Single Supply OperationFor applications where the analog signal is unipolar, the ADG408/ADG409 can be operated from a single rail power supply. The parts are fully specified with a single +12 V power supply and will remain functional with single supplies as low as +5 V.FUNCTIONAL BLOCK DIAGRAMSOne Technology Way, P.O. Box 9106, Norwood, MA 02062-9106,U.S.A.Tel: 781/329-4700World Wide Web Site: Fax: 781/326-8703© Analog Devices, Inc., 1998ADG408/ADG409–SPECIFICATIONSDUAL SUPPLY 1B VersionT Version–40؇C to–55؇C toParameter+25؇C +85؇C+25؇C +125؇CUnits Test Conditions/CommentsANALOG SWITCH Analog Signal Range V SS to V DD V SS to V DD VR ON 4040Ω typV D = ±10 V, I S = –10 mA 100125100125Ω max∆R ON1515Ω max V D = +10 V, –10 V LEAKAGE CURRENTSSource OFF Leakage I S (OFF)±0.5±50±0.5±50nA max V D = ±10 V, V S = ϯ10 V;Test Circuit 2Drain OFF Leakage I D (OFF)V D = ±10 V; V S = ϯ10 V;ADG408±1±100±1±100nA max Test Circuit 3ADG409±1±50±1±50nA max Channel ON Leakage I D , I S (ON)V S = V D = ±10 V;ADG408±1±100±1±100nA max Test Circuit 4ADG409±1±50±1±50nA max DIGITAL INPUTSInput High Voltage, V INH 2.4 2.4V min Input Low Voltage, V INL 0.80.8V max Input Current I INL or I INH±10±10µA max V IN = 0 or V DD C IN , Digital Input Capacitance 88pF typ f = 1 MHzDYNAMIC CHARACTERISTICS 2t TRANSITION 120120ns typ R L = 300 Ω, C L = 35 pF;250250ns max V S1 = ±10 V, V SS = ϯ10 V;Test Circuit 5t OPEN 10101010ns min R L = 300 Ω, C L = 35 pF;V S = +5 V; Test Circuit 6t ON (EN)8512585125ns typ R L = 300 Ω, C L = 35 pF;150225150225ns max V S = +5 V; Test Circuit 7t OFF (EN)6565ns typ R L = 300 Ω, C L = 35 pF;150150ns max V S = +5 V; Test Circuit 7Charge Injection 2020pC typ V S = 0 V, R S = 0 Ω, C L = 10 nF;Test Circuit 8OFF Isolation–75–75dB typ R L = 1 k Ω, f = 100 kHz;V EN = 0 V; Test Circuit 9Channel-to-Channel Crosstalk 8585dB typ R L = 1 k Ω, f = 100 kHz;Test Circuit 10C S (OFF)1111pF typ f = 1 MHz C D (OFF) f = 1 MHz ADG4084040pF typ ADG4092020pF typC D , C S (ON) f = 1 MHzADG4085454pF typ ADG4093434pF typPOWER REQUIREMENTS I DD 11µA typ V IN = 0 V, V EN = 0 V55µA max I SS 11µA typ 55µA max I DD100100µA typ V IN = 0 V, V EN = 2.4 V200500200500µA maxNOTES 1Temperature ranges are as follows: B Version: –40°C to +85°C; T Version: –55°C to +125°C.2Guaranteed by design, not subject to production test.Specifications subject to change without notice.REV. A–2–(V DD = +15 V, V SS = –15 V, GND = 0 V, unless otherwise noted)ADG408/ADG409 SINGLE SUPPLY1(V DD = +12 V, V SS = 0 V, GND = 0 V, unless otherwise noted)B Version T Version–40؇C to–55؇C toParameter+25؇C+85؇C+25؇C+125؇C Units Test Conditions/Comments ANALOG SWITCHAnalog Signal Range0 to V DD0 to V DD VR ON9090Ω typ V D = +3 V, +10 V, I S = –1 mA LEAKAGE CURRENTSSource OFF Leakage I S (OFF)±0.5±50±0.5±50nA max V D =8 V/0 V, V S = 0 V/8V;Test Circuit 2Drain OFF Leakage I D (OFF)V D =8 V/0 V, V S = 0 V/8V;ADG408±1±100±1±100nA max Test Circuit 3ADG409±1±50±1±50nA maxChannel ON Leakage I D, I S (ON)V S = V D = 8 V/0 V;ADG408±1±100±1±100nA max Test Circuit 4ADG409±1±50±1±50nA maxDIGITAL INPUTSInput High Voltage, V INH 2.4 2.4V minInput Low Voltage, V INL0.80.8V maxInput CurrentI INL or I INH±10±10µA max V IN = 0 or V DDC IN, Digital Input Capacitance88pF typ f = 1 MHzDYNAMIC CHARACTERISTICS2t TRANSITION130130ns typ R L = 300 Ω, C L = 35 pF;V S1 = 8 V/0 V, V S8 = 0 V/8 V;Test Circuit 5t OPEN1010ns typ R L = 300 Ω, C L = 35 pF;V S = +5 V; Test Circuit 6t ON (EN)140140ns typ R L = 300 Ω, C L = 35 pF;V S = +5 V; Test Circuit 7t OFF (EN)6060ns typ R L = 300 Ω, C L = 35 pF;V S = +5 V; Test Circuit 7 Charge Injection55pC typ V S = 0 V, R S = 0 Ω, C L = 10 nF;Test Circuit 8OFF Isolation–75–75dB typ R L = 1 kΩ, f = 100 kHz;V EN = 0 V; Test Circuit 9 Channel-to-Channel Crosstalk8585dB typ R L = 1 kΩ, f = 100 kHz;Test Circuit 10C S (OFF)1111pF typ f = 1 MHzC D (OFF) f = 1 MHzADG4084040pF typADG4092020pF typC D, C S (ON) f = 1 MHzADG4085454pF typADG4093434pF typPOWER REQUIREMENTSI DD11µA typ V IN = 0 V, V EN = 0 V55µA maxI DD100100µA typ V IN = 0 V, V EN = 2.4 V200500200500µA maxNOTES1Temperature ranges are as follows: B Version: –40°C to +85°C; T Version: –55°C to +125°C.2Guaranteed by design, not subject to production test.Specifications subject to change without notice.REV. A–3–ADG408/ADG409REV. A–4–ABSOLUTE MAXIMUM RATINGS 1(T A = +25°C unless otherwise noted)V DD to V SS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+44 V V DD to GND . . . . . . . . . . . . . . . . . . . . . . . . . .–0.3 V to +25 V V SS to GND . . . . . . . . . . . . . . . . . . . . . . . . . . .+0.3 V to –25 V Analog, Digital Inputs 2 . . . . .V SS –2 V to V DD +2 V or 20 mA,Whichever Occurs FirstContinuous Current, S or D . . . . . . . . . . . . . . . . . . . . .20 mA Peak Current, S or D(Pulsed at 1 ms, 10% Duty Cycle max) . . . . . . . . . . .40 mA Operating Temperature RangeIndustrial (B Version) . . . . . . . . . . . . . . . . .–40°C to +85°C Extended (T Version) . . . . . . . . . . . . . . . .–55°C to +125°C Storage Temperature Range . . . . . . . . . . . .–65°C to +150°C Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . .+150°C Cerdip Package, Power Dissipation . . . . . . . . . . . . . . .900 mW θJA , Thermal Impedance . . . . . . . . . . . . . . . . . . . . .76°C/W Lead Temperature, Soldering (10 sec) . . . . . . . . . . .+300°C Plastic Package, Power Dissipation . . . . . . . . . . . . . . .470 mW θJA , Thermal Impedance . . . . . . . . . . . . . . . . . . . .117°C/W Lead Temperature, Soldering (10 sec) . . . . . . . . . . .+260°C TSSOP Package, Power Dissipation . . . . . . . . . . . . . .450 mW θJA , Thermal Impedance . . . . . . . . . . . . . . . . . . . .155°C/W θJC , Thermal Impedance . . . . . . . . . . . . . . . . . . . . .50°C/W SOIC Package, Power Dissipation . . . . . . . . . . . . . . . .600 mW θJA , Thermal Impedance . . . . . . . . . . . . . . . . . . . . .77°C/W Lead Temperature, SolderingVapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . .+215°C Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . .+220°CNOTES 1Stresses above those listed under Absolute Maximum Ratings may cause perma-nent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.2Overvoltages at A, EN, S or D will be clamped by internal diodes. Current should be limited to the maximum ratings given.ORDERING INFORMATIONModel 1Temperature Range Package Option 2ADG408BN –40°C to +85°C N-16ADG408BR –40°C to +85°C R-16A ADG408BRU –40°C to +85°C RU-16ADG408TQ –55°C to +125°C Q-16ADG409BN –40°C to +85°C N-16ADG409BR –40°C to +85°C R-16A ADG409TQ–55°C to +125°CQ-16NOTES 1To order MIL-STD-883, Class B processed parts, add /883B to T grade part numbers.2N = Plastic DIP; Q = Cerdip; R = 0.15" Small Outline IC (SOIC);RU = Think Shrink Small Outline Package (TSSOP).CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test eq uipment and can discharge without detection.Although the ADG408/ADG409 feature proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore,proper ESD precautions are recommended to avoid performance degradation or loss of functionality.ADG408/ADG409REV. A –5–TERMINOLOGYV DD Most positive power supply potential.V SSMost negative power supply potential in dual supplies. In single supply applications, it may be connected to ground.GND Ground (0 V) reference.R ON Ohmic resistance between D and S.∆R ON Difference between the R ON of any two channels.I S (OFF)Source leakage current when the switch is off.I D (OFF)Drain leakage current when the switch is off.I D , I S (ON)Channel leakage current when the switch is on.V D (V S )Analog voltage on terminals D, S.C S (OFF)Channel input capacitance for “OFF”condition.C D (OFF)Channel output capacitance for “OFF”condition.C D , C S (ON)“ON” switch capacitance.C IN Digital input capacitance.t ON (EN)Delay time between the 50% and 90% points of the digital input and switch “ON” condition.t OFF (EN)Delay time between the 50% and 90% points of the digital input and switch “OFF” condition.t TRANSITIONDelay time between the 50% and 90% points of the digital inputs and the switch “ON” condition when switching from one address state to another.t OPEN“OFF” time measured between the 80% point of both switches when switching from one address state to another.V INL Maximum input voltage for Logic “0.”V INH Minimum input voltage for Logic “1.”I INL (I INH )Input current of the digital input.CrosstalkA measure of unwanted signal which is coupled through from one channel to another as a result of parasitic capacitance.Off Isolation A measure of unwanted signal coupling through an “OFF” channel.Charge A measure of the glitch impulse transferred Injection from the digital input to the analog output during switching.I DD Positive supply current.I SSNegative supply current.PIN CONFIGURATIONS (DIP/SOIC/TSSOP)A0EN V SS S1S2S3S4D A1A2GNDV DD S5S6S7S8V DDADG408 Truth TableONA2A1A0EN SWITCH X X X 0NONE 0001100112010130111410015101161101711118ADG409 Truth TableON SWITCH Al A0EN PAIR X X 0NONE 0011011210131114ADG408/ADG409REV. A–6–Typical Performance CharacteristicsV D (V S ) – VoltsR O N – ⍀Figure 1.R ON as a Function of V D (V S ): Dual Supply VoltageV D (V S ) – Volts10030R O N – ⍀807050406090Figure 2.R ON as a Function of V D (V S ) for Different Temperatures V D (V S ) – Volts0.2–0.2L E A K A G E C U R R E N T – n A–0.10.1Figure 3.Leakage Currents as a Function of V D (V S )V D (V S ) – Volts18040R O N – ⍀1401208060160100Figure 4.R ON as a Function of V D (V S ): Single Supply VoltageV D (V S ) – Volts13060R O N – ⍀100807090120110Figure 5.R ON as a Function of V D (V S ) for Different TemperaturesV D (V S) – VoltsL E A K A G E C U R R E N T – n AFigure 6.Leakage Currents as a Function of V D (V S )ADG408/ADG409REV. A –7–V IN – Volts12020t – n s604010080Figure 7.Switching Time vs. V IN (Bipolar Supply)V SUPPLY – Volts400t – n s200100300Figure 8.Switching Time vs. Single Supply FREQUENCY – Hz104103102I D D – A10M101001k 10k 100k 1MFigure 9.Positive Supply Current vs. Switching FrequencyV IN – Voltst – n sFigure 10.Switching Time vs. V IN(Single Supply)V SUPPLY – Volts3000t – n s200100Figure 11.Switching Time vs. Bipolar SupplyFREQUENCY – Hz10410310–110M1M 10I S S – A1001k 10k 100k 102101100Figure 12.Negative Supply Current vs. Switching FrequencyADG408/ADG409REV. A–8–FREQUENCY – Hz11070O F F I S O L A T I O N – d B9080100Figure 13.Off Isolation vs. Frequency FREQUENCY – Hz11070C R O S S T A L K – d B908010060Figure 14.Crosstalk vs. FrequencyTest CircuitsI V Test Circuit 1.On ResistanceV I S Test Circuit 2.I S(OFF)V V V (OFF)Test Circuit 3.I D (OFF)V V V (ON)Test Circuit 4. I D (ON)ADG408/ADG409REV. A –9–VVV 35pFTest Circuit 5.Switching Time of Multiplexer, t TRANSlTlONVVV Test Circuit 6.Break-Before-Make Delay, tOPENV V35pFV 3V 0VTest Circuit 7. Enable Delay, t ON (EN), t OFF (EN)ADG408/ADG409REV. A–10–VVOUT 3VV INVTest Circuit 8.Charge InjectionV OUTV OFF ISOLATION = 20 LOG V OUT /V IN Test Circuit 9.OFF Isolation VV OUTOUT INTest Circuit 10.Channel-to-Channel CrosstalkADG408/ADG409REV. A –11–OUTLINE DIMENSIONSDimensions shown in inches and (mm).Plastic DIP (N-16)Cerdip (Q-16)BSCSO (Narrow Body) (R-16A)°Thin Shrink Small Outline Package (TSSOP)(RU-16)PLANE BSC(1.10)MAX0.0035 (0.090)C 1824a –0–4/98P R I N T E D I N U .S .A .。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CMOS模拟开关及其应用

无线电86.12 彭定武

CMOS(互补金属氧化物半导体)集成电路具有微功耗、使用电源电压范围宽和抗干扰能力强等特点。

其发展日新月异,应用范围十分广泛。

本文介绍的CMOS 模拟开关集成电路,在音频和视频范围可以使增益控制数字化,和微处理器配合使用可以简化自动控制电路的设计。

下面就MOS场效应管及CMOS模拟开关作一介绍。

MOS场效应管的工作原理

金属氧化物半导体场效应三极管是通过光刻或扩散的方法,在P型基片(衬

底)上制作两个N型区,在N

型区上通过铝层引出两个电

极,即源极(S)和漏极(D)。

漏源两个扩散区之间的硅表

面上生成一层绝缘的氧化膜

(二氧化硅),在氧化膜上也制作一个铝电极,即为栅极(G),两个扩散区和P型衬底分别构成PN结。

如果把源极和衬底相连接,并在栅源极间加正电压UGS,就会在衬底表面形成一个导电的反型层,它把漏源两个N扩散区连接起来,成为可以导电的沟道,见图1(a)。

若在漏源之间也加正

电压U DS,则源极与漏

极之间将有漏电流I D

流通,且I D随U DS的

增加而增大。

我们把开

始有漏电流产生时的

电压叫做开启电压U T,把在P型衬底上形成的导电反型层的场效应管叫做N沟道增强型MOS场效应管。

其符号见图1(b)。

MOS场效应管的漏极特性曲线及漏极电流I D随栅极电压U GS变化的特性曲线如图2所示。

由以上分析,我们可以把MOS管的漏极D和源极S当作一个受栅极电压U GS 控制的开关使用,即当U GS>U T时,漏极D与源极S之间导通,相当于一个开关

接通,导通电阻约几百欧姆。

当U<U T时漏极D与源极s之间不导通,没有电流流过,则如同开关断开一样。

同样,也可在N型基片上制作两个P型区,以形成P沟道增强型MOS管,见图3。

典型的P沟道增强型MOS管的特性曲线如图4所示。

比较图2和图4我们可以看出,P沟道和N沟道MOS管的特性曲线是相反的。

在了解了MOS管的

基本工作原理和特性曲线

以后,下面谈谈CMOS开

关。

简单的CMOS开关

如果将P沟道MOS管

Q1和N沟道MOS管Q2的衬底,漏极和源极连接在一起,将它们的栅极分别接到反相器JC1的输出端和输入端,JC1的输入端再由开关

S1控制接正电压或接地,见图5。

当开关S1接地时,Q2 的栅极是

低电位,使U GS2<U T2,因它是

N沟道MOS管,由前面分析可

知,Q2 应截止。

同时开关所接

低电位经反向器JC1反相变为高

电位,使得U GS1>U T1,因它是P沟道MOS管,此时Q1也截止。

其结果是A B 两端处于断开状态,即相当于一个开关断开。

当开接S1接到正电源时,Q2 的栅极为高电位,因U GS2> U T2,故Q2 导通。

同样,高电位经JC1反相变为低电位,使得U GS1<U T1,故Q1也导通。

其结果是A、B两端是导通状态,即相当于一个开关接通。

图5电路是建立在P沟道和N沟道MOS场效应管两者对称的情况,但在实际中并非完全如此。

如果它们之间的参数有差异,那么从A点到B点的信号通道与从B点到A点的信号通道就有可能不完全相同,若差别较大,则可能引起信号失真。

图6是一种改进了的CMOS

开关电路。

与图5相比,在开关的输入端又加了两个反向器JC2和JC3,因反相再反相其方向不变,故所加反相器只起隔离控制电压和CMOS开关的作用。

除此而外。

在Q1和Q2 上又并联了两只分别与它们相同的MOS场效应管Q4 、Q5 ,还加接了一只N沟道MOS管Q3。

Q1和Q2并联上Q4和Q5以后,因并联的原因,跨过A、B两端的电压降将小于简单开关电路的情况,电压降减小。

意味着导通电阻的减小。

当开关S1接地时,Q1、Q4 P沟道MOS场效应管因栅极高电位而截止,Q2 、Q5N沟道MOS场效应管因栅极为低电位也处于截止状态,其结果使AB两端呈断开状态。

Q3是N沟道MOS管,此时因栅极接高电位,使栅极和源极(接地)的PN给正偏置而导通,且导通电阻比较小,如果有来自控制部分的外来干扰信号,就会被Q3旁路。

因而提高了A、B两端处于断开状态时的稳定度。

当开关S1接电源高电位对,分析同图5故不多述。

近年来已将CMOS开关设计成中规模集成电路(MSI),可以解决很多电路中的开关问题。

下面举几个例子加以说明。

CMOS模拟开关集成电路及应用

图7所示是一个具有四个单刀单掷开

关的CMOS集成电路,型号为4016。

其中

每一个开关都是由图6所示的电路组成的。

图中的引出脚①、②相当于图6中的A、B

两点,引出脚③相当于图6中的开关S1 。

在实际使用中并没有开关S1,而是加上一

个幅度相当于电源(+U)的正脉冲。

当未加正脉冲时,相当于S1接地(低电位)。

开关处于断开状态。

当正脉冲到来时,相当于S1接正电压(高电位),开关处于导通状态。

我们称图中的引出脚1和2;3和4;8和9;10和11组成四个CMOS模拟开关。

它们之间的串音很小,其隔离系数约为50db。

图8是一个由4016组成的增益控制数字化电路。

其中的IC是一个线性放大器,在它的输出与输入之间接上4016CMOS开关,用来控制反馈电阻R1、R2、

R3及R4是否接入电路。

由于控制输入端是低电位时,CMOS开关处于断开状态,故线性放大器的反馈电阻未能接上。

只在控制端为高电位时,因CMOS开关导通而接通反馈电阻网络。

如果在控制输入端输入不同的低电位和高电位信号,就可使反馈电阻因不同组合而得到改变。

在控制输入端为4输入端的情况下,共有16级增益变化,见表一。

采用数字增益控制给我们带来很多好处。

我们知道,音频范围内的电源交流声是比较难以解决的问题,采用屏蔽电缆也不易彻底解决。

如果使用数字信号控制增益,导线中只传输数字信号,上述问题就很容易得到解决。

图9所示为另一种

CMOS集成电路,其型号

为4051。

它是一种单刀8

档开关,引出脚3是开关

的刀,它接到哪一档由加

到控制脚9、10和11的电

压来决定。

表二列出了输

出脚与控制脚的关系。

如

果控制脚都为低态

(A=B=C=)0,输出脚是

13。

若A、B接地,C按

正电压(A=B=0 C=1),

输出脚则是14。

引出脚6

是禁止脚,如果它是高电

位,则全部输入脚和输出

脚均呈

断开状

态。

引出脚7是模拟/数字,它是专为开关用在模拟或数字两种

情况而设计

的。

在模拟情

况时,信号有

正负方向,在数字情况时,则只有高态“1”和低态“0”。

如果4051用于数字电路,则引出脚7接地,若用于模拟电路时,引出脚7与系统最低电平连接,这个最低电平即是模拟电压摆动的下限(往往是负值)。

图10所示是使用4051CMOS开关选择放大器的输入信号。

在控制脚9、10和11输入数字信号,根据表2所指输出脚,即可选择不同的输入通道。

由于CMOS模拟开关在

导通情况下,信号可以沿不

同方向流动,而且使用在模

拟情况下,我们可以把

4051CMOS开关倒过来使

用,见图11。

这时,放大器的输出接到引脚3输入信号,这样就变成一个分配放大器。

如果加在控制脚上的数字信号以一定的速率重复交替变化,则分配放大器的输出端也相应地以一定的速率重复交替变化,实现扫描输出。

4051CMOS开关集成电路可以在2MHZ的速率下扫描输出。

用它作分配放大器,可用一个放大器推动八个输出负载,每个输出端都不会有明显的信号损失。

使用CMOS开关应注意以下几点

(1)CMOS开关与其他CMOS集成电路一样,由于MOS场效应管衬底上的氧化层特别薄,故容易被一定强度的静电荷所击穿。

因此在使用时要采取一定的防静电措施,决不能在通电的情况下接插集成电路,否则电路将被损坏。

(2)通过开关的电流,在使用不同电源电压时有所不同。

在正常情况下,工作电压为3伏到15伏,电流不超过25毫安(图5电路)或15毫安(图6电路),不可强行使开关通过更大的电流,否则会影响电路性能以致烧毁开关电路。

(3)不要把控制引出脚悬空。

记住CMOS电路设计必须遵循的规则,所有的输入端一定要和相关的地方连接好。

由于控制引出脚在集成电路的内部是与反相器相连的,如果将控制引出脚悬空,使CMOS开关处于不稳定状态,反相器很可能将MOS场效应管偏置到线性工作区。

这也有可能使电流剧增而烧环集成电路或其他有关电路。

(4)必须限制输入电压,使输入电压的变化范围不超过电源电压的最大值或

低于地。

由于CMOS集成电路能够安全工作的电压可到15伏,一般来说不会出现什么问题。

在必要的时候可以先减小输入信号,通过开关后再增大信号。

CMOS模拟开关集成电路的种类很多,用途十分广泛,只要掌握了基本原理、性能,必将给我们的工作带来极大的方便。