分立元件逻辑门(精选)

电子课件电子技术基础第六版第六章门电路及组合逻辑电路可编辑全文

逻辑函数除可以用逻辑函数表达式(逻辑表达式)表示以 外,还可以用相应的真值表以及逻辑电路图来表示。真值表 与前述基本逻辑关系的真值表类似,就是将各个变量取真值 (0 和 1)的各种可能组合列写出来,得到对应逻辑函数的真 值(0 或 1)。逻辑电路图(逻辑图)是指由基本逻辑门或复 合逻辑门等逻辑符号及它们之间的连线构成的图形。

TTL 集成“与非”门的外形和引脚排列 a)外形 bOS 集成门电路以绝缘栅场效应管为基本元件组成, MOS 场效应管有 PMOS 和NMOS 两类。CMOS 集成门电路 是由 PMOS 和 NMOS 组 成的互补对称型逻辑门电路。它具 有集成度更高、功耗更低、抗干扰能力更强、扇出系数更大 等优点。

三、其他类型集成门电路

1. 集电极开路与非门(OC 门) 在这种类型的电路内部,输出三极管的集电极是开路的, 故称集电极开路与非门,也称集电极开路门,简称 OC 门。

OC 门 a)逻辑符号 b)外接上拉电阻

74LS01 是一种常用的 OC 门,其外形和引脚排列如图所 示。

74LS01 的外形和引脚排列 a)外形 b)引脚排列

2. 主要参数 TTL 集成“与非”门的主要参数反映了电路的工作速度、抗 干扰能力和驱动能力等。

TTL 集成“与非”门的主要参数

TTL 集成“与非”门具有广泛的用途,利用它可以组成很多 不同逻辑功能的电路,其外形和引脚排列如图所示。如 TTL“ 异或”门就是在 TTL“与非”门的基础上适当地改动和组合而成 的;此外,后面讨论的编码器、译码器、触发器、计数器等 逻辑电路也都可以由它来组成。

2.1 分立元件门电路

~ 220V A

开关闭合为 1

开关断开为 0

F

灯亮为 1

灯不亮为 0

AF 01 10

工作波形:

逻辑符号:

逻辑表达式:

FA

VCC(12V) VCL(+3V)

F

A

C1

&

F

R1

AA

(2)、非门 反相器就是非门

R2

RC

D

T

VBB(-12V)

+12V

OV

R 0.7V

R 1.4V

R 2.1V

输入低电平0V,经过三极与门的移位,使输出的低电 平达到2.1V。输出和输入电平相差很大,会造成逻辑功 能紊乱。而且,带负载的能力和抗干扰的能力都比较差, 所以很少直接应用。

反相器的优点是:没有电平偏移,抗干扰能力和带负 载能力都比较强。因此:将二极管门和三极管反相器连接 起来就构成与非门及或非门。

与非门由二极管与门及反相器组成。 VCC(12V)

VCL(3V)

与非门有运0算为顺序1,是: 先与后非

反相与器运输算入全:是1有0为,0输为0出0。,为全11。为1。BA

R

A0

5V

3V 3V 3V 1 1 1 B 0

规定:

F

F0

高电平用“1”表 & 与运算逻辑符号:

低示电平用“0”表示

AB

与运算逻辑表达式: F A B

(1)、逻辑或的概念:决定某一件事

A

的诸条件中,只要有一个或一个以上的条

件满足,这件事的结果就会发生,否则结

B

果不会发生。这样的逻辑关系称为:逻辑 ~ 220V

C1

RC

D

F

逻辑门电路

逻辑门电路1.1 晶体管的开关特性及应用在数字电路中,晶体管大多工作在开关状态,所以是一种无触点的电子开关。

通常的电子开关按其用途,可分为模拟开关和数字开关(又称逻辑开关)两大类。

对它们的要求也有所不同:模拟开关应具备断开和接通时,流过的电流或两端的电压为零,两种状态转换的时间为零;而对数字开关则要求器件有两种可以区分的工作状态,同时输出能明确地用逻辑0或1来表示。

1.1.1 晶体二极管的开关特性及应用1. 晶体二极管的开关特性图1-1是硅二极管的符号和伏安特性曲线。

由伏安特性可知:(1) 二极管端电压小于0.5V作为二极管的截止条件。

一旦截止,即可近似认为电流等于0,相当于开关断开,这就是二极管截止时的特点。

(2)二极管正向电压大于0.5V作为二极管的导通条件。

一旦导通,即可将二极管认为是具有0.7V压降的闭合开关,这就是二极管导通时的特点。

2. 二极管开关特性的应用利用二极管开关特性可以构成限幅器和钳位器。

(1) 二极管限幅器。

限幅器是一种波形变换或整形电路。

当输入信号在一定范围内变化时,输出电压跟随输入电压相应变化,完成信号的传输;而当输入电压超过这一范围时,其超过的部分被削去,输出电压保持不变,实现限幅作用,由于限幅器能将一定范围以外的输入波形削去,所以限幅器又称削波器。

(2) 二极管钳位器。

二极管钳位器是利用二极管的开关特性,将输入波形的顶部或底部钳定在某一选定的电平上的电路。

这种错位作用又称为波形钳位,在脉冲技术中经常用到。

1.1.2 晶体三级管的开关特性及应用 1. 晶体三极管的开关特性如图1-6所示为NPN 型三极管的电路和特性曲线。

图中直流负载线和三极管输出特性曲线的交点称为静态工作点,用Q 表示。

工作点的位置由基极电流iB 决定。

由于工作点的位置不同,三极管有3种不同的工作状态,或称为3个工作区域。

(1)0,0≈≈i i C B 的区域称为截止区,如图中的Q1点。

在截止区,三极管的集电极C 和发射极e 之间近似为开路,相当于开关断开一样,故有u u CCCE≈。

分立元件门电路和集成电路的逻辑符号

分立元件门电路和集成电路的逻辑符号什么是分立元件门电路和集成电路分立元件门电路和集成电路是电子电路中常用的两种逻辑门实现技术。

逻辑门是数字电路的基本构建模块,用于处理二进制数字,实现逻辑运算等功能。

分立元件门电路是通过使用离散的电子元件来构建逻辑门,而集成电路则是将逻辑门的元件集成在一个芯片中。

分立元件门电路的逻辑符号分立元件门电路使用不同的逻辑符号来表示不同的逻辑门,常见的逻辑门包括与门、非门、或门、与非门、或非门、异或门等。

1.与门(AND Gate)的逻辑符号是一个带有两个输入端和一个输出端的图形。

输入端上通常连接输入信号,而输出端上则输出根据输入信号进行逻辑与运算的结果。

与门的逻辑符号通常用字母”AND”表示。

2.非门(NOT Gate)的逻辑符号是一个带有一个输入端和一个输出端的图形。

非门将输入信号取反后输出,用于实现逻辑非运算。

非门的逻辑符号通常用字母”NOT”或”!“表示。

3.或门(OR Gate)的逻辑符号是一个带有两个输入端和一个输出端的图形。

或门将输入信号进行逻辑或运算后输出结果。

或门的逻辑符号通常用字母”OR”表示。

4.与非门(NAND Gate)的逻辑符号是一个带有两个输入端和一个输出端的图形。

与非门将输入信号进行逻辑与运算后取反输出,实现逻辑与非运算。

与非门的逻辑符号通常用字母”NAND”表示。

5.或非门(NOR Gate)的逻辑符号是一个带有两个输入端和一个输出端的图形。

或非门将输入信号进行逻辑或运算后取反输出,实现逻辑或非运算。

或非门的逻辑符号通常用字母”NOR”表示。

6.异或门(XOR Gate)的逻辑符号是一个带有两个输入端和一个输出端的图形。

异或门实现异或运算,当输入信号相同时输出为低电平,当输入信号不同时输出为高电平。

异或门的逻辑符号通常用字母”XOR”表示。

集成电路的逻辑符号集成电路通过将逻辑门的元件集成在一个芯片中实现,它可以以一个整体的形式提供逻辑门的功能,简化了电路的布局和设计。

实验一分立元件(由二极管三极管组成的)逻辑门电路

实验一分立元件(由二极管三极管组成的)逻辑门电路一、实验目的1.熟悉并掌握由二极管、三极管组成的逻辑门电路。

2.掌握数字电路实验装置及示波器的使用方法。

二、实验仪器与器材1.数字电路实验装置2.双踪示波器三、预习要求1.复习二极管、三极管的开关特性。

2.了解双踪示波器的使用方法。

四、实验内容与步骤(一)二极管与门电路实验步骤:1、按图-1所示连接电路2、检查无误后,按表-1所列的真值表设置开关K、2K的状态,1开关闭合表示为“0”,开关断开或发光二极管亮表示为“1”,然后检测每次的输出端的状态填入表-1中,应符合逻辑关系式Y=AB。

(注:K=A,2K=B,Y代表发光二极管。

下同)13、根据真值表和逻辑关系式Y=AB,总结二极管与门电路的功能为“全高则高,有低则低”。

图-1 二极管与门电路表-1 真值表(二)二极管或门电路 实验步骤:1、按图-2所示连接电路。

2、检查无误后,按表-2所列的真值表设置开关1K 、2K 的状态,开关闭合表示为“1”,开关断开表示为“0”,发光二极管亮表示为“1”,然后检测每次的输出端的状态填入表-1中,应符合逻辑关系式Y=A+B 。

图-2 二极管或门电路 表-2 真值表3、根据真值表和逻辑关系式Y=A+B ,总结二极管或门电路的功能为“全低则低,有高则高”。

(三)三极管非门电路实验步骤:1、按图-3所示连接电路2、检查无误后,按表-3所列的真值表设置开关K 的状态,开关闭合表示为“1”, 开关断开表示为“0”,发光二极管亮表示为“1”,然后检测每次的输出端的状态填入表-3中,应符合逻辑关系式Y=A 。

3、根据真值表和逻辑关系式Y=A ,总结三极管非门电路的功能相当于反相器“是低则高,是高则低”。

(注:K=A )图-3 三极管非门电路 表-3 真值表(四)三极管与非门电路实验步骤:1、按图-4所示连接电路2、检查无误后,按表-4所列的真值表设置开关1K 、2K 的状态,开关闭合表示为“0”,开关断开或发光二极管亮表示为“1”,然后检测每次的输出端的状态填入表-1中,应符合逻辑关系式Y=AB 。

12.04分立元件组成的基本门电路

4、三极管“非门”电路 三极管“非门”

(1)、电路和符号 R1 A R2 -VBB (2)、工作原理 (3)、 (3)、表达式和真值表 +VCC RC F A 1 F

真值表: 真值表:

F=A

A 0 1

F 1 0

5、“与非” 与非” 门

实际上,可以将二极管“ 实际上,可以将二极管“与”门和三极管“非”门 门和三极管“ 组合在一起而构成“与非” 组合在一起而构成“与非”门。 +12V +VCC DA A B C DB DC

A B C

≥1

F

2、工作原理

真值表: 真值表:

有高出高, 有高出高, 全低出低

A B C DA

-12V R F

ABC 000 001 010 011 100 101 110 111

F 0 1 1 1 1 1 1 1

DB DC

3、表达式和真值表

F=A+B+C

二:晶体管的开关作用

晶体管不仅具有放大作用, 晶体管不仅具有放大作用,而且还具有开关 作用。在数字电路中就是利用晶体管的开关作用。 作用。在数字电路中就是利用晶体管的开关作用。 如前所述,我们可以根据 如前所述,我们可以根据UCC和RC作出直流 负载线, 负载线,负载线与晶体管输出特性曲线的交点就 是静态工作点,工作点的位置由偏流I 确定。 是静态工作点,工作点的位置由偏流 B确定。由 于工作点的位置不同,晶体管有三种工作状态。 于工作点的位置不同,晶体管有三种工作状态。 一、放大状态 1、发射结正偏,集电结反偏 发射结正偏, UCE=UCC-RCIC成立 2、IC=βIB成立

数字电路在数字计算机数字控制数据采集和处理数数字电路在数字计算机数字控制数据采集和处理数字通讯等领域获得广泛应用

分立元件逻辑门的级联

分立元件逻辑门的级联在数字电路设计中,分立元件逻辑门的级联是一种常见的组合逻辑方法。

分立元件逻辑门包括与门、或门、非门等基本逻辑门,通过合理地连接这些逻辑门,可以实现复杂的数字逻辑电路。

级联是将多个逻辑门按照一定的方式相互连接,以实现更丰富的功能。

首先,我们来了解一下分立元件逻辑门的原理及应用:1. 与门:与门(AND gate)接收两个或多个输入信号,当所有输入信号都为高电平(通常表示为1)时,输出为高电平;否则,输出为低电平(通常表示为0)。

与门广泛应用于组合逻辑电路的设计中。

2. 或门:或门(OR gate)接收两个或多个输入信号,当任意一个输入信号为高电平时,输出为高电平;只有当所有输入信号都为低电平时,输出才为低电平。

或门常用于构建多路选择器、编码器等电路。

3.非门:非门(NOT gate)只接收一个输入信号,输出信号与输入信号相反。

非门常用于信号反相、时序控制等场合。

在了解了基本逻辑门的工作原理后,我们可以将它们级联以实现更复杂的逻辑功能。

以下是一个分立元件逻辑门级联的例子:假设我们有一个输入信号A和两个输出信号Y和Z。

我们可以通过以下逻辑电路实现输出Z与输入A的反相(即Z= NOT A):1. 将输入信号A接入非门(NOT gate)的输入端,得到输出信号B(B= NOT A)。

2. 将输出信号B与输入信号A接入与门(AND gate),得到输出信号C(C= A·B)。

3. 将输出信号C接入非门(NOT gate),得到输出信号Z(Z= NOT C = NOT(A·B))。

通过这个级联电路,我们实现了输出信号Z与输入信号A的反相。

此外,我们还可以通过调整逻辑门的连接方式,实现其他复杂的逻辑功能。

分立元件逻辑门的级联在数字电路设计中具有重要意义。

掌握这种方法,有助于我们更好地理解数字逻辑电路的工作原理,并灵活地设计出满足实际需求的数字电路系统。

同时,分立元件逻辑门的级联也是学习现代数字电子技术的基础,对于深入理解计算机原理、嵌入式系统等领域具有重要意义。

分立元件逻辑门

(2-18)

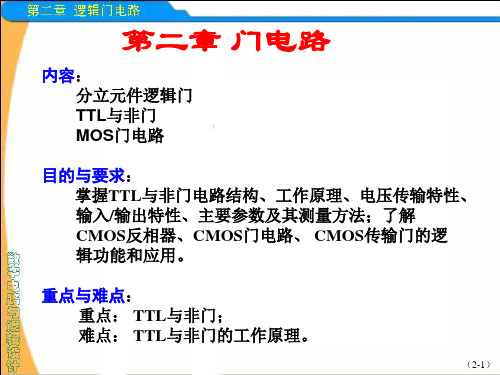

§2.3

TTL与非门 TTL与非门

二、输入、输出负载特性 输入、

1. 扇出系数 扇出系数: &

与非门电路输出能驱动同类门的个数。 与非门电路输出能驱动同类门的个数。

?

&

分两种情况讨论: 分两种情况讨论:

(1)前级输出为 高电平时 ) (2)前级输出为 低电平时 )

(2-9)

§2.3

TTL与非门 TTL与非门

+5V

R1 R2 T3 R5 T5 R4

A B C

T1

T2

T4

F

T1 —多发射极晶 多发射极晶 体管:实现“ 体管:实现“与” R3 运算。 运算。

输入级

中间级

输出级

(2-10)

§2.3

TTL与非门 TTL与非门

+5V

R1 R2 T3 R5 T5 R3 R4 复合管形式 A B C

OC门可以实现“线与”功能。 门可以实现“线与”功能。 门可以实现 UCC & F1 & F2 & F3 分析: 任一导通, 分析:F1、F2、F3任一导通,则F=0。 。 F1、F2、F3全截止,则F=1 。 全截止, RL F

UCC RL T5 T5 T5

T1

T2

T4

F

“与” 与

“非” 非

输出级

与非门

(2-11)

二、工作原理 1. 任一输入为低电平(0.3V)时 任一输入为低电平( )

不足以让 T2、T5导通 、 R1 3k 0.7V b1 R2 750Ω Ω T2 T3 3k R5

§2.3

TTL与非门 TTL与非门