verilog学习笔记

DC-PT-FM-ICC学习笔记

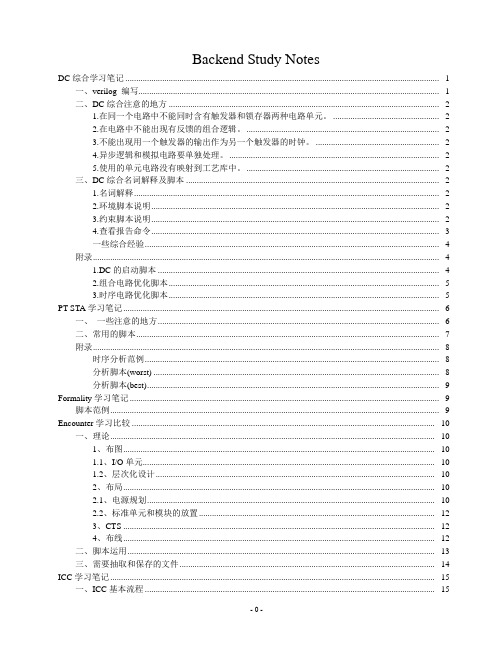

Backend Study NotesDC综合学习笔记 ................................................................................................................................................. - 1 -一、verilog 编写........................................................................................................................................... - 1 -二、DC综合注意的地方 ............................................................................................................................. - 2 -1.在同一个电路中不能同时含有触发器和锁存器两种电路单元。

................................................. - 2 -2.在电路中不能出现有反馈的组合逻辑。

......................................................................................... - 2 -3.不能出现用一个触发器的输出作为另一个触发器的时钟。

......................................................... - 2 -4.异步逻辑和模拟电路要单独处理。

................................................................................................. - 2 -5.使用的单元电路没有映射到工艺库中。

自己整理的:学习verilogDHL问题笔记——Quartus常见错误

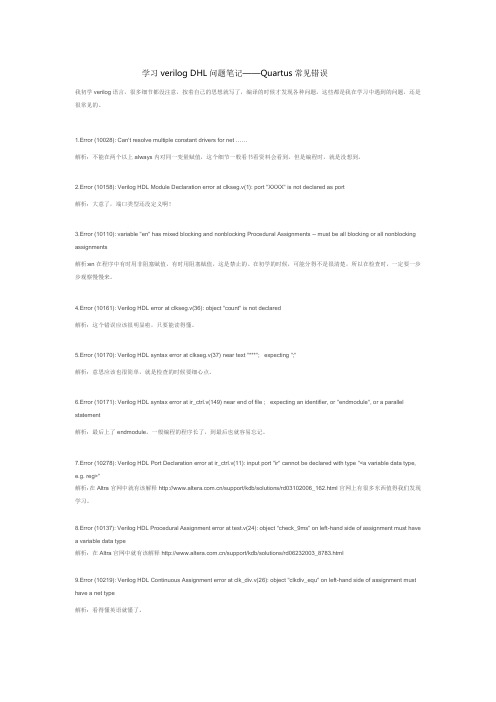

⾃⼰整理的:学习verilogDHL问题笔记——Quartus常见错误我初学verilog语⾔,很多细节都没注意,按着⾃⼰的思想就写了,编译的时候才发现各种问题。

这些都是我在学习中遇到的问题,还是很常见的。

1.Error (10028): Can't resolve multiple constant drivers for net ……解析:不能在两个以上always内对同⼀变量赋值,这个细节⼀般看书看资料会看到,但是编程时,就是没想到。

2.Error (10158): Verilog HDL Module Declaration error at clkseg.v(1): port "XXXX" is not declared as port解析:⼤意了,端⼝类型还没定义啊!3.Error (10110): variable "en" has mixed blocking and nonblocking Procedural Assignments -- must be all blocking or all nonblocking assignments解析:en在程序中有时⽤⾮阻塞赋值,有时⽤阻塞赋值,这是禁⽌的。

在初学的时候,可能分得不是很清楚,所以在检查时,⼀定要⼀步步观察慢慢来。

4.Error (10161): Verilog HDL error at clkseg.v(36): object "count" is not declared解析:这个错误应该很明显啦,只要能读得懂。

5.Error (10170): Verilog HDL syntax error at clkseg.v(37) near text "***"; expecting ";"解析:意思应该也很简单,就是检查的时候要细⼼点。

学习verilog DHL问题笔记——Quartus常见错误

学习verilog DHL问题笔记——Quartus常见错误我初学verilog语言,很多细节都没注意,按着自己的思想就写了,编译的时候才发现各种问题。

这些都是我在学习中遇到的问题,还是很常见的。

1.Error (10028): Can't resolve multiple constant drivers for net ……解析:不能在两个以上always内对同一变量赋值,这个细节一般看书看资料会看到,但是编程时,就是没想到。

2.Error (10158): Verilog HDL Module Declaration error at clkseg.v(1): port "XXXX" is not declared as port解析:大意了,端口类型还没定义啊!3.Error (10110): variable "en" has mixed blocking and nonblocking Procedural Assignments -- must be all blocking or all nonblocking assignments解析:en在程序中有时用非阻塞赋值,有时用阻塞赋值,这是禁止的。

在初学的时候,可能分得不是很清楚,所以在检查时,一定要一步步观察慢慢来。

4.Error (10161): Verilog HDL error at clkseg.v(36): object "count" is not declared解析:这个错误应该很明显啦,只要能读得懂。

5.Error (10170): Verilog HDL syntax error at clkseg.v(37) near text "***"; expecting ";"解析:意思应该也很简单,就是检查的时候要细心点。

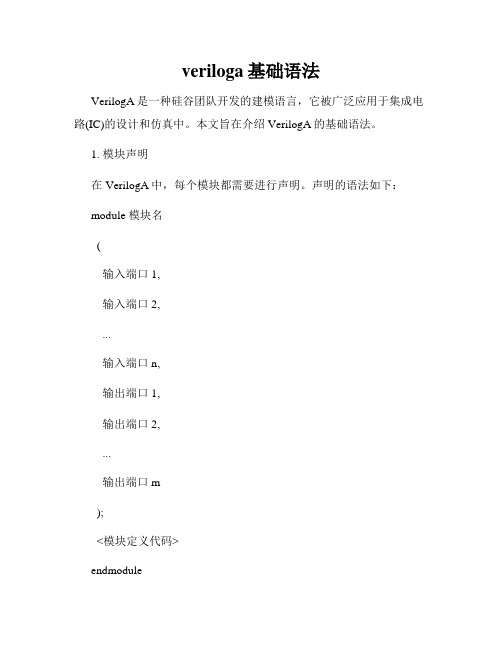

veriloga基础语法

veriloga基础语法VerilogA是一种硅谷团队开发的建模语言,它被广泛应用于集成电路(IC)的设计和仿真中。

本文旨在介绍VerilogA的基础语法。

1. 模块声明在VerilogA中,每个模块都需要进行声明。

声明的语法如下:module 模块名(输入端口1,输入端口2,...输入端口n,输出端口1,输出端口2,...输出端口m);<模块定义代码>endmodule其中,模块名可以由字母、数字和下划线组成,不能以数字开头;输入端口和输出端口可以是标量或向量。

2. 参数声明VerilogA允许在模块中声明参数,以便在实例化时进行配置。

语法如下:parameter 参数名 = 值;参数可以通过assign语句进行连接,也可以在实例化时进行配置。

3. 变量声明在VerilogA中,可以使用不同的变量类型进行声明,如实数、整数、布尔值等。

real: 实数类型,用于存储实数值。

integer: 整数类型,用于存储整数值。

boolean: 布尔类型,用于存储真/假值。

语法如下:real 变量名;integer 变量名;boolean 变量名;4. 函数和任务在VerilogA中,可以使用函数和任务来实现特定的功能。

函数是一段可重用的代码,它接收输入参数并返回一个值。

函数的语法如下:function 返回类型函数名(输入参数);<函数定义代码>return 返回值;endfunction任务是一段可重用的代码,不返回值,但可以通过参数进行输入和输出。

任务的语法如下:task 任务名(输入参数);<任务定义代码>endtask5. 运算符VerilogA支持各种常见的数学和逻辑运算符,如加减乘除、取余、与或非等。

加法运算符:+减法运算符:-乘法运算符:*除法运算符:/取余运算符:%与运算符:&&或运算符:||非运算符:!6. 控制结构在VerilogA中,可以使用if-else、for、while等控制结构来实现条件判断和循环。

16位乘法器学习笔记(Verilog语言源程序+仿真程序)

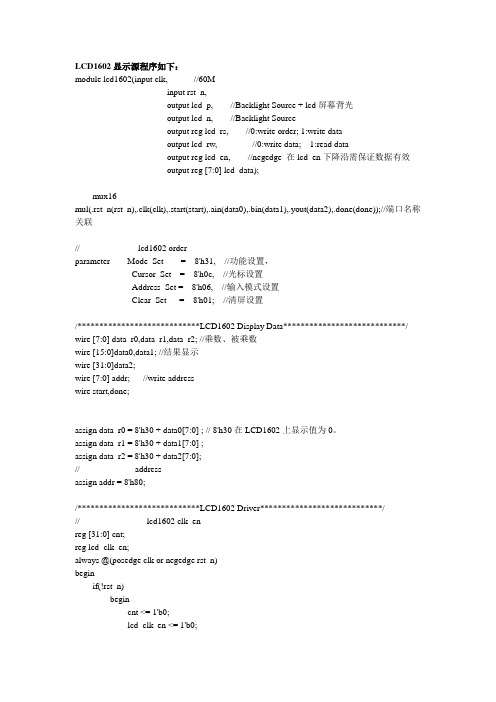

LCD1602显示源程序如下:module lcd1602(input clk, //60Minput rst_n,output lcd_p, //Backlight Source + lcd屏幕背光output lcd_n, //Backlight Source -output reg lcd_rs, //0:write order; 1:write dataoutput lcd_rw, //0:write data; 1:read dataoutput reg lcd_en, //negedge 在lcd_en下降沿需保证数据有效output reg [7:0] lcd_data);mux16mul(.rst_n(rst_n),.clk(clk),.start(start),.ain(data0),.bin(data1),.yout(data2),.done(done));//端口名称关联//--------------------lcd1602 order----------------------------parameter Mode_Set = 8'h31, //功能设置,Cursor_Set = 8'h0c, //光标设置Address_Set = 8'h06, //输入模式设置Clear_Set = 8'h01; //清屏设置/****************************LCD1602 Display Data****************************/ wire [7:0] data_r0,data_r1,data_r2; //乘数、被乘数wire [15:0]data0,data1; //结果显示wire [31:0]data2;wire [7:0] addr; //write addresswire start,done;assign data_r0 = 8'h30 + data0[7:0] ; // 8'h30在LCD1602上显示值为0。

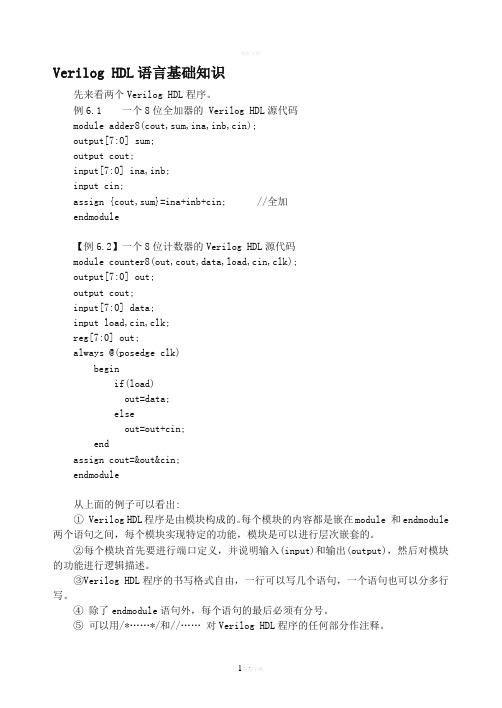

Verilog语言基础知识

在Verilog HDL中,用parameter来定义常量,即用parameter来定义一个标志符,代表一个常量,称为符号常量。其定义格式如下:

parameter 参数名1=表达式,参数名2=表达式,参数名3=表达式……;

例如:

parameter sel=8,code=8'ha3;

//分别定义参数sel为常数8(十进制),参数code为常数a3(十六进制)

Verilog HDL中共有19种数据类型。数据类型是用来表示数字电路中的数据存储和传送单元的。在此介绍4个最基本的数据类型:integer型、parameter型、reg型和wire型。

Verilog HDL中也有常量和变量之分,他们分属以上这些类型。

6.2.1 常量

在程序运行过程中,其值不能被改变的量称为常量。

assign {cout,sum}=ina+inb+cin;//全加

endmodule

【例6.2】一个8位计数器的Verilog HDL源代码

module counter8(out,cout,data,load,cin,clk);

output[7:0]out;

output cout;

input[7:0] data;

6.1.2 Verilog HDL模块的结构

Verilog HDL的基本设计单元是"模块(block)"。一个模块是由两部分组成的,一部分描述接口;另一部分描述逻辑功能,即定义输入是如何影响输出的。下面举例说明,图6.1示出了一个"与-或-非"门电路。

图6.1"与-或-非"电路

该电路表示的逻辑函数可以写为:

6.2.2 变量

Verilog学习笔记--运算符与阻塞非阻塞语句

verilog中的位运算符,缩位运算符和逻辑运算符的说明

1,位运算符

按位运算的运算符是位运算符,原来的操作数有几位,结果就有几位,若两个操作数位数不同,则位数短的操作数左端会自动补0(两个数右端对齐,位数少的操作数会在相应的高位补0)。

(1),按位取反:~

(2),按位与:&

(3),按位或:|

(4),按位异或:^

(5),按位同或:^~或~^

2,缩位运算符(又称归约运算符)

缩位运算符是单目运算符,按位进行逻辑运算,结果是一位值!

(1),与缩位运算符:&

(2),或缩位运算符:|

(3),异或缩位运算符:^

(4),与,或,异或运算符和非运算符组成的复合运算符:~&,~|,~^

3,逻辑运算符(逻辑关系运算)

(1),逻辑与:&&

(2),逻辑或:||

(3),逻辑非:!

其中,逻辑与和逻辑或是双目运算符,逻辑非是单目运算符。

如果操作数是多位的,则将操作数看做整体,若操作数中每一位都是0值则为逻辑0值,若操作数当中有1,则做位逻辑1值。

4,相等与全等运算符

(1),==

(2),!=

(3),===

(4),!==

== 、!= 、===、!== 符号之间不能有空格。

“==”和“!=”称作逻辑等式运算符,其结果由两个操作数的值决定。

由于操作数可能是x或z,其结果可能为x;

“===”和“!==”常用于case表达式的判别,又称作cae等式运算符。

其结果只为0和1.如果操作数中存在x和z,那么操作数必须完全相同结果才为1,否则为0.

逻辑等式运算符和case等式运算符的区别:。

FPGA笔记之verilog语言(基础语法篇)

FPGA笔记之verilog语言(基础语法篇)笔记之verilog语言(基础语法篇)写在前面:verilogHDL语言是面对硬件的语言,换句话说,就是用语言的形式来描述硬件线路。

因此与等软件语言不同,假如想要在实际的中实现,那么在举行verilog语言编写时,就需要提前有个硬件电路的构思和主意,同时,在编写verilog语言时,应当采纳可综合的语句和结构。

1. verilog 的基础结构1.1 verilog设计的基本单元——module在数字电路中,我们经常把一些复杂的电路或者具有特定功能的电路封装起来作为一个模块用法。

以后在运用这种模块化的封装时,我们只需要知道:1.模块的输入是什么;2.模块的输出是什么;3.什么样的输入对应什么样的输出。

而中间输入是经过什么样的电路转化为输出就不是我们在用法时需要特殊重视的问题。

当无数个这样的模块互相组合,就能构成一个系统,解决一些复杂的问题。

verilog语言的基础结构就是基于这种思想。

verilog中最基本的模块是module,就可以看做是一个封装好的模块,我们用verilog来写无数个基本模块,然后再用verilog描述多个模块之间的接线方式等,将多个模块组合得到一个系统。

那么一个module应当具有哪些要素呢?首先对于一个module,我们应当设计好其各个I/O,以及每个I/O的性质,用于与模块外部的信号相联系,让用法者知道如何连线。

第二,作为开发者,我们需要自己设计模块内部的线路来实现所需要的功能。

因此需要对模块内部浮现的变量举行声明,同时通过语句、代码块等实现模块的功能。

综上所述,我们把一个module分成以下五个部分:模块名端口定义I/O解释第1页共9页。

verilog知识点总结

verilog知识点总结Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统,它广泛应用于数字系统设计和仿真领域。

本文将总结一些Verilog 的重要知识点,以帮助读者更好地理解和应用Verilog。

一、Verilog的基本语法Verilog的基本语法包括模块声明、端口声明、信号声明、数据类型、运算符等。

Verilog中的模块是设计的基本单元,模块声明包括模块名和端口声明。

端口可以是输入、输出或双向的。

信号声明用于定义内部信号,可以是寄存器或线网类型。

Verilog支持多种数据类型,包括整数、浮点数、向量、数组等。

Verilog还提供了丰富的运算符,包括算术运算符、逻辑运算符、位运算符等。

二、组合逻辑电路描述Verilog可以用来描述各种组合逻辑电路,如与门、或门、非门等。

通过使用逻辑运算符和条件语句,可以很方便地描述组合逻辑电路的功能。

Verilog还提供了多种语法结构,如if语句、case语句等,用于描述复杂的逻辑功能。

三、时序逻辑电路描述时序逻辑电路是一种带有状态的电路,Verilog可以用来描述各种时序逻辑电路,如触发器、计数器、状态机等。

通过使用时钟信号和触发器,可以实现电路的时序行为。

Verilog提供了多种触发器类型,如D触发器、JK触发器、T触发器等,可以根据实际需求选择合适的触发器类型。

四、模块实例化和层次化设计Verilog支持模块的实例化和层次化设计,可以将一个模块实例化为另一个模块的一部分。

通过模块实例化,可以方便地实现模块的复用和层次化设计。

层次化设计可以使整个系统更加清晰和模块化,方便调试和维护。

五、仿真和验证Verilog可以用于对设计进行仿真和验证,以确保设计的正确性。

Verilog提供了仿真器,可以对设计进行时序仿真和波形查看。

通过仿真,可以验证设计的功能和时序行为是否符合要求。

Verilog 还支持测试向量的生成和自动验证,可以自动生成测试向量并进行自动验证。

Verilog入门教程笔记

将编码后的信号还原成原始信号,常用于数据解压缩和控制信号生成。例如, 将3个输入信号译码成8个输出信号的3-8译码器。

多路选择器设计实例

多路选择器(Multiplexer)

根据选择信号从多个输入信号中选择一个输出,常用于数据选择和路由。例如,2选1 多路选择器、4选1多路选择器等。

明确CPU需要实现哪些指令集,具备哪些功能,以及达到什么样的性 能指标。

选择合适的架构

根据需求和性能指标,选择适合的CPU架构,如RISC或CISC。

设计指令集

根据所选架构,设计相应的指令集,包括指令格式、操作码、寻址方 式等。

规划寄存器组

设计寄存器组,包括通用寄存器、特殊功能寄存器等,以满足指令执 行和数据存储的需求。

03

组合逻辑电路设计

基本门电路实现方法

01

02

03

04

05

与门(AND Gate)或门(OR Gate) 非门(NOT Gate)与非门(NAND 或非门(NOR

Ga…

Gat…

实现逻辑与操作,当所有输 入为高电平时输出高电平。

实现逻辑或操作,当任一输 入为高电平时输出高电平。

实现逻辑非操作,将输入信 号取反后输出。

实现二进制数的减法运算,可 以通过加法器和取反器来实现。

实现二进制数的乘法运算,通 常采用逐位相乘再相加的方式 实现。

实现二进制数的除法运算,通 常采用逐位相除再减去的方式 实现,也可以使用更高效的算 法如SRT除法算法等。

04

时序逻辑电路设计

触发器类型及特点介绍

RS触发器

具有置0、置1和保持功能,是基 本存储单元。

数字电路的设计。

发展历程

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

学习Verilog HDL简谈

学习是一个慢长的过程不是一朝一夕的事情。

我坚信自学是最好的老师。

无论我们学什么都要有一个信心与奋斗目标。

现在接合自己的真实的体会简谈一下学习Verilog HDL语言一些注意事项。

希望对新上手学习Verilog HDL有一定的帮助。

我接触EDA设计主要是FPGA方面的。

可以这样说对一个大专的学生来说是很难的从事这个方面的学习的。

因为我们不仅要掌握硬件电路和软件设计知识而且还要拥有数字信号处理、系统分析、较强的高数知识。

特别是在设计FPGA应用玩是无线通信领域时,对这方面的要求更高,此时我们也要掌握别一个数学工具软件就是矩形实验室软件(AMTLAB)的运用。

而这些课程都是在本科高年级才开设的。

如果我们想要从事这方面的设计就要慢慢的努力自学对与我一样的大专生来说。

说到此就给大家推荐一个网址。

在这个网站上有许多的教学视频,软件和文档资料都是免费的。

比如说我们EDA所设计的软件知料几乎都可以找到在这个上面。

我是在学习VHDL和C语言后,接触这门语言的。

说所以说,我就接合这三种语言来谈它们的基本区别思路。

我们在做任何系统设计时候,都要先学会硬件电路的规划。

这里就不谈这个,我们常用的就是自己购买的实验开发板。

如果自己做,有一点困难。

主要是没有相关的设备。

比如说我们学校吧,做PCB板就只可以做单面的。

而EDA项目板都采用的是双层以上的板设计。

如

果拿到工厂去就是很贵了,接下来就是焊接了,这方面也是一个难点,FPGA/CPLD/DSP这些元件的管脚都很多的。

因此建议新手去买开发板。

一个好的开发板就可以省去你做实验和开发项目许多的时间。

我就说这样一个例子吧!上一学期,我们做实习项目就是一个多人抢答器。

因为自己比较了解自己的实验板,所以说就按照自己硬件资源设计但是结果是程序很长,调试不方便。

主要原因就是资源不足,不足就要想办法弥补。

这就增加了困难和延长了时间。

最后老师让我用学校的因资源充足所以代码也少许。

最后只有我与另一个同学成功完成了这个项目的设计且实习老师打出了98分的高分。

我说这个意思就是我们在做项目设计首先要规划好的硬件电路,我们编程出来的结果最终是在硬件电路上实现的。

在那个时候,我们只能够修改程序来适应硬件电路。

我们无论学习VHDL和Verilog HDL设计还是阅读他们的程序时候,我们头脑第一反映就要有一个模块形状。

简说就是一块集成块,有多少个管脚,哪些输入和输出,每个有什么作用有一个整体的把握。

说起模块,我就再多说一点。

我们在学习硬件电路的设计为了以后的工作,我们就必须要对这两种语言熟练一种,了解一种。

这就要看个人的喜好了。

一个项目的设计都是与多人的合作的成果。

为了便宜与团队工作就必须要这样的。

这也是我最后接触Verilog HDL的原因。

在学习这门语言基本就是要把握思路。

在心中要劳记一些结构。

如定义一个任务的结构如下:

task 任务名

定义端口类型(如input ,output ,inout)

数据类型(如reg,wire,parameter)

任务体(常用块语言begin………end和fork……………..join)

endtask

要区别C,VHDL ,与Verilog HDL的区别。

如:在C语言中有这样的形式if(a>b) y=1;和if if(a>b) y=1;else y=0;在C语言中就是相等的。

但是在Verilog HDL就是的,因为前者要引起竟争就会产生x输出。

我们在VHDL中也这样说到,为了避免产生多的寄存器也不用这种少else 的。

我们学习要学会正迁引。

要常常总结才能更好的掌握其区别的。

符号的区别。

在预编译时有这样一个符号“’”我们在书上看如’define。

但是一定要记住我们在写程序的时候,不是这个符号而是这个符号“`”如`define。

这个符号键位于ESC键正下方那个。

当初我也犯了这样的一个错误。

真值表的记忆要找规律。

如“==”和“|”真值表。

== 0 1 x z

0 1 x x x

1 x 1 x x

X x x 0 x

Z x x x 0

| 0 1 x z

0 x 1 x x

1 1 1 1 1

X x 1 x x

Z x 1 x x

以上的规律我相信大家会看出来吧。

与的规律只要有1两者之一,就为1,其他都是未知x。

最后给大家推荐两本书。

VHDL学习可以看一看由电子工业出版社出版的《VHDL数字电路设计教程》,由Volinei A.Pedroni著的。

而Verilog HDL可以看一看《Verilog HDL与数字电路设计》由王冠编的。

以上是自己的体会,有什么不足的还请朋友了解给予指出。

我还是一在校的大专生。