Cadence SPB使用经验总结

Cadence SPB开发平台在EDA实践教学中的应用

图2 反 相 运 算 放 大 器 电 路

●● ● ● ● 一 ●●●

了EDA的 丰 H 火 课程 , 通 过 该 课 程 的学 习 , 可 使 学 生 系统 掌 握 现 代 电子 设 计 方 法 。 提 高学 生 的 ] 程 应川 实践 能力 。 利, q J E D A 技 术 领 域 的C A D 通 川 软 件 包 ,可 以辅 助 进 行 I C 设汁、 电 子 电 路 设 汁和 P CB( F ' r i n t e d C i r c u i t B o a r d, 印刷电路板 ) 设 计 等 方 l l i 『 的设 汁 ] 作 , 主要 包 括 电子 系统 的设 计 、 分 析 和 仿 真 及 印刷 线 路 板 的设 计 方 面 内容 。目前 , 大 部 分 高 校 主 要

图1 P s p i c e  ̄ 真 分 析 过 程 打 ̄O r C A D C a p t u r e 软 件 包 绘 制 如 图2 所 爪 反 相 放 大 电 路 图, 图 巾电源及接地属 7 : S o u r c e  ̄ : 型库 , 电 阻 于 A n a h l g  ̄ 型 库, 运 算放大 器u A 7 4I 属 T Op a m 型库 , 相 火 设 置 参 数 如

钳‘ 对 基 于大 规模 可编 程 逻 辑 器 件 的 数 字 系 统 的设 计 开设 了 相 关 粜 程, 对可编程逻辑器件 、 硬 件 描 述 语 言 及 相 关 软 件 开 发 T 具 的使 川 进 行 了教 学 。 一 些 应 H { 型 背 景 较 强 的学 校 则开 设 了

电 了线 路 C AI ) 的卡 ¨ 火 课程 ( 如 “ 印 刷 电路 板 原 理 图 与P CB设 汁” ) , 但大f } I 5 分院校使门 J 的 教 学 平 俞 主 要 是 基 于 澳 大 利 亚A 1 . 1 i u m 公 司 的设 计  ̄A h i u n l D e s i g n e r c 。 C a d e n c e S P B 开 发 平 台是 美 国 C a d e n c e 公 司新 一 代 的 系 统

Cadence spb16.3学习笔记3__封装

Cadence学习笔记3__封装IPC软件计算后导出下面是STM32F103RCT6(64脚QFP封装)数据手册的封装尺寸:STM32F103xC, STM32F103xD, STM32F103xE Package characteristicsFigure 71. LQFP64 – 10 x 10 mm 64 pin low-profile Figure 72. Recommended footprintTable 72. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data然后打开IPC,在Calculate中打开SMD Calculator,选择QFP封装,双击或者点击ok,出现计算界面,如下图:此时在左侧窗口填上相应的数据,然后光标停在任意一个数据中回车,就可以计算出其余的尺寸了。

注意到这里的单位是毫米Millimeters,所以应该对应数据手册中的毫米而不是英尺。

Pitch(P)在图中是引脚中心的间距,对应于数据手册中的e,值为0.5。

A和B分别是两个方向上的引脚数量,都是16,下面给出了提示,如果是矩形芯片的话,A应该小于B。

Pin Count(for search)是引脚总数,填64。

L1和L2表示包括引脚的芯片宽度和长度,对应芯片手册的D和E,最小值是11.8,最大值是12.2。

T是引脚长度,对应于数据手册中的L,最小值为0.45,最大值为0.75。

W表示焊盘的宽度,对应于数据手册中的b,最小值为0.17,最大值为0.27。

A和B表示不包括引脚的芯片宽度和长度,对应芯片手册的D1和E1,最小值为9.8,最大值为10.2。

H表示芯片的高度,对应于芯片手册中的A,最大值为1.6,不用填最小值。

K表示芯片离PCB板的高度,对应于芯片手册中的A1,最小值为0.05,不用填最大值。

填完之后光标放在任意一个框中回车,就可以计算出其余的数据了。

Cadence SPB v16.2 安装及完整破解详细说明

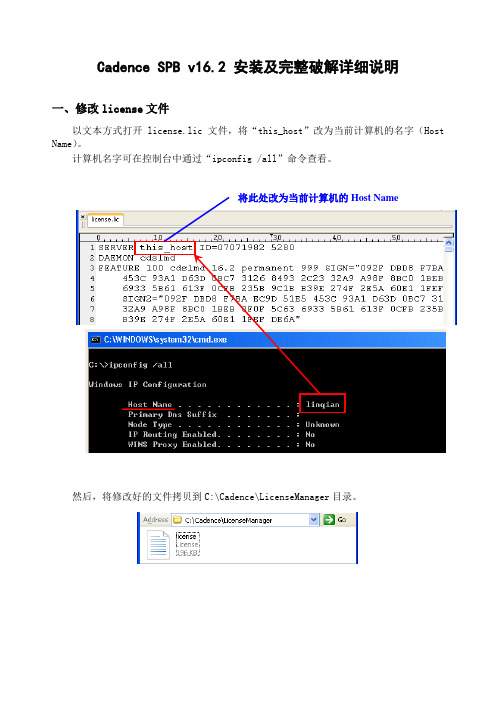

Cadence SPB v16.2 安装及完整破解详细说明一、修改license 文件以文本方式打开license.lic 文件,将“this_host ”改为当前计算机的名字(Host Name )。

计算机名字可在控制台中通过“ipconfig /all ”命令查看。

然后,将修改好的文件拷贝到C:\Cadence\LicenseManager 目录。

Host Name二、准备安装程序Cadence SPB v16.2共有三张安装光盘,将所有安装文件解压到同一目录下,分别对应\Disk1、\Disk2、\Disk3三个独立文件夹。

三、安装License Manager双击setup.exe,启动安装向导。

选择安装License Manager。

安装过程会提示选择License文件,选择先前修改好的那个license.lic。

在License Server Data中的Port Number框内,保留“5280”即可;但本身可能会在数字后留有若干空格,必须将这些空格删除,否则点“Next”会报错。

License Manager安装成功后,可以看到在license.lic文件中修改过的计算机名。

启动LmTool工具来设定License Manager。

在Service/License File选项卡中选择“Configuration using Services”。

在Config Services选项卡中的Path to the license file框中载入先前修改过的license.lic文件。

点击“Save Service”并确认保存。

在Start/Stop/Reread选项卡中可启动或停止License Manager服务。

软件正常工作时要保证服务处于启动状态。

四、正式安装Cadence套件在安装向导中选择“Product Installation”。

建议在安装前关闭所有的杀毒软件和防火墙,否则有些配置文件无法写入。

(整理)Cadence_SPB16.2入门教程——PCB布线.

Cadence_SPB16.2入门教程——PCB布线(一)PCB布线4.1 PCB层叠结构层叠结构是一个非常重要的问题,不可忽视,一般选择层叠结构考虑以下原则:·元件面下面(第二层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;·所有信号层尽可能与地平面相邻;·尽量避免两信号层直接相邻;·主电源尽可能与其对应地相邻;·兼顾层压结构对称。

对于母板的层排布,现有母板很难控制平行长距离布线,对于板级工作频率在 50MHZ以上的(50MHZ以下的情况可参照,适当放宽),建议排布原则:·元件面、焊接面为完整的地平面(屏蔽);·无相邻平行布线层;·所有信号层尽可能与地平面相邻;·关键信号与地层相邻,不跨分割区。

基于以上原则,对于一个四层板,优先考虑的层叠结构应该是:·S ←信号·G ←地平面·P ←电源层·S ←信号对于一个六层板,最优的层叠结构是:·S1 ←信号·G1 ←地平面·S2 ←信号·G2 ←地平面·P ←电源层·S4 ←信号对于一个八层板,有两种方案:方案 1:方案2:·S1 ←信号S1 ←信号·G1 ←地平面G1 ←地平面·S2 ←信号S2 ←信号·G2 ←地平面P1 ←电源层·P ←电源层G2 ←地平面·S3 ←信号S3 ←信号·G3 ←地平面P2 ←电源层·S4 ←信号S4 ←信号方案2主要是比方案1多了一个电源层,在电源比较多的情况下可以选择方案2。

对于更多层的结构也是按照上面的原则来定,可以参考其它的资料。

下面以SMDK6410核心板(设计为八层板)来设置层叠结构,包括规则设置,PCB布线等。

打开程序->Cadence SPB 16.2->PCB Editor,然后打开在第3 章布局好的PCB文件。

Cadence_SPB16.2入门教程——建立封装

Cadence_SPB16.2入门教程——建立封装零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置,是纯粹的空间概念。

因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装。

像电阻,有传统的针插式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD)这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD元件放上,即可焊接在电路板上了。

Cadence_SPB16.2入门教程——焊盘制作建立封装2.1 新建封装文件用Allegro来演示做一个K4X51163内存芯片的封装。

打开程序->Cadence SPB 16.2->PCB Editor,选择File->New,弹出新建设计对话框,如图2.1所示。

图2.1 新建封装在Drawing Type列表框中选择Package symbol,然后点击Browse按钮,选择保存的路径并输入文件名,如图2.2所示。

图2.2 选择保存封装的路径点击打开回到New Drawing对话框,点击OK退出。

就会自动生成一个bga63.dra的封装文件。

点击保存文件。

2.2 设置库路径在画封装之前需要在Allegro设置正确的库路径,以便能正确调出做好的焊盘或者其它符号。

打开之前建立的封装文件bga63.dra,选择Setup->User Preferences,如图2.3所示。

图2.3 设置路径弹出User Preferences Editor对话框,如图2.4所示。

图2.4 User Preferences Editors对话框点击Paths前面的‘+’号展开来,再点击Library,现在只需要设置两个地方就可以了,padpath(焊盘路径)和psmpath(封装路径)。

点击padpath 右边Value列的按钮。

弹出padpath Items对话框,如图2.5所示。

Cadence_SPB16.2中文教程

2

图 1.3 表贴元件焊盘设置

如果是通孔焊盘,需要填写的参数有: BEGINLAYER 层的 Regular Pad,Thermal Relief,Anti Pad; DEFAULTINTERNAL 层的 Regular Pad,Thermal Relief,Anti Pad; ENDLAYER 层的 Regular Pad,Thermal Relief,Anti Pad; SOLDEMASK_TOP 层的 Regular Pad; PASTEMASK_TOP 层的 Regular Pad。 如图 1.4 所示。 在 BEGINLAYER、DEFAULTINTERNAL、ENDLAYER 三个层面中的 Thermal Relief 可以 选择系统提供的默认连接方式,即 Circle、Square、Oblong、Rectangle、Octagon 五种,在 PCB 中这几种连接方式为简单的‘+’形或者‘X’形。也可以选用自己画的热风焊盘连接 方式,即选择 Flash。这需要事先做好一个 Flash 文件(见第二节)。这些参数的设置见下面的 介绍。

第 2 章 建立封装 .......................................................................................................10

第 3 章 元器件布局 ...................................................................................................23

第 5 章 输出底片文件 ...............................................................................................70

Cadence SPB 16.5 学习中注意点

一、焊盘显示1、焊盘的填充显示及钻孔显示在系统的默认下,焊盘是填充显示、钻孔是不显示的,要修改显示在Setup->Design Paraneter ->在弹出的对话框中选择Display ->Enhanced display modes 勾选Dispaly ppated holes Display non-plated holes Display padless holes,这三项是显示钻孔。

去掉Filled pads 前面的勾就可以使焊盘不填充。

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~END~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ~~~~~~~~~~~~~~~~~~~~~~~~二、Allegro PCB文件更新封装及单个焊盘修改方法1、PCB文件更新封装打开brd文件,选择菜单中的Place->Update Symbols, 选择需要更新封装的元件,把“Package symbols”“ Shape and flash symbols”“Update symbol padstacks” 等选项都选上,点击Refresh即完成封装更新。

2、单个焊盘修改选中焊盘右键“Replace Padstack”->“Selected instance(s)“ 在弹出的“Select a padstack”对话框中选择新的焊盘。

三、Allegro PCB Design创建区域约束规则方法在打开电路板后,1、打开规则约束管理器“setup”->>“constraints”->>“constraint manager”,打开物理约束“physical”->>“Region”->>“All Layers”,创建区域物理约束“Objects”->>“Create”->>“Region” 在弹出的对话框中输入约束区域名字“OK” ,在“Referenced physical CSet”中选择物理约束。

Cadence SPB 16.5 学习中注意点

一、焊盘显示1、焊盘的填充显示及钻孔显示在系统的默认下,焊盘是填充显示、钻孔是不显示的,要修改显示在Setup->Design Paraneter ->在弹出的对话框中选择Display ->Enhanced display modes 勾选Dispaly ppated holes Display non-plated holes Display padless holes,这三项是显示钻孔。

去掉Filled pads 前面的勾就可以使焊盘不填充。

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~END~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ~~~~~~~~~~~~~~~~~~~~~~~~二、Allegro PCB文件更新封装及单个焊盘修改方法1、PCB文件更新封装打开brd文件,选择菜单中的Place->Update Symbols, 选择需要更新封装的元件,把“Package symbols”“ Shape and flash symbols”“Update symbol padstacks” 等选项都选上,点击Refresh即完成封装更新。

2、单个焊盘修改选中焊盘右键“Replace Padstack”->“Selected instance(s)“ 在弹出的“Select a padstack”对话框中选择新的焊盘。

三、Allegro PCB Design创建区域约束规则方法在打开电路板后,1、打开规则约束管理器“setup”->>“constraints”->>“constraint manager”,打开物理约束“physical”->>“Region”->>“All Layers”,创建区域物理约束“Objects”->>“Create”->>“Region” 在弹出的对话框中输入约束区域名字“OK” ,在“Referenced physical CSet”中选择物理约束。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cadence SPB使用方法1.在用OrCad Capture CIS画电路原理图时,不同电路图页面之间的信号互联,单信号线(wire)用分页端口连接器(Off Page Connector)实现互联,总线(Bus)用端口(Port)实现互连(也可以用分页端口连接器(Off Page Connector))。

2.特别注意:在FPGA原理图设计中,在为FPGA设计原理图符号时,一般要将FPGA分为多个部分,这时一定要注意在管脚功能划分时,要将Bank2中用于配置的管脚,包括:配置模式选择管脚M0、M1,CCLK,DIN,INIT_B等与TMS,TCK,TDO,TDI 等一起划分到FPGA的配置(Configuration)部分。

3.在OrCad Capture CIS中制作原理图符号时,如果器件有多个(两个以上)管脚名称(pin name)相同,在保存该元件时就会弹出以下警告信息:因为ORCAD的封装(原理图符号)是有规则的,只有管脚为POWER属性才能同名,比如VCC,GND的管脚名等等,很好理解,这些属性在画PCB的时候默认的是同一个网络,是要连接在一起的,如GND连GND,VCC连VCC,有时候有很多的空脚NC 最好用NC1,NC2...来描述,避免不必要的错误,有的甚至连POWER属性的管脚名都不做重复的。

如果忽略这些这些警告信息,则当使用这些元件符号画电路图,在生成网表(Create Netlist)时就会产生错误:#79 Error [ALG0050] Duplicate Pin Name "SW" found on Package LM2852Y , U21 Pin Number 9: SCHEMATIC1, POWER SUPLLY (1.80, 3.20). Please renumber one of these.这时选中设计,可以利用accessories菜单的libcorrectionutil->library verification / correction来批量修改重复管脚定义(即:批量把重复的管脚名改为不同)。

(accessories->libcorrectionutil->library verification / correction)但是通过这种方法只能修改元件库Library中的元件,不能更新到原理图页面中。

如图所示,选中Duplicate Pin Names复选框。

当然也可以手动把重复管脚名称改过来,即加数字编号:1,2,3……。

或者把重复管脚名称管脚的属性改为POWER,因为CIS里面只允许POWER属性的管脚同名。

出现这个问题,另外一个可能的原因是因为制作元件时Part name和Part number混了。

于其后期出现了问题再修改,就不如在最初设计原理图符号时就把问题解决了,即:要把Pin Name改成互不相同,如加上0,1,2,3...的编號,例如:NC1,NC2,NC3……,等,还有Pin Number不可为空或者为0。

总之,allegro的netlist不能有相同的管脚名,除了power类型的管脚。

在做零件的過程,可以先將vcc或vss設成power pin,這樣了,既使都叫vcc 也不會有問題。

但是如果是I/O, 建議你乖乖的給它名字,要不然它可是不會讓你轉net lists的。

#79 Error [ALG0050] Duplicate Pin Name "SW" found on Package LM2852Y , U21 Pin Number 9: SCHEMATIC1, POWER SUPLLY (1.80, 3.20). Please renumber one of these.这个意思是说,你的原理图VDD 有重复的名字,处理方法点上这个U21,点右键.出现 EDIT PART ,把VDD有些重复的改成VDD1,VDD2,还有些GND 改成GND1 .这样操作了是更新了图上的器件的引脚,怎么给它更新到库里呢?编辑完成后,关闭对话框,会弹出信息问你要不要更新。

你可以选择更新当前或所有同样的封装。

要想保存到库里去,防止以后现有这样的事发生:1 你编辑好以后关悼对话框,你先更新所有的吧;2 编辑好之后.到原理图看下图操作。

如果你要更新你库文件里的,可以在DESIGN Cache里面复制你更新的封装,粘贴到你的库文件复盖你的原封装就行了。

每个Part的Pin Name是不可以重复的,你要修改一下的。

只有当他们的Type为Power时才可以重复。

如果在前期原理图符号设计中忽略了重复管脚的问题,在出现错误时,在原理图中修改错误的最简捷的处理方法如下例所示:#1 Error [ALG0050] Duplicate Pin Name "PVIN" found on Package LM20123MH , U22 Pin Number 7: SCHEMATIC1, POWER SUPLLY (6.60, 4.00). Please renumber one of these.错误信息提示,U22 Pin Number 7为Duplicate Pin Name "PVIN",则在相应的原理图页面找到该元件U22,选中它。

单击鼠标右键,在弹出菜单中选择Edit Part,打开元件编辑页面,按住Ctrl键选中所有重复名称的管脚(Duplicate Pin Name),点击右键选择Edit Properties,弹出管脚属性编辑窗口:给其中的重复管脚重新命名,编号。

单击OK按钮关闭,关闭Part Edit窗口:在弹出的Save Part Instance提示窗口中,选择Update All,其余两个提示都选YES,更新全部,则在原理图中的所有元件都得到更新。

4.Orcad Capture CIS中原理图符号的管脚编号(Pin Number而不是管脚名称Pin Name)与Allegro PCB Design中的PCB封装管脚相对应。

例如:与就不能匹配,PCB封装是以字母开头编号的,所以要把原理图封装的管脚编号与管脚名称改为一致。

其实在原理图元件符号设计中,管脚名只是用作用户识别,并不起与PCB封装管脚对应的作用。

5.每次替换元件,包括把原理图中原来的元件删除,再重新放置,都要使用Tools->Annnotate,对设计重新编号。

负责软件认为是放置了一个元件的两个部分,从而产生Error[ALG0045]错误。

6.在Orcad Capture CIS原理图生成元件清单时,从菜单Reports->CIS Bill ofMaterials->Standard生成的元件清单和点击工具栏的“Bill of materials”图标生成的元件清单是不同的,通过后者生成的元件清单包括每种具有相同元件值和相同封装的同种元件的个数。

在实际中更实用些。

利用后种方法生成元件清单时的设置:在其中输入:Header:Item\tQuantity\tReference\tPart\PCB FootprintCombined property string:{Item}\t{Quantity}\t{Reference}\t{Value}\t{PCB Footprint} 生成的元件清单:7.可以在库文件夹下直接右击“Rename”元件。

在Cache中用库中修改后的元件Replace原来的元件。

8.在用Orcad Capture CIS设计元件符号,给元件管脚命名(Pin Name)时,不能用以下符号:/ ; ! < > : \ " , *。

而且不能出现同名的管脚。

同名管脚加数字1,2,3……来区分,最好是用#1,#2,#3来区分,这样就知道是同一个地上的不同引脚,如果用1,2,3来分的话,DATA1,DATA2,DATA3,它也是用1,2,3来分的,名字也都是data,但不是同一网络。

Cadence的Help文档:(1)Whenever appropriate the input pins should be placed on the left side of the symbol with outputs on the right.(2)Pin NamingPins should be designated with functional names. Each pin name mustbe unique to that symbol and must have a matching entry in thechips.prt file. Typically, a pin name must be alphanumeric, but youcan have numbers as pin names for scalar pins. The other charactersthat are supported . by Design Entry HDL as valid characters in pinnames are as follows: - # $ % + = | ? ^ _ . ( ) .The following are not valid for pin names:All extended character sets / ; ! < > : \ " , *.When creating parts manually, place the SIG_NAME properties outside the symbol, next to the pin it is attached to. Text size is not too important on these properties since they are not displayed on the schematic.Follow low asserted pin names with an asterisk (*) (for example, OE*) or _N (for example OE_N). Do not differentiate low asserted pins with anyother nomenclature. All low asserted pins should appear as bubbles and not straight pin stubs.9.在使用PCB Editor设计PCB时,在放置(Place)元件之前,要确定PCB在波峰焊或者回流焊时的移动方向,尤其是贴片元件SMD,要使其两侧焊盘的连线与焊接时PCB的移动方向相垂直,从而可以确定元件的放置方向,然后选择Setup—>Design Parameters在Design Parameter Editor窗口的Design选项卡中的Symbol选项中设置元件的放置角度。