七进制计数器

采用74LS192设计的4、7进制计数器

采用74LS192设计的4、7进制计数器《电子设计基础》课程报告设计题目:4/7进制计数器设计学生班级:通信0902学生学号:20095972学生姓名:指导教师:时间:2011. 6.24西南科技大学信息工程学院四、74283加法器每一位的进位信号送给高位作为输入信号,因此,任一位的加法运算必须在低一位的运算完成之后才能进行,这种进位方式成为串行进位,这种加法器的逻辑电路较为简单。

74283管脚图74283原理图一.电路设计及计算1.选择一个方波信号发生器作为输入信号源;CP2利用74LS192,通过清零法设计一个四进制计数器,状态图如下:0000 000101000011 00103、利用74S192通过置数法设计一个从1到7的计数器,状态图如下:0010 0011 0111 0110 0101 0100然后通过减法器在每一个状态的基础上减去一个1,从而实现一个7进制计数器。

减法器电路如图所示U774283NSUM_410SUM_313SUM_14SUM_21C49B411A412B315A314B22A23B16A15C07U8A74LS136D U9B 74LS136DU10C74LS136D U11D74LS136D GNDVCC 5V4、通过一个单刀双掷开关控制信号源,从而进行四进制和七进制之间的转换。

接4进制计数器接7进制计数器接地5、进行四进制计数时,在74LS192后面接一个7447显示译码管,将8421BCD 码转换成十进制,最后通过一个七段显示数码管来显示数据输出状态。

6、在进行七进制计数时,用40192进行置数法计数,预置数为0001,计数到1000后反馈到置数端,循环计数,后面接一个74238加法器构成的减法器,使输出显示数字在0000~0110之间计数,在经过7447译码管将其转化为十进制数0~6,从而实现七进制计数器功能。

五、原理图、仿真图及结果分析、PCB版图原理图如下所示:仿真及结果分析MULTISIM仿真图四进制波形七进制波形PCB板排布2.PCB原理图如下:PCB顶层PCB底层总结:完成这次课程设计之后,我觉得自己在电子设计过程中收获了很多,在这过程中我遇到了很多困难:在电路仿真时候,我觉得原理图是正确的,但运行不出想要的结果,我把74LS192换成了同样是计数器的74LS161,结果可以实现4、7进制的转换,于是我认为时芯片出了问题,找到老师说明了我的问题后,才知道是这个芯片本身特点,要根据它自身的性质来修改原理图;还有,接地的标号中要把Net选项选为GND,不然在PCB制作中将没有接地这一个选项出现;在PCB板制作时,要对元器件不断调整位置来使排版最佳。

同步七进制加法计数器状态转换表

同步七进制加法计数器状态转换表摘要:1.同步七进制加法计数器的基本概念2.状态转换表的定义和作用3.同步七进制加法计数器状态转换表的构建方法4.同步七进制加法计数器状态转换表的应用实例正文:一、同步七进制加法计数器的基本概念同步七进制加法计数器是一种计数器,它的计数方式是基于七进制数制的加法原理。

在计数过程中,每当计数值达到7 时,计数器就会产生一个进位信号,同时将计数值清零。

同步七进制加法计数器广泛应用于数字电路、计算机科学等领域。

二、状态转换表的定义和作用状态转换表是一种用于描述计数器状态转换的表格,它将计数器的所有可能状态及其对应的输入信号和输出信号都列出来。

通过状态转换表,我们可以清晰地了解计数器的工作原理和状态变化规律。

在实际应用中,状态转换表有助于分析和设计计数器电路,也可以用来验证计数器的正确性。

三、同步七进制加法计数器状态转换表的构建方法构建同步七进制加法计数器状态转换表的方法如下:1.首先,确定计数器的输入信号和输出信号。

输入信号通常包括计数使能信号(如时钟信号)和进位信号;输出信号通常是计数值的表示。

2.其次,根据计数器的工作原理,列出所有可能的状态及其对应的输入信号和输出信号。

对于同步七进制加法计数器,共有7 种状态,分别对应0~6 这七个计数值。

3.最后,将这些信息整理成表格形式,形成状态转换表。

四、同步七进制加法计数器状态转换表的应用实例以下是一个同步七进制加法计数器状态转换表的应用实例:假设有一个同步七进制加法计数器,它的输入信号包括时钟信号(CLK)和进位信号(Carry),输出信号是计数值(Count)。

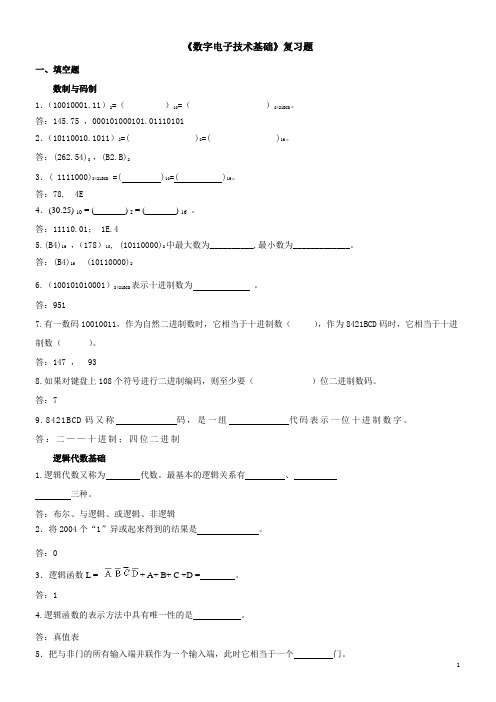

《数字电子技术基础》复习题

10.组成计数器的各个触发器的状态,能在时钟信号到达时同时翻转,它属

于计数器。

答:同步

11.组成计数器的各个触发器的状态,在时钟信号到达时不能同时翻转,它属于计数器。

答:异步

12.两片中规模集成电路10进制计数器串联后,最大计数容量为()位。

答:100

13.驱动共阳极七段数码管的译码器的输出电平为()有效。

A.110 B.001 C.100 D.000

答:B

11.8—3线优先编码器(74LS148)中,8条输入线 ~ 同时有效时,优先级最高为I7线,则 输出线的状态是()

A.000 B.010 C.101 D.111

答:A

12.引起组合逻辑电路中竟争与冒险的原因是()

A.逻辑关系错;B.干扰信号;C.电路延时;D.电源不稳定。

答:D

5.指出下列各式中哪个是四变量A、B、C、D的最小项

A.ABC;B. A+B+C+D;C.ABCD;D. A+B+D

答:C

6.测得某逻辑门输入A、B和输出F的波形如图所示,则F(A,B)的表达式为()

A.F=AB B. F=

C.F= D. F=A⊕B

答:B

7.函数F(A,B,C)=AB+AC的最小项表达式为( )。

答:C

13.一个16选一的数据选择器,其地址输入(选择控制输入)端的个数是()

A.1 B.2 C.4 D.16

答:C

14.半加器和的输出端与输入端的逻辑关系是()

A、与非B、或非C、与或非D、异或

答:D

15.逻辑数F=A +B ,当变量的取值为()时,将出现冒险现象。

A.B=C=1 B.B=C=0 C.A=1,C=0 D.A=0,B=0

同步七进制加法计数器状态转换表

同步七进制加法计数器状态转换表(实用版)目录1.概述2.同步七进制加法计数器的原理3.状态转换表的构成4.状态转换表的解读5.应用示例正文1.概述同步七进制加法计数器是一种数字电路,用于实现七进制数的计数。

与常见的二进制计数器相比,七进制计数器可以更有效地处理七进制数,从而在某些应用场景中具有优势。

本文将介绍同步七进制加法计数器的状态转换表,帮助读者更好地理解和应用这一电路。

2.同步七进制加法计数器的原理同步七进制加法计数器基于七进制数的加法规则,使用四个输入信号(A、B、C、D)表示七进制数的每一位。

计数器有两个输出信号,分别是进位标志 Q 和当前位值 Q0、Q1、Q2、Q3。

当输入信号发生变化时,计数器会根据当前状态进行相应的状态转移,实现七进制数的计数。

3.状态转换表的构成同步七进制加法计数器的状态转换表是一个四行三列的矩阵,其中行表示输入信号的状态(0 或 1),列表示计数器的三位输出(Q0、Q1、Q2)以及进位标志(Q)。

每个矩阵元素对应一个输入信号状态与输出信号状态的组合,通过这个组合可以确定计数器的下一个状态。

4.状态转换表的解读以输入信号 A、B、C、D 和输出信号 Q0、Q1、Q2、Q 为例,我们可以通过状态转换表找到计数器在某个输入信号状态下的下一个状态。

例如,当输入信号 A、B、C、D 分别为 0、1、0、1 时,查找状态转换表可知,计数器将从当前状态转移到状态“110”。

这意味着输出信号 Q 将变为 0,而 Q0、Q1、Q2 将变为 1、0、1。

5.应用示例同步七进制加法计数器广泛应用于计算机科学、通信系统和数字信号处理等领域。

例如,在数字时钟设计中,可以使用同步七进制加法计数器实现七进制计数,从而将时钟信号分成七个等分。

在数字电路设计中,同步七进制加法计数器可以作为基本组件,实现复杂的计数和控制功能。

总之,同步七进制加法计数器的状态转换表是理解该电路工作原理的关键。

EDA技术(机械)实验报告--能自启的七进制计数器

实验报告(计算机类)开课学院及实验室:实验时间:年月曰一、实验目的1.了解VHDL语言编程方法,学会熟练运用quartus软件2.了解如何使用状态机方法设计十三进制计数器二、内容与设计思想1.能自启的七进制计数器的状态转换图2.能自启的七进制计数器引脚图三、使用环境WinXP或win7QUartUSii编程环境四、核心代码及调试过程能自启动的七进制计数器Iibraryieee;useieee.std_Iogic_1164.aII;useieee.std_Iogic_arith.all;useieee.std_Iogic_unsigned.all;entityh34isport(cp:instd_logic; --------------- c IocksignaIq:outstd_Iogic_vector(2downtoO); ------------------------- s tateoutputy:outstd_logic --------------- c arryoutput);endh34;architecturewofh34istypestateisarray(2downto0)ofstd_logic;constantconstantconstantconstantconstantconstantconstantsθ:stateι=,,OOΓ,s1:state:="1OO,,s2:state:="010”s3:state:="101"s4:state:="110"s5:state:="111" s6:state:="011"signaIp:state;signaIn:state;begins:process(cp)beginifcp,eventandcp='1,thenP<=n;endif;endprocesss;m:process(p)begincasepiswhensθ=>n<=s1;y<=,0';q<="100∙,;whens1=>n<=s2;y<=,0';q<="010";whens2=>n<=s3;y<=,0';q<="101";whens3=>n<=s4;y<=,0';q<="110";whens4=>n<=s5;y<=,0';q<=F11";whens5=>n<=s6;y<=,0';q<=>,011";whens6=>n<=sθ;y<=,Γ;q<=1,oor,;whenothers=>n<=sO;y<=,01;endcase;endprocessm;endw;五、总结六、附录(仿真结果)SimulationWaveformsSimulationmod。

七进制加法计数器电路设计

N进制计数器仿真设计

1.设计要求

试分别采用反馈清零和反馈置数的方法,用同步十进制加法计数器74LS160(或同步4位二进制加法计数器74LS161)、三3输入与非门74LS10、4511、共阴七段数码LED显示器、显示电路

2.仪器设备

安装了Muitisim仿真软件、公式编辑器软件的计算机1台

图1 例4.2.5用74LS160反馈清零法构成七进制加法计数器仿真设计电路

图2 例4.2.5用74LS160反馈置数法构成七进制加法计数器仿真设计电路

图3 例4.2.5用74LS161反馈清零法构成七进制加法计数器仿真设计电路

图4 例4.2.5用74LS161反馈置数法构成七进制加法计数器仿真设计电路。

数字电子技术基础自制题库

数字电子技术基础试卷试题1一、单项选择题(每小题1分,共15分)1.一位十六进制数可以用多少位二进制数来表示?( C )A. 1B. 2C. 4D. 16 2.以下电路中常用于总线应用的是( A )A.T S L 门B.O C 门C. 漏极开路门D.C M O S 与非门 3.以下表达式中符合逻辑运算法则的是( D )A.C ·C =C 2B.1+1=10C.0<1D.A +1=1 4.T 触发器的功能是( D )A . 翻转、置“0” B. 保持、置“1” C. 置“1”、置“0” D. 翻转、保持 5. 存储8位二进制信息要多少个触发器(D )A.2B.3C.4D.8 6.多谐振荡器可产生的波形是( B )A.正弦波B.矩形脉冲C.三角波D.锯齿波 7.一个16选一的数据选择器,其地址输入(选择控制输入)端的个 数是( C )A.1B.2C.4D.16 8.引起组合逻辑电路中竟争与冒险的原因是( C )A.逻辑关系错;B.干扰信号;C.电路延时;D.电源不稳定。

9.同步计数器和异步计数器比较,同步计数器的最显著优点是( A ) A.工作速度高 B.触发器利用率高C.电路简单D.不受时钟C P 控制10.N 个触发器可以构成能寄存多少位二进制数码的寄存器?( B ) A.N -1 B.N C.N +1 D.2N11.若用J K 触发器来实现特性方程AB Q A Q n 1n +=+,则J K 端的方程应为( B )A.J =A B ,K =B AB.J =A B ,K =B AC.J =B A +,K =A BD.J =B A ,K =A B12.一个无符号10位数字输入的D A C ,其输出电平的级数是( C )A.4B.10C.1024D.10013.要构成容量为4K ×8的RAM ,需要多少片容量为256×4的RAM ?( D )A.2B.4C.8D.3214.随机存取存储器R A M 中的内容,当电源断掉后又接通,则存储器中的内容将如何变换?( C )A.全部改变B.全部为1C.不确定D.保持不变 15.用555定时器构成单稳态触发器,其输出的脉宽为( B )A.0.7RC ;B.1.1RC ;C.1.4RC ;D.1.8RC ; 二、多项选择题(每小题1分,共5分)16.以下代码中,为无权码的是( C )( D )A. 8421BCD 码B. 5421BCD 码C. 余三码D. 格雷码 17.当三态门输出高阻状态时,以下说法正确的是( A )( B )A.用电压表测量指针不动B.相当于悬空C.电压不高不低D.测量电阻指针不动18.已知F=A B +BD+CDE+A D ,下列结果正确的是哪几个?( A )( C )A.F =D B A +B.F =D B A )(+C.F =))((D B D A ++D.F =))((D B D A ++19.欲使J K 触发器按Q n +1=Q n 工作,可使J K 触发器的输入端为以下哪几种情况?( A )( B )( D )A.J =K =0B.J =Q ,K =QC.J =Q ,K =QD.J =Q ,K =0 20.关于PROM 和PAL 的结构,以下叙述正确的是( A )( D )A.P R O M 的与阵列固定,不可编程B.P R O M 与阵列、或阵列均不可编程C.P A L 与阵列、或阵列均可编程D.P A L 的与阵列可编程 三、判断改错题(每小题2分,共10分)21. 数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

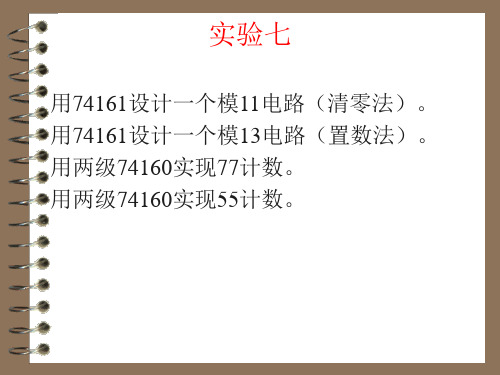

实验报告七

选预置数D3D2D1D0=0000;

写出D5-1的二进制数码:D4=0100;

再根据D4数码写出置数信号表达式: Q2 ; LD

最后根据置数信号表达式画出连线图。

例 用 74LS160的置数法构成七进制加法计数器

741LS60的有效状态是10个状态,在此选后七个状态为循环 计数状态即0011~1001。所以选预置数为:D3D2D1D0=1001 ; 74LS160是同步置数的,选

1) 异步清零:当 RD 0 时,不管其他输入端的状态如何, 不论有无时钟脉冲CP,计数器输出将被直接置零(Q3Q2QlQ0= 0000),称为异步清零。 2) 同步并行预置数:当 RD 1, LD 0 时,在输入时钟脉 冲CP上升沿的作用下,并行输入端的数据d3d2d1d0被置入计数 器的输出端,即Q3Q2QlQ0=d3d2d1d0。由于这个操作要与CP上 升沿同步,所以称为同步预置数。 3)计数功能:当 RD LD EP ET 1 时,在CP端输入 计数脉冲,计数器进行二进制加法计数。 4)保持功能:当 R D LD 1 ,且 EP ET 0 ,即两个 使能端中有0时,则计数器保持原来的状态不变。这时,如 EP=0、ET=1,则进位输出信号CO保持不变;如ET=0则不 管EP状态如何,进位输出信号CO为低电平0。

集成计数器产品多数是二进制和十进制计数器,如果需要其 他进制的计数器,可用现有的二进制或十进制计数器,利用 其清零端或预置数端,外加适当的门电路连接构成任意进制 计数器。如果手边有M进制的集成计数器,要构成N进制的计 数器,当M>N时用一片M进制的计数器就可以实现;当M<N时 则需要多片M进制的计数器下面分别介绍实现的方法。

LD CO ;

最后根据置数信号表达式画出连线图。