详细讲解cmos反相器的原理及特点

清华大学《数字集成电路设计》周润德 第5章 CMOS反相器

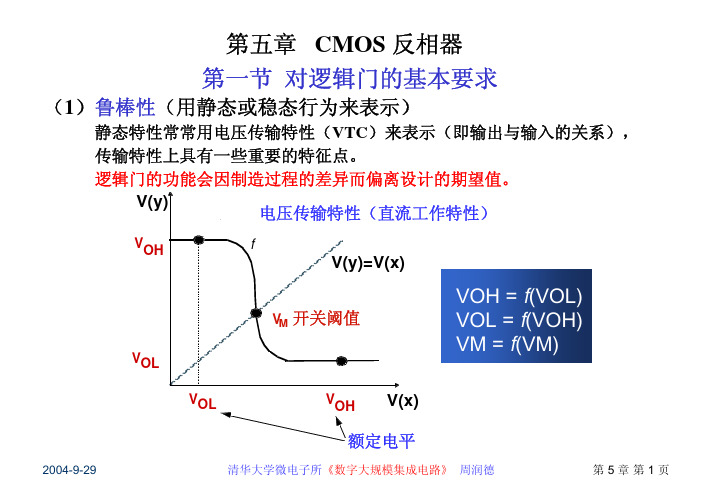

第五章 CMOS 反相器 第一节 对逻辑门的基本要求(1)鲁棒性(用静态或稳态行为来表示)静态特性常常用电压传输特性(VTC)来表示(即输出与输入的关系), 传输特性上具有一些重要的特征点。

逻辑门的功能会因制造过程的差异而偏离设计的期望值。

V(y) 电压传输特性(直流工作特性)VOH fV(y)=V(x)VM开关阈值VOL VOL VOHVOH = f(VOL) VOL = f(VOH) VM = f(VM)V(x)额定电平2004-9-29 清华大学微电子所《数字大规模集成电路》 周润德 第5章第1页(2)噪声容限:芯片内外的噪声会使电路的响应偏离设计的期望值 (电感、电容耦合,电源与地线的噪声)。

一个门对于噪声的敏感程度由噪声容限表示。

可靠性―数字集成电路中的噪声v(t) i(t)V DD电感耦合电容耦合电源线与地线噪声噪声来源: (1)串扰 (2)电源与地线噪声 (3)干扰 (4)失调 应当区分: (1)固定噪声源 (2)比例噪声源 浮空节点比由低阻抗电压源驱动的节点更易受干扰 设计时总的噪声容限分配给所预见的噪声源2004-9-29 清华大学微电子所《数字大规模集成电路》 周润德 第5章第2页噪声容限(Noise Margin)V“1” V OH V IHout OH 斜率 = -1V不确定区 斜率 = -1ILV “0” VVOLOL V IL V IH V in2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第3页噪声容限定义"1"噪声容限(Noise Margin) 容许噪声的限度V IH高电平 噪声容限VOHNM H未定义区 低电平 噪声容限V OL "0" NM L V IL抗噪声能力(Noise Immunity) 抑止噪声的能力门输出门输入2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第4页理想逻辑门V outg=∞Ri = ∞ Ro = 0 Fanout = ∞ NMH = NML = VDD/2V in2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第5页早期的逻辑门5.0 4.0 3.0 2.0 VM 1.0 NM H NM L0.01.02.03.0 V in (V)4.05.02004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第6页(3) “再生”特性:逻辑门的“再生”特性使被干扰的信号能恢复到名义 的逻辑电平。

三态输出的CMOS反相器

BC段: T1 、T2同时导通, 为转折区。

上页 下页 返回

7

3. 电流传输特性

iD

VGS(th)N

VG S(th)P

AB

CD

O

1 2 VDD

v VDD

I

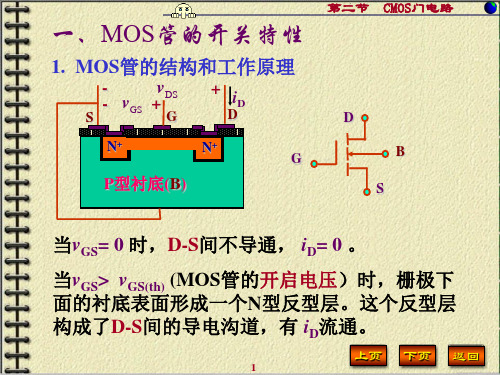

第二节 CMOS门电路

AB段:T2截止 漏极电流几乎为0

CD段:T1截止 漏极电流几乎为0

上页 下页 返回

28

第二节 CMOS门电路

用短沟道、硅栅自对准工艺生产的高速CMOS门电路,

其平均传输延迟时间小于10ns。

高速CMOS门电路的通用系列为54HC/74HC系列。

该系列产品使用+5V电源,

输出的高、低电平与TTL电路兼容。

如54HC/74HC× × ×与54LS/74LS × × × ,

动态功耗 PD = PT + PC 其中PT : T1和T2在短时间内同时导通所产生的瞬时导通功耗。

PC :对负载电容充、放电所消耗的功率。

上页 下页 返回

16

第二节 CMOS门电路

五、其他类型的CMOS门电路

1.其他逻辑功能的CMOS门电路

在CMOS门电路的系列产品中, 除反相器外常用的还有: 与非门、或非门、与门、 或门、与或非门、异或门等几种。

1. 输入特性 因为MOS管的栅极和衬底之间存在输入电容,

绝缘介质又非常薄,极易被击穿,

所以必须采取保护措施。

输入保护电路

VDD

C1

T1

RS

vI

vO

C2

T2

输入保护电路

C1 RS

vI

C2

VDD

第七章MOS 反相器

Vi

CMOS反相器电压传输特性VTC

NMOS截止 PMOS线性 NMOS饱和 PMOS线性

2.5 a 2

b

c

Vout (V)

1.5 1 0.5

d

NMOS饱和 PMOS饱和

0 0 0.5 1 1.5

NMOS线性 PMOS饱和 NMOS线性 e PMOS截止

f

2

2.5

Vin (V)

四、

CMOS反相器VTC分析

MI

2. 电压传输特性曲线的推导

3. 基本特性 VDD VOL 1+2KI RL(VOHVTI) VDD RL RL若小:VOL高, Vo 功耗大, tr小; VOH

Vi

Vo W/L若小(即K I 小):VOL高,功 MN 耗小,t 大。 f

RL减小

VOL 0

VILVIH Vi

7.1.2 E/E饱和负载NMOS反相器 1. 结构和工作原理 VDD ML Vi为低电平VOL时,MI截止,ML饱和 VOH=VDDVTL Vi为高电平VOH时,MI非饱和,ML饱和 KL(VDD-VOL-VTL)2= KI[2(VOH-VTI)VO-VO2] Vo (VDD VTL )2 MI 有比电路 VOL 2R(VOHVTI) (W/L)I KI 其中:R = K = (W/L)L L

VGL

Vi

1. 结构和自举原理(续) VDD VGL 自举过程: Vi 变为VOL ,ME截止,Vo上升, MB VGL随Vo上升(电容自举), ML MB截止,ML逐渐由饱和进入 CB 非饱和导通,上升速度加快。 Vo ME 自举结果: tr缩短,VOH可达到VDD。

Vi

2. 寄生电容与自举率 VDD 由于寄生电容CO的存在: VGL CO = VGSL CB VGL = VGSL + Vo

COMS反相器原理

Y

VDD

B

图3-5-14 带缓冲级的与非门

A

上述电路虽然简单;但存在一些严重缺点: 1 输出电阻受输入端状态的影响; 2 当输入端数目增多时;输出低电平也随着相应提高;使低电平噪声容限降低

3 5 CMOS电路

3 5 1 CMOS反相器工作原理

3 5 2 CMOS反相器的主要特性

3 5 3 CMOS传输门

3 5 4 CMOS逻辑门电路

3 5 5 CMOS电路的锁定效应及 正确使用方法

图351 CMOS反相器

D

G

S

S

G

D

vO

VDD

TL

T0

vI

3 5 1 CMOS反相器工作原理

CMOS反相器由一个P沟道增强型MOS管和一个N沟道增强型MOS管串联组成 通常P沟道管作为负载管;N沟道管作为输入管

第一种形式: 在反相器基础上增加一对P沟道T'P和N沟道T'N MOS管 当控制端为1时;T'P和T'N同时截止;输出呈高阻态;当控制端为0时;T'P和T'N同时导通;反相器正常工作 该电路为低电平有效的三态输出门

EN

图3516 三态输出CMOS门结构之二

A

Y

VDD

≥1

TN

TP

A

Y

&

TN

当输入vI为高电平时;负载管截止;输入管导通;负载电流IOL灌入输入管;如图356 所示 灌入的电流就是N沟道管的iDS;输出特性曲线如图357 所示 输出电阻的大小与vGSNvI有关;vI越大;输出电阻越小;反相器带负载能力越强

CMOS反相器

B

18

N阱形成的主要步骤是:

1、外延层;2、原氧化生长;3、第一层掩膜(N阱注 入);4、N阱注入(高能);5、退火,如下图。外延层 与衬底有完全相同的晶格结构,只是纯度更高晶格缺陷更 少。氧化层的主要 作用是:1、保护表面的外延层免受沾 污;2、阻止在注入过程中对硅片过度损伤;3、作为氧化 屏蔽层,有助于控制注入过程中杂质的注入深度。光刻胶 图形覆盖了硅片上的特定区域,将起保护起来免于离子注 入。离子注入机离化杂质原子,使其加速获得高能,选出 最恰当的元素注入,并聚焦离子成为极窄的一束,最后扫 描使硅片不受光刻胶保护的区域得到均匀掺杂。杂质离子 穿透硅的晶格结构,对其共价原子结构造成损伤,这种损 伤在以后的扩散以及退火步骤中得到修复。

源/漏(S/D)注入工艺

为了完成倒掺杂技术,用中等剂量的掺杂稍稍超过LDD的结

深,但是比最初的双阱掺杂的结深浅,上一步形成的侧墙阻止

了注入杂质侵入狭窄的沟道。N+S/D注入的主要步骤是:1、第

七层掩膜(N+S/D注入);2、 N+S/D注入(中等能量)P+S/D

注入的步骤:1、第八层( P+S/D 注入);2、 P+S/D(中等能

B

SUM

≥1

COUT

B

13

---用RTL描述的一位半加器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY HADDER IS

PORT (A,B:IN STD_LOGIC;

SO,CO:OUT STD_LOGIC);

END ENTITY HADDER;

ARCHITECTURE FH1 OF HADDER IS

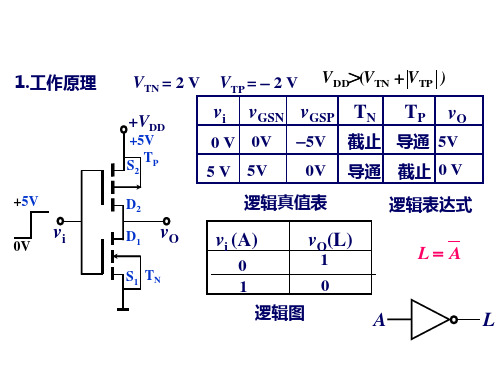

02-9.1 CMOS反相器电路及其特性-课件

图1 CMOS反相器

(a)结构示意图(b)电路图

]

,[)(DD SS I P th GS V V V V ∈+

当V I =V IL =0时

当V I =V IH =V DD 时

⎪⎩⎪⎨⎧<=>=N

th GS GS GS P th GS DD GS V v v V V v )(21)(10)(为负且⎪⎩⎪⎨⎧>=<=N

th GS DD GS P

th GS GS V V v V v )(2)(10输出V=V OH ≈V DD

输出V=V OL ≈0

Vo

静态功耗低

噪声容限高

工作速度快

在CMOS 反相器中,无论电路处于何种状态,T N 、T P 中总有一管截止,所以其静态功耗极低,有微功耗电路之称。

CMOS 反相器的阈值电压U TH =V DD /2,即两管状态在v I =V DD /2处转换,因此其噪声容限接近50%。

CMOS 反相器工作时总有一管导通,且导通电阻较小,为低阻回路,所以带容性负载时,充放电速度很快,CMOS 反相器的t pd ≈10ns 。

CMOS反相器的概述

+5V

0V vi

VTN = 2 V VTP = 2 V VDD>(VTN VTP )

+VDD

+5V

S2 TP

vi vGSN vGSP TN TP vO

0 V 0V 5V 截止 导通 5V 5 V 5V 0V 导通 截止 0 V

D2

D1 vO

S1 TN

逻辑真值表

逻辑表达式

vi (A)

0 1

TN1

TN2

10

导通 截止 截止 导通 0

11

导通 截止 导通 截止 0

N输入的或非门的电路的结构? 输入端增加有什么问题?

ห้องสมุดไป่ตู้

或非门

A

B

L A B

例:分析CMOS电路,说明其逻辑功能。

A B

=A⊙B

L AB X AB A B

A B A B

AB

异或门电路

2. 电压传输特性和电流传输特性

电压传输特性 vO f ( vI ) 电流传输特性iD f (vI )

3. 输入逻辑电平和输出逻辑电平

VOUT /V

5

输入低 电平

输入高电 平

0

VILmax VIHmin 5 VIN

/V

(Transfer c无ha定ra义cteristic )

输入低电平的上限值 VIL(max)

vO(L)

1 0

逻辑图

A

L A

L

CMOS反相器的重要特点:

第一,vI是高电平还是低电平 ,TN和TP中总是一个导通而 另一个截止。CMOS反相器的静态功耗几乎为零。

第二,MOS管导通电阻低,截止电阻高。使充、放电时间 常数小,开关速度更快,具有更强的带负载能力。

cmos反相器工作原理

cmos反相器工作原理

CMOS反相器是一种基于混合型CMOS技术开发的一种电路,它由一个

主要的反相器和周围电路组成。

它的工作原理是:输入端口输入电压必须

处于某一范围之内,它的输出端口电压高于输入端口的电压值,即输出一

个反向电压值,这就是CMOS反相器的作用原理。

CMOS反相器通常由几个主要的组件组成,这些组件包括p-型晶体管、n-型晶体管和金属氧化物半导体(MOSFET)。

反相器的输入端口会接受一

种电压值,这是输入电压,而晶体管和MOSFET会根据输入电压值来响应,一些形成周围电路的组件会根据所输入的电压来决定电流,最后将得到一

个反向的输出电压。

CMOS反相器的优点在于它的低功耗使得它可以用在节能类的电路中,并且它的体积小,结构简单以及可靠性高。

而且它输出电压的高低可以调节,因此它可以提高电路的灵活性和可靠性,也可以提高电路的稳定性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

详细讲解cmos反相器的原理及特点

CMOS(cornplementary MOS)由成对的互补p沟道与n沟道MOSFET所组成.CMoS逻辑成为目前集成电路设计最常用技术的缘由,在于其有低功率损耗以及较佳的噪声抑止才干.事实上,由于低功率损耗的需求,目前仅有CMOS技术被运用于ULSI 的制造.

CMOS反相器

如图6. 28所示,CMOS反相器为CMOS逻辑电路的基本单元.在CMOS反相器中,p 与n沟道晶体管的栅极衔接在一同,并作为此反相器的输入端,而此二晶体管的漏极也连接在一同,并作为反相器的输出端.n沟道MOSFET的源极与衬底接点均接地,而p沟道MOSFET的源极与衬底则衔接至电源供应端(VDD),需留意的是p沟道与n沟道MOSFET 均为增强型晶体管,当输入电压为低电压时(即vin=O,VGsn=o|VTp|(VGSp与VTp 为负值),所以p沟道MOSFET.为导通态,

因此,输出端经过p沟道MOSFET充电至VDD,当输入电压逐渐升高,使栅极电压等于VDD时,由于VGSn=VDD>VTn,所以n沟道MOSFET将被导通,而由于|VGSp |≈O

欲更深化天文解CMOS反相器的工作,可先画出晶体管的输出特性,如图6.29所示,其中显现Ip以及In为输出电压(V out)函数.Ip为p沟道MOSFET由源极(衔接至VDD)流向漏极(输出端)的电流;In为n沟道MOSFET由漏极(输出端)流向源极(衔接至接地端)

的电流.需留意的是在固定V out下,增加输入电压(vin)将会增加In而减少Ip,但是在稳态时,In应与Ip相同,关于给定一个Vin可由In(Vin)与Ip(Vin)的截距,计算出相对应的V out如图6. 29所示.如图6.30所示的Vin-V out曲线称为CMOS反相器的传输曲线.

CMOS反相器的一个重要的特性是,当输出处于逻辑稳态(即V out=或VDD)时,仅有一个晶体管导通,因此由电源供应处流到地端的电流非常小,且相当于器件关闭时的漏电流.事实上,只需在两个器件暂时导通时的极短暂态时间内才会有大电流流过,因此与。