verilog_HDL交通灯控制电路

verilogHDL交通灯设计说课材料

复位 六十进制计数交通灯设计第一模块 分频模块把 50MHz 分成 1Hzmodule divider (clk_50MHz, clk_1Hz);input clk_50MHz;output clk_1Hz;reg clk_1Hz;reg [30:0] count;parameter N = 50000000;always @ ( posedge clk_50MHz) beginif ( count == N/2-1 )begin clk_1Hz <= clk_1Hz + 1'b1;end elsecount <= 0;endendmodulecount <= count + 1'b1;第二模块 60 进制计数器程序:module counter60 ( clkin, reset, countnum);input clkin, reset; //reset output [5:0]countnum;reg [5:0] countnum;always @ ( posedge clkin )beginif ( !reset ) countnum <= 0;elsebeginif ( countnum == 59 ) //countnum <= 0;elsecountnum <= countnum + 1;endend endmodule第三模块控制器程序:module control ( elk, countin, start_sn, start_ew, redn, reds, rede, redw, greenn, gree ns, gree ne, gree nw);in put elk;in put [5:0] cou ntin; 〃60 进制计数器output start_sn, start_ew; //控制东西、南北方向倒计时控制开关output redn, reds, rede, redw; // 东西南北红灯开关output greenn, greens, greene, greenw; // 东西南北绿灯开关reg start_s n, start_ew;reg redn, reds, rede, redw;reg gree nn, gree ns, gree ne, gree nw;always @ ( posedge elk )beginif ( coun ti n == 0)beginstart_s n <= 1;start_ew <= 0;endelse if ( countin >= 1 && countin <= 24 )beginstart_s n <= 0;start_ew <= 0;gree nn <= 0;gree ns <= 0;gree ne <= 1;gree nw <= 1;redn <= 1;reds <= 1;rede <= 0;redw <= 0; endelse if ( countin > 24 && countin < 30 )beginstart_sn <= 0;start_ew <= 0;greenn <= 0;greens <= 0;greene <= 0;green w <= 0;redn <= 1;reds <= 1;rede <= 1;redw <= 1; end else if ( countin == 30 )begin start_sn <= 0; start_ew <= 1;endelse if ( countin > 30 && countin <= 59) beginstart_sn <= 0;start_ew <= 0;greenn <= 1;greens <= 1;greene <= 0;green w <= 0;redn <= 0;reds <= 0;rede <= 1;redw <= 1;end endendmoduleIA 英K 編|*.|-*耳斟 alhO CKB.llb 口 u <■] -M “ tl ■- JJ -4] Rrmu|14-faU.04*1PWT■i ris -THfel匸■鼻• * • xa “k . ■ W«* <■ D 咖,- Mirk* II 。

FPGA 交通灯控制器实验

交通灯控制器一、实验目的熟练掌握EDA软件quartus 2的应用环境,加强利用verilog语言解决生活中实际问题的能力。

二、实验原理和内容利用软件quartus 2进行编写程序实现十字路口交通灯控制器,达到A方向和B方向红、黄、绿三盏灯按合理的顺序亮或灭,并能将灯亮的时间用倒计时的形式显示在数码管上,最后通过软件自带的工具将交通灯控制器的门级电路和RTL级电路自动生成。

三、实验步骤1:首先分析交通灯的原理,整理出所需要的模块,设定每个灯的亮灯时间。

2:运行quartus 2软件、新建工程,然后新建verilog HDL文件,利用verilog语言编写程序实现A和B方向的红黄绿三盏灯合理的交替亮灭,通过对应数码管显示亮灯倒计时。

3:编译程序,若有错误根据错误提示对程序进行修改,直到编译通过,然后设置LED 灯和数码管的引脚,以达到控制A和B那盏灯亮和与之相对应的数码管做倒计时,倒计时结束,亮灯状态转换的效果。

4:将程序烧入FPGA开发板,观察开发板上的LED和数码管显示状况,看是否达到实验目的,若达到则记录实验结果并整理,反之继续修改,直到达到预期效果为止。

5:关闭电源,拆除实验器材。

四、实验数据A方向红灯40s,黄灯10s,绿灯30sB方向红灯40s,黄灯10s,绿灯30s五、实验代码module traffic(clk,en,seg,dig,lampa,lampb);input clk;//时钟信号,50Mhzinput en;// 使能信号,当为高电平时控制器工作,当为低电平时,进行初始化设置。

output[7:0] dig;//数码管位选output[7:0] seg;//数码管段选output[2:0] lampa;//A方向灯亮的情况output[2:0] lampb;//B方向灯亮的情况reg clk_out1;reg clk_out2;reg[15:0] count1;reg[31:0] count2;reg[1:0] a;reg[2:0] lampa;reg[2:0] lampb;reg[3:0] disp_dat;reg[7:0] dig;reg[7:0] seg;reg[7:0] ared,ayellow,agreen,bred,byellow,bgreen;reg[7:0] numa,numb;reg tempa,tempb;reg[1:0] counta, countb;always @(posedge clk)begincount1<=count1+1;if(count1==16'd25000)beginclk_out1<=~clk_out1;count1<=0;endendalways @(posedge clk)begincount2<=count2+1;if(count2==32'd2*******)beginclk_out2<=~clk_out2;count2<=0;endendalways @(en) //给各种灯亮的时间预置数,注意此处为十六进制的数beginif (!en)beginared <= 8'h40;ayellow <= 8'h10;agreen <= 8'h30;bred <=8'h40;byellow <= 8'h10;bgreen <= 8'h30;endendalways @(posedge clk_out2) //控制A方向的四种灯的亮灭及亮的时间beginif(en)beginif(!tempa)begintempa <= 1;case(counta)2'd0:begin numa <= ared; lampa <= 3'b011; counta <= 2'd1;end2'd1:begin numa <= agreen; lampa <= 3'b110; counta <= 2'd2;end2'd2:begin numa <= ayellow; lampa <= 3'b101; counta <= 2'd0;endendcaseendelsebeginif(numa[3:0]==0)beginnuma[3:0] <= 4'd9;numa[7:4] <= numa[7:4]-1;endelse numa[3:0] <= numa[3:0]-1;if (numa == 8'd2)tempa <= 0;endendelsebeginlampa <= 3'b000;counta <= 0; tempa <= 0;endendalways @(posedge clk_out2) //控制B方向的四种灯的亮灭及亮的时间beginif(en)beginif(!tempb)begintempb <= 1;case(countb)2'd0:begin numb <= bgreen; lampb <= 3'b110; countb <= 2'd1;end2'd1:begin numb <= byellow; lampb <= 3'b101; countb <= 2'd2;end2'd2:begin numb <= bred; lampb <= 3'b011; countb <= 2'd0;endendcaseendelsebeginif(numb[3:0]==0)beginnumb[3:0] <= 4'd9;numb[7:4] <= numb[7:4]-1;endelse numb[3:0] <= numb[3:0]-1;if (numb == 8'd2)tempb <= 0;endendelsebeginlampb <= 3'b000;countb <= 0; tempb <= 0;endendalways @(posedge clk_out1)begina<=a+1;endalways @(posedge clk_out1)begincase(a) //数码管显示什么样的数2'd0:disp_dat = numa[3:0];2'd1:disp_dat = numa[7:4];2'd2:disp_dat = numb[3:0];2'd3:disp_dat = numb[7:4];endcasecase(a) //数码管位选2'd0:dig = 8'b10111111;2'd1:dig = 8'b01111111;2'd2:dig = 8'b11111110;2'd3:dig = 8'b11111101;endcaseendalways @(disp_dat)begincase(disp_dat) //数码管译码4'h0:seg = 8'hc0; //显示04'h1:seg = 8'hf9; //显示14'h2:seg = 8'ha4; //显示24'h3:seg = 8'hb0; //显示34'h4:seg = 8'h99; //显示44'h5:seg = 8'h92; //显示54'h6:seg = 8'h82; //显示64'h7:seg = 8'hf8; //显示74'h8:seg = 8'h80; //显示84'h9:seg = 8'h90;endcaseendendmodule交通灯RTL电路交通灯门级网表实际效果。

Verilog HDL交通灯设计源程序

module aa(clk,rst,LAMPA,ledcom,data_out);output[7:0]LAMPA,ledcom,data_out;input clk,rst;reg[7:0]numa,ledcom;reg tempa,i;reg[3:0]data_in;reg[3:0]counta;reg[7:0]ared,ayellow,agreen;reg[7:0]LAMPA,data_out;reg[24:0]c,k,c1;reg clk1s;reg clk_100;reg[19:0]cnt2;always@(posedge clk)beginif(c==12500000)beginc<=0;clk1s=~clk1s;endelsec<=c+1;endalways@(posedge clk)begincnt2<=cnt2+1;if(cnt2==100000)beginclk_100=~clk_100;cnt2<=0;endendalways@(posedge clk1s or negedge rst)//该模块控制东西方向的三种灯if(!rst)LAMPA<=8'b00001001;elsebeginayellow<=8'b00000110;agreen<=8'b00000111;if(!tempa)begintempa<=1;if(counta==0)beginnuma<=agreen;LAMPA<=8'b00100001;//南北方向通绿灯亮东西方向红灯亮counta<=counta+1;endif(counta==1)beginnuma<=ayellow;LAMPA<=8'b00010001;//南北方向黄灯亮东西方向红灯亮counta<=counta+1;endif(counta==2)beginnuma<=ayellow;LAMPA<=8'b00000001;//南北方向黄灯灭东西方向红灯亮counta<=counta+1;endif(counta==3)beginnuma<=ayellow;LAMPA<=8'b00010001;//南北方向黄灯亮东西方向红灯亮counta<=counta+1;endif(counta==4)beginnuma<=agreen;LAMPA<=8'b00001100;//南北方向红灯亮东西方向绿灯亮counta<=counta+1;endif(counta==5)beginnuma<=ayellow;LAMPA<=8'b00001010;//南北方向红灯亮东西方向黄灯亮counta<=counta+1;endif(counta==6)beginnuma<=ayellow;LAMPA<=8'b00001000;//南北方向红灯亮东西方向黄灯灭counta<=counta+1;endif(counta==7)beginnuma<=ayellow;LAMPA<=8'b00001010;//南北方向红灯亮东西方向黄灯亮counta<=0;endendelsebegin//倒计时模块if(numa)beginif(numa==0)begintempa<=0;endelsebeginif(numa[7:4]==4'b0000)beginnuma[3:0]<=4'b1111;numa[7:4]<=numa[7:4]-4'b0001;endelsenuma[3:0]<=numa[3:0]-4'b0001;endendendend//////////////////////////////////////////////////////////////////////always@(posedge clk_100or negedge rst)if(!rst)begini<=0;ledcom<=8'b11111100;data_out<=8'b11000000;endelsebeginledcom<=~(1<<i);if(i==0)begindata_in<=numa[7:4];i<=i+1'b1;endelseif(i==1)begindata_in<=numa[3:0];i<=1'b0;endcase(data_in)4'b0000:data_out<=8'b11000000;//04'b0001:data_out<=8'b11111001;//14'b0010:data_out<=8'b10100100;//24'b0011:data_out<=8'b10110000;//34'b0100:data_out<=8'b10011001;//44'b0101:data_out<=8'b10010010;//54'b0110:data_out<=8'b10000011;//64'b0111:data_out<=8'b11111000;//74'b1000:data_out<=8'b10000000;//84'b1001:data_out<=8'b10011000;//9//4'b1111:data_out<=8'b10111111;default:data_out<=8'b11000000;endcaseendendmodule。

verilog课程设计-交通灯

课程论文论文题目基于DE2的交通灯设计完成时间课程名称 Verilog语言设计任课老师专业年级1.交通信号控制器设计要求与思路1.1设计背景FPGA是一种用户根据各自需要而自行构造逻辑功能的数字集成电路,其种类很多,内部结构也不同,但共同的特点是体积小、使用方便。

本文介绍了用VerilogHDL语言设计交通灯控制器的方法,并在QuartusII系统对FPGA芯片进行编译下载,由于生成的是集成化的数字电路,没有传统设计中的接线问题,所以故障率低、可靠性高,而且体积非常小。

本文通过EDA设计,利用VerilogHDL语言模拟仿真交通灯控制电路。

1.2设计要求根据交通灯控制器要实现的功能,考虑用两个并行执行的always语句来分别控制A方向和B方向的3盏灯。

这两个always语句使用同一个时钟信号,以进行同步,也就是说,两个进程的敏感信号是同一个。

每个always语句控制一个方向的3种灯按如下顺序点亮,并往复循环:绿灯----黄灯----红灯,每种灯亮的时间采用一个减法计数器进行计数,计数器用同步预置数法设计,这样只需改变预置数据,就能改变计数器的模,因此每个方向只要一个计数器进行预置数就可以。

为便于显示灯亮的时间,计数器的输出均采用BCD码,显示由4个数码管来完成,A方向和B方向各用两个数码管。

设定A方向红灯、黄灯、绿灯亮的时间分别为:35s、5s、35s,B方向的红灯、黄灯、绿灯亮的时间分别为:35s、5s、35s。

假如要改变这些时间,只需要改变计数器的预置数即可。

1.3设计思路两个方向各种灯亮的时间能够进行设置和修改,此外,假设B方向是主干道,车流量大,因此B方向通行的时间应该比A方向长。

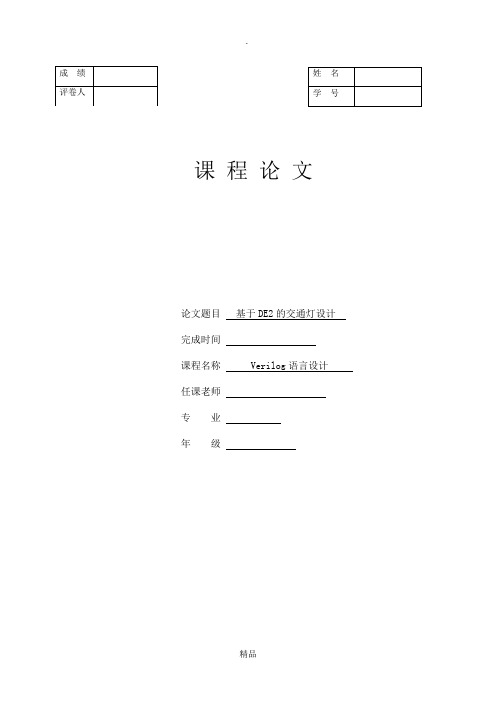

交通灯控制器的状态转换表见下表。

表中,1表示灯亮,0表示灯不亮。

A方向和B方向的红黄绿分别用R1、Y1、G1、R2、Y2、G2来表示。

交通灯控制器状态转换表从状态表中可以看出,每个方向3盏灯依次按如下顺序点亮,并不断循环:绿灯----黄灯----红灯,并且每个方向红灯亮的时间应该与另一个方向绿灯、黄灯亮的时间相等。

基于VerilogHDL的交通灯控制器设计

目录第一章设计原理 (1)1.1设计要求 (1)1.2设计思路和原理 (1)1.3实现方法 (1)第二章Verilog 程序设计 (2)2.1整体设计 (2)2.2 具体设计 (3)第三章仿真 (7)3.1 波形仿真 (7)第四章设计总结 (9)4.1 总结 (9)4.2参考资料 (9)程序清单 (10)交通灯控制器设计第一章 设计原理1.1设计要求设计一个交通控制器,用LED 显示灯表示交通状态,并以7段数码显示器显示当前状态剩余秒数 主干道绿灯亮时,支干道红灯亮;反之亦然,二者交替允许通行,主干道每次放行35s ,支干道每次放行25s 。

每次由绿灯变为红灯的过程中,亮光的黄灯作为过渡,黄灯的时间为5s 。

能进行特殊状态显示,特殊状态时东西、南北路口均显示红灯状态。

用LED 灯显示倒计时,并且能实现总体清零功能,计数器由初始状态开始计数,对应状态的显示灯亮。

1.2设计思路和原理本次设计是针对十字路口,进行南北和东西直行情况下交通灯控制。

设定东西方向为主干道方向,根据交通灯的亮的规则,在初始状态下四个方向的都为红灯亮启,进入正常工作状态后,当主干道上绿灯亮时,支干道上红灯亮,持续35S 后,主干道和支干道上的黄灯都亮启,持续5S 后,主干道上红灯亮启,支干道上绿灯亮启持续25S ,之后主干道和支干道上的黄灯都亮启5s ,一个循环完成。

循环往复的直行这个过程。

其过程如下图所示:0s30s25s主干道方向支干道方向图1.交通灯点亮时间控制说明1.3实现方法本次采用文本编辑法,即利用Verilog 语言描述交通控制器,通过状态机计数法,实现设计所要求的交通灯控制及时间显示。

设计中用两组红黄绿LED 模拟两个方向上的交通灯,用4个7段数码管分别显示两个方向上的交通灯剩余时间,控制时钟由试验箱上频率信号提供。

第二章 Verilog 程序设计2.1整体设计根据上章设计原理,交通灯控制的关键是各个状态之间的转换和进行适当的时间延时,根据状态机的设计规范,本次设计了三个状态之间的循环转化,其真值表及状态转化图如下所示:状状状状状状状状状状状状00状状10状状11状状01状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状001100010010001010100010图2.交通灯控制状态转化说明:该状态图为交通灯在正常情况下的状态转化图,进入控制后,状态00时主干道绿灯及支干道红灯亮起,进入状态01后两路黄灯亮起,状态11时主干道红灯及支干道绿灯亮起。

基于Verilog HDL的交通灯控制器

交通灯控制器专业:电子信息科学与技术_班级:学号:学生姓名:指导教师:*** _摘要交通灯是城市交通监管系统的重要组成部分,对于保证机动车辆的安全运行,维持城市道路的顺畅起到了重要作用。

目前很多城市交叉路口的交通灯实行的是定时控制,灯亮的时间是预先设定好的,在时间和空间方面的应变性能较差,一定程度上造成了交通资源的浪费,加重了道路交通压力。

本文在EDA技术的基础上,利用FPGA的相关知识设计了交通灯控制系统,可以根据实际情况对灯亮时间进行自由调整,通过数码管显示等待时间,点阵显示运行状态,蜂鸣器提示紧急状况,很好地维护了道路的交通规则。

整个设计系统通过Quartus Ⅱ软件中的Verilog HDL语言进行代码编写,并下载到FPGA器件中进行硬件调试,验证了设计的交通信号灯控制电路完全可以实现预定的功能,具有一定的实用性。

关键字:交通灯、定时控制、FPGA、Verilog HDL一、设计原理根据交通灯循环顺序表可以得到如表1的循环状态表,遇到紧急状况的时候,这时候有东西通行、南北通行和全部禁行三种情况,紧急状态结束后条件满足的情况下状态依次往后跳转。

表1 交通灯循环状态表1. 方案比较方案一:直接用GPIO口驱动双色点阵;方案二:用两块3-8译码器控制双色点阵,一个控制红色,另一个控制绿色;方案三:用一块4-16选择器控制双色点阵;通过比较方案一需要24个GPIO,方案二需要14个GPIO口,而方案三只需要12个GPIO 口,考虑到IO口的数量限制和资源的优化,故选择方案三,硬件部分还包括Led灯和蜂鸣器,用洞洞板搭建好了硬件电路。

2.系统框架图1 状态机状态转换图随着现代生活节奏的加快,人们出门便更多地选择自家的交通工具,这无疑加大了交通流量,如何控制十字路口的红绿灯,便显得相当的重要。

简单的,有效地控制红绿灯,是减小客流量,甚至减少交通事故的重要保障。

而此次课题,我选择了交通灯控制电路,能熟悉Verilog HDL 硬件描述语言在现实生活中的重要意义,为以后的学习和工作打好基础。

交通信号灯控制器的verilog实现

H a r b i n I n s t i t u t e o f T e c h n o l o g yV e r i l o g实验报告(2)实验内容:交通信号灯控制器班级:姓名:学号:哈尔滨工业大学2015年6月一、功能描述本设计利用Verilog HDL 语言,对一个十字路口的交通信号灯进行控制,可控制4个路口的红、黄、绿、左转四盏信号灯,让其按特定的规律进行变化。

并通过ModelSim软件对系统进行了仿真。

仿真结果表明系统可自动实现十字路口红绿灯及左转弯信号灯的控制。

实现设计目标如下:(1)设计一个十字路口的交通灯控制电路,每条路配有红、黄、绿、左转四盏交通信号灯。

通过控制器对四个路口的四组交通灯的状态实现自动循环控制;(2)实现两主干道车辆交替运行,每次通行直行时间为30 秒;左转时间为10秒,右转不受信号灯控制。

(3)黄灯作为绿灯转为左转灯,左转灯转为红灯的过渡信号灯,过渡时间为5s。

(4)系统设有总复位开关,可在任意时间对系统进行复位。

二、设计方案1.设计思路我们对图1所示的十字路口进行设计,路口A和路口C的车辆同时行驶,路口B和路口D的车辆同时行驶,所以虽然要控制4组信号灯,但其实它们可以俩俩合并,这样大大简化了设计。

由于我们采用自动控制方式,两个方向的灯按照顺序依次交替循环显示,每种灯亮的时间结合实际生活合理设定。

系统设有复位开关,可在任意时间内对系统进行复位。

图1 十字路口示意图由以上分析可知,该系统可视为一个状态机,而且共有8种状态,如表1所示。

表1 交通灯状态示意表由上表我们还可以得到状态转换图,如图2所示:图2 状态转移示意图该状态机共有两个输入信号rstn和clk,rstn为复位信号,当该信号为低电平时,状态机处于S0,且状态不发生改变。

当rstn为高电平时,这8个状态依次按时间顺序发生变化,每个状态保持多长时间由clk信号控制。

三、关键代码1.我们通过宏定义来设置每个状态保持的时间,这样既增强了代码的可读性,又方便以后的更改。

基于Verilog HDL语言的带左转复杂交通灯设计

基于Verilog HDL语言的带左转复杂交通灯设计1 引言EDA技术是依靠功能强大的电子计算机,在EDA工具软件平台上,对以硬件描述语言HDL(Hardware Description Language)为系统逻辑描述手段完成的设计文件,自动地完成逻辑编辑、化简、分割、综合、优化和仿真,直至下载到可编程逻辑器件CPLD/FPGA或专用集成电路ASIC(Application Specific Integrated Circuit)芯片中,实现既定的电子电路设计功能。

EDA技术使得电子电路设计者的工作仅限于利用硬件描述语言和EDA软件平台来完成对系统硬件功能的实现,极大地提高了设计效率,缩短了设计周期,节省了设计成本。

实现路口交通灯系统的控制方法很多,可以用标准逻辑器件,可编程控制器PLC,单片机等方案来实现。

但是这些控制方法的功能修改及调试都需要硬件电路的支持,在一定程度上增加了功能修改及系统调试的困难。

因此,在设计中采用EDA技术,应用目前广泛应用的Verilog HDL硬件电路描述语言,实现交通灯系统控制器的设计,利用MAX+PLUS 集成开发环境进行综合、仿真,并下载到CPLD可编程逻辑器件中,完成系统的控制作用。

2 Verilog HDL硬件描述语言的介绍Verilog HDL是目前应用最广泛的一种硬件描述语言。

Verilog HDL是在1983年由GDA(GateWay Design Automation)公司的Phil Moorby首创的。

1986年,他对Verilog HDL 的发展又作出了另一个巨大贡献:提出了用于快速门级仿真的XL算法。

Verilog-XL算法的成功,使Verilog HDL语言得到迅速发展。

基于Verilog HDL的优越性,IEEE于1995年制定了Verilog HDL 的IEEE标准,即Verilog HDL1364-1995。

Verilog HDL语言具有以下特点:基本逻辑门,例如and,or和nand等都内置在语言中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

青岛农业大学理学与信息科学学院电子设计自动化及专用集成电路课程设计报告设计题目__________ 用状态机设计交通灯控制器___________ 学生专业班级_____ 通信工程2008级1班 _______________ 学生姓名(学号)孙鹏飞(20082715)_____________ 扌旨导教师________________ 刘金梅_____________________ 完成时间2011-9-9 ________________________ 实习(设计)地点工程楼405 __________________2011年9月9日、课程设计目的和任务课程设计目的:本次课程设计是在学生学习完数字电路、模拟电路、电子设 计自动化的相关课程之后进行的。

通过对数字集成电路或模拟集成电路的模拟与 仿真等,熟练使用相关软件设计具有较强功能的电路, 提高实际动手,为将来设计大规模集成电路打下基础。

课程设计任务:设计一个交通控制器,用 LED 显示灯表示交通状态,并以 7 段数码显示器显示当前状态剩余秒数主干道绿灯亮时,支干道红灯亮;反之亦然,二者交替允许通行,主干道每次放行 35s ,支干道每次放行25s 。

每次由绿 灯变为红灯的过程中,亮光的黄灯作为过渡,黄灯的时间为 5s o 能进行特殊状 态显示,特殊状态时东西、南北路口均显示红灯状态。

用LED 灯显示倒计时,并且能实现总体清零功能,计数器由初始状态开始计数,对应状态的显示灯亮。

二、分析与设计1、设计任务分析本次设计是针对十字路口,进行南北和东西直行情况下交通灯控制。

设定东 西方向为主干道方向,根据交通灯的亮的规则,在初始状态下四个方向的都为红 灯亮启,进入正常工作状态后,当主干道上绿灯亮时,支干道上红灯亮,持续 35S 后,主干道和支干道上的黄灯都亮启,持续 5S 后,主干道上红灯亮启,支 干道上绿灯亮启持续25S ,之后主干道和支干道上的黄灯都亮启 5s ,一个循环完 成。

循环往复的直行这个过程。

其过程如下图所示:图1•交通灯点亮时间控制说明2、设计方案论证主干道方向支干道方向本次采用文本编辑法,即利用 Verilog HDL语言描述交通控制器,通过状态 机计数法,实现设计所要求的交通灯控制及时间显示。

设计中用两组红黄绿LED 模拟两个方向上的交通灯,用4个7段数码管分别显示两个方向上的交通灯剩余 时间,控制时钟由试验箱上频率信号提供。

根据上章设计原理,交通灯控制的关键是各个状态之间的转换和进行适当的 时间延时,根据状态机的设计规范,本次设计了三个状态之间的循环转化, 其真 值表及状态转化图如下所示:图2.交通灯控制状态转化说明:该状态图为交通灯在正常情况下的状态转化图, 进入控制后,状态00 时主干道绿灯及支干道红灯亮起, 进入状态01后两路黄灯亮起,状态11时主干道 红灯及支干道绿灯亮起。

进入10状态两路黄灯亮起。

结束一个循环,从00状态重 新开始循环。

为实现控制与显示的功能,需要设计交通灯点亮顺序控制程序,倒数计时程 序,七段数码管显示程序,数码管显示扫描程序,其系统结构图如下所示:图3•交通灯控制系统结构图其中resets 复位信号,elk 为时钟信号,hold 为特殊情况控制信号,输入hold 时两个 方向红灯无条件亮起。

3、详细设计根据整体设计要求,编写各个功能部分 Verilog HDL 程序,设置各输入输出 变量说明如下主干道方向 支干道方向 状态00 红、黄、绿 -001 状态01 红、黄、绿 -010状态11 红、黄、绿-100 状态10红、黄、绿 -010红、黄、绿 100 红、黄、绿 010 红、黄、绿 001 红、黄、绿 010状态00状态0110 状态11clk:为计数时钟;qclk :为扫描显示时钟;en:使能信号,为 1 的话,则控制器开始工作;reset: 复位信号,为 1 的话,控制及技术回到初始状态;hold :特殊情况控制信号,为1的话,则两个方向无条件显示为红灯;light1: 控制主干道方向四盏灯的亮灭;其中, light1[0]~light[2] ,分别控制主干道方向的绿灯、黄灯和红灯;light2: 控制支干道方向四盏灯的亮灭;其中, light2[0] ~ light2[2] ,分别控制支干道方向的绿灯、黄灯和红灯;num1: 用于主干道方向灯的时间显示, 8 位,可驱动两个数码管;num2: 用于支干道方向灯的时间显示, 8 位,可驱动两个数码管;counter:用于数码管的译码输出;stl, st2:数码管扫描信号。

输入输出及中间变量设置如下:moduletraffic(en,clk,qclk,reset,reset1,hold,num1,num2,light1,light2,counter,st1,st2);input en,clk,qclk,reset,hold,reset1;output st1,st2;output[7:0] num1,num2;output[6:0]counter;output[2:0] light1,light2;reg tim1,tim2,st1,st2;reg[1:0]state1,state2,ste;reg[2:0]light1,light2;reg[3:0]num;reg[6:0]counter;reg[7:0] num1,num2;reg[7:0] red1,red2,green1,green2,yellow1,yellow2;3.1二极管点亮控制该部分程序的作用是根据计数器的计数值控制发光二极管的亮、灭,以及输出倒计时数值给七段数码管的译码电路。

此外,当检测到特殊情况( hold= ‘)1'发生时,无条件点亮红灯的二极管,当检测到复位信号,两个方向计数与控制回复到00 状态。

因为主、支干道两个方向二极管点亮的顺序与延迟时间不同,顾编写两个独立的部分来控制,具体程序如下:1)主干道方向 always @(posedge clk ) beginif(reset) //复位与特殊情况控制begin light1<=3'b001; num1<=green1;endelse if(hold) begin light1<=3'b100; num1<=green1;endelse if(en)begin //使能有效开始控制计数if(!tim1) //begin //主干道交通灯点亮控制 tim1<=1;case(state1)2'b00:begin num1<=green1;light1<=3'b001;state1<=2'b01;end 2'b01:beginnum1<=yellow1;light1<=3'b010;state1<=2'b11;end 2'b11:beginnum1<=red1;light1<=3'b100;state1<=2'b10;end 2'b10:beginnum1<=yellow1;light1<=3'b010;state1<=2'b00;end default:light1<=3'b100;endcaseend2)支干道方向 always @(posedge clk ) begin if(reset) //复位与特殊情况控制 beginlight2<=3'b100;num2<=red2;end else if(hold) begin light2<=3'b100;num2<=red2;endelse if(en)beginif(!tim2)begintim2<=1;case(state1)2'b00:begin num2<=red2;light2<=3'b100;state2<=2'b01;end2'b01:begin num2<=yellow1;light2<=3'b010;state2<=2'b11;end2'b11:begin num2<=green2;light2<=3'b001;state2<=2'b10;end2'b10:begin num2<=yellow2;light2<=3'b010;state2<=2'b00;enddefault:light2<=3'b100;endcaseend3.2倒数计时该部分程序完成二极管发光时延的计数,并将计数结果送到数码管显示电路,每切换到一个状态,计数器的初值都被重置,以实现不同颜色二极管不同的时延要求。

本次设计直接用逻辑运算完成2 位十进制数的计数,未采用分位器的设计。

因为主、支干道上计数器的结构完全相同,顾只列出一路的程序,其具体程序如下所示:always @(posedge clk )beginelsebegin // 倒数计时if(num1>0)if(num1[3:0]==0)beginnum1[3:0]<=4'b1001;num1[7:4]<=num1[7:4]-1;endelse num1[3:0]<=num1[3:0]-1;if(num1==1) tim1<=0;endendelsebeginlight1<=3'b010;num1=2'b00;tim1<=0;endend3.3数码管的译码及扫描显示该段程序主要完成4 个7 段数码管的译码显示及扫描,使系统能正常显示主、支干道两个方向上的剩余时间。

译码的时钟频率要低,为Hz 级。

扫描的时钟频率要高,最低不得小于人眼分辨频率50Hz,具体程序如下所示:always @(posedge qclk)begin //数码管扫描if(reset1)beginst1=0;st2=0;endelsebegincase({st2,st1})2'b00:begin num<=num1[3:0];{st2,st1}<=2'b01; end2'b01:begin num<=num1[7:4];{st2,st1}<=2'b10; end2'b10:begin num<=num2[3:0];{st2,st1}<=2'b11; end2'b11:begin num<=num2[7:4];{st2,st1}<=2'b00; endendcaseendendalways @(posedge qclk)begin //数码管译码显示case(num)4'b0000: counter<=7'b0111111; //0 4'b0001: counter<=7'b0000110; //1 4'b0010: counter<=7'b1011011; //2 4'b0011: counter<=7'b1001111; //3 4'b0100: counter<=7'b1100110; //4 4'b0101: counter<=7'b1101101; //5 4'b0110: counter<=7'b1111101; //6 4'b0111: counter<=7'b0000111; //7 4'b1000: counter<=7'b1111111; //84'b1001: counter<=7'b1101111; 〃9 default: counter<=7'b0111111; 〃0 endcase end en dmodule4、源代码清单(按照设计的功能模块,提供适量主要代码并注释, 1页-1.5页)module traffic(e n,clk,qclk,reset,reset1,hold, nu m1, nu m2,light1,light2,co un ter,st1,st2);in put en, clk,qclk,reset,hold,reset1; output st1,st2;output[7:0] num1,num2; output[6:0]counter;output[2:0] light1,light2; reg tim1,tim2,st1,st2; reg[1:0]state1,state2,ste; reg[2:0]light1,light2; reg[3:0]num; reg[6:0]counter; reg[7:0] num1,num2;'TcTcQ Q QR1reg[7:0] red1,red2,green1,green2,yellow1,yellow2;always @(en )if(!en) begin //设置计数初值 green1<=8'b00110101;red1<=8'b00100101; yellow1<=8'b00000101; green2<=8'b00100101;red2<=8'b00110101; yellow2<=8'b00000101;endalways @(posedge clk )beginif(reset) //复位与特殊情况控制begin light1<=3'b001; num1<=green1;endelse if(hold)begin light1<=3'b100; num1<=green1;endelse if(en)begin //使能有效开始控制计数 if(!tim1) // 开始控制begin //主干道交通灯点亮控制 tim1<=1;case(state1)2'b00:begin num1<=green1;light1<=3'b001;state1<=2'b01;end2'b01:begin num1<=yellow1;light1<=3'b010;state1<=2'b11;end2'b11:begin num1<=red1;light1<=3'b100;state1<=2'b10;end2'b10:begin num1<=yellow1;light1<=3'b010;state1<=2'b00;enddefault:light1<=3'b100;endcaseendelsebegin //倒数计时if(num1>0)if(num1[3:0]==0) beginnum1[3:0]<=4'b1001; num1[7:4]<=num1[7:4]-1;endelse num1[3:0]<=num1[3:0]-1;if(num1==1) tim1<=0;endendelsebeginlight1<=3'b010;num1=2'b00;tim1<=0;endendalways @(posedge clk )beginif(reset) //复位与特殊情况控制beginlight2<=3'b100;num2<=red2;endelse if(hold)beginlight2<=3'b100;num2<=red2;endelse if(en)beginif(!tim2)begintim2<=1;case(state1)2'b00:begin num2<=red2;light2<=3'b100;state2<=2'b01;end2'b01:begin num2<=yellow1;light2<=3'b010;state2<=2'b11;end2'b11:begin num2<=green2;light2<=3'b001;state2<=2'b10;end 2'b10:begin num2<=yellow2;light2<=3'b010;state2<=2'b00;enddefault:light2<=3'b100;endcaseendelsebegin //倒数计时if(num2>0)if(num2[3:0]==0)beginnum2[3:0]<=4'b1001;num2[7:4]<=num2[7:4]-1;endelse num2[3:0]<=num2[3:0]-1;if(num2==1) tim2<=0;endendelsebegintim2<=0;state2<=2'b00;light2<=3'b010;endendalways @(posedge qclk)begin //数码管扫描if(reset1)beginst1=0;st2=0;endelsebegincase({st2,st1})2'b00:begin num<=num1[3:0];{st2,st1}<=2'b01; end2'b01:begin num<=num1[7:4];{st2,st1}<=2'b10; end2'b10:begin num<=num2[3:0];{st2,st1}<=2'b11; end2'b11:begin num<=num2[7:4];{st2,st1}<=2'b00; end endcase endendalways @(posedge qclk)begin //数码管译码显示case(num)4'b0000: counter<=7'b0111111; //04'b0001: counter<=7'b0000110; //14'b0010: counter<=7'b1011011; //24'b0011: counter<=7'b1001111; //34'b0100: counter<=7'b1100110; //4 4'b0101: counter<=7'b1101101; //5 4'b0110: counter<=7'b1111101; //6 4'b0111: counter<=7'b0000111; //7 4'b1000: counter<=7'b1111111; //8 4'b1001: counter<=7'b1101111; //9 default: counter<=7'b0111111; //0 endcaseendendmodule三、系统实施3.1波形仿真在Quarturs H软件下创建工程,新建编辑设计文件,将程序输入,整体编译后, 新建波形仿真文件。