EDA实验指导书全(Verilog版)

EDA verilog JK触发器实验

1. case 语句描述JK触发器(带有异步清0,异步置1功能) module jk_ff(clk,j,k,Q,rs,set); input clk,j,k,set,rs; output Q; reg Q; always@(posedge clk or negedge rs or negedge set) begin if(!rs) Q<=1'b0; else if(!set) Q<=1'b1; else case({j,k}) 2'b00:Q<=Q; 2'b01:Q<=1'b0; 2'b10:Q<=1'b1; 2'b11:Q<=~Q; default:Q<=1'bx; endcase end endmodule

4.1.3赋值语句

使用阻塞和非阻塞赋值应遵循的原则: (1)当用“always”块来描述组合逻辑时,既可以用阻塞赋值,也 可以用非阻塞赋值,建议尽量使用阻塞赋值。 (2)对时序逻辑描述和建模,使用非阻塞赋值方式。 (3)为锁存器建模,应尽量使用非阻塞赋值。 (4)若在同一个“always”过程块中既为组合逻辑建模,又为时序 逻辑建模,最好使用非阻塞赋值方式。 (5)在同一个“always”过程块中,最好不要混合使用阻塞赋值和 非阻塞赋值。虽然同时使用这两种赋值方式在综合时不一定出错, 但对同一个变量不能既进行阻塞赋值又进行非阻塞赋值,在综合 时会产生错误。 (6)不能在2个或2个以上的“always”过程块中对同一个变量赋值, 这样会引发冲突,综合时出错。

实验五 用VerilogHDL描述JK触发器

else if({j,k}==2'b01) Q<=0; else if({j,k}==2'b10) Q<=1; else Q<=~Q; end end endmodule

EDA实验指导书

EDA技术实验指导书陆利坤编北京印刷学院2004.5前言主要术语摘要:*EDA(电子设计自动化):Electronic Design Automation*PLD(可编程逻辑器件):Programmable Logical Device*CPLD(复杂可编程逻辑器件):Complex Programmable Logical Device*FPGA(现场可编程门阵列):Field Programmable Gates Array*ISP(在系统可编程): In System Programmble*ASIC(专用集成电路): Application Specific Integrated Circiuts*VHDL(硬件描述语言) : Very High Speed IC Hardware Description Language 20世纪末,电子技术发展迅速,在近代通讯控制、电子测量等众多领域,都广泛地应用电子电路技术。

电子设计自动化EDA技术的发展,要求广大专业人才能够较快的掌握该技术的应用。

为了帮助广大同学更好的学习应用EDA技术我们编写了本实验指导书。

本着快速掌握、即学即用和实用易学的目的,本书采用了理论从略、应用从详的原则,指导书的主要结构特点分为以下三个部分:1.模拟验证性实验。

以完成一个实际应用实例为例,引导同学完成并掌握整个设计过程。

2.基本训练性实验。

本着由简单到复杂、由单一到综合的目的,巩固和加强学生对基本理论的掌握,训练提高学生的基本设计能力。

3.增加设计性实验。

提出实验目的要求和实验内容及约束条件,设计方案、功能选择由学生自行拟定,以培养学生独立组织实验和创新设计的能力。

本指导书体系与内容由陆利坤老师编写,刘小清老师对实验体系与内容做了审阅,并提出了宝贵意见。

在此特对本实验改革付出辛勤劳动的各位老师和同学表示感谢。

限于笔者的水平和时间,有错之处请批评指正。

编者2004.5 于北京印刷学院目录实验一实验系统的构成,软件环境的操作(模拟验证实验)实验二 3/8译码器,BCD/七段显示译码器实验实验三触发器设计实验实验四按键去抖设计实验实验五计数器实验实验六分频器设计实验实验七状态机设计实验实验八数字钟设计实验实验九编码矩阵键盘接口设计实验实验十可设置数字钟设计实验实验十一可控制点阵LED显示器的设计实验实验十二设计性实验实验一实验系统的构成,软件环境的操作一.实验目的1.学习MAX+PLUSII 软件的基本操作;2.学习使用原理图、文本文件进行设计输入;3.初步掌握器件设计、编译、仿真和编程的过程;4.学习掌握教学实验板的使用方法;二.实验说明采用Verilog-HDL和原理图输入方式设计一个简单的三人表决器,并下载到PLD实验箱进行实际运行。

EDA实验指导书全

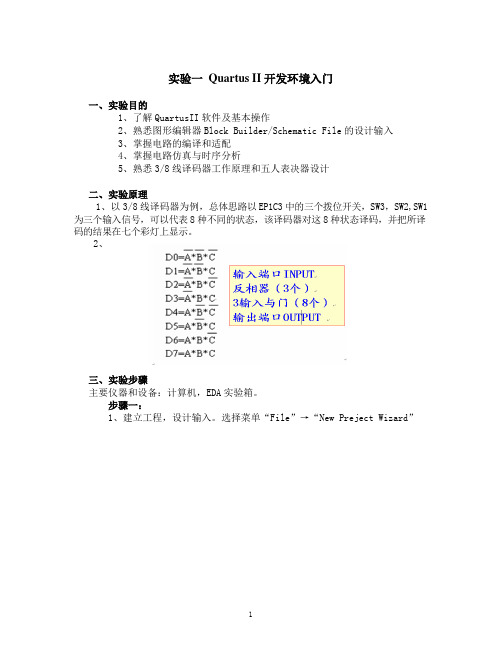

实验一Quartus II开发环境入门一、实验目的1、了解QuartusII软件及基本操作2、熟悉图形编辑器Block Builder/Schematic File的设计输入3、掌握电路的编译和适配4、掌握电路仿真与时序分析5、熟悉3/8线译码器工作原理和五人表决器设计二、实验原理1、以3/8线译码器为例,总体思路以EP1C3中的三个拨位开关,SW3,SW2,SW1为三个输入信号,可以代表8种不同的状态,该译码器对这8种状态译码,并把所译码的结果在七个彩灯上显示。

2、三、实验步骤主要仪器和设备:计算机,EDA实验箱。

步骤一:1、建立工程,设计输入。

选择菜单“File”→“New Preject Wizard”将设计文件加入工程中:点击下方的“Next” 按钮,在弹出的对话框中点击“File”栏的按钮,将此工程相关的所有VHDL文件加入进此工程(如果有的话)。

Cyclone系列的EP1C3T144C8按下“Next”后,出现仿真工具选择对话框。

不作任何选择。

4、完成设置点击“Next”后,完成工程的设定,点击“finish”。

步骤二:1、选择File/New或点击主菜单中的空白图标,进入新建程序文件状态,选择VHDL file 。

VHDL程序文件的扩展名是:* .vhd程序代码:-- A simple 3 to 8 decoderlibrary ieee;use ieee.std_logic_1164.all;entity decoder isport ( inp: in std_logic_vector(2 downto 0);outp: out std_logic_vector(7 downto 0)); end decoder;architecture behave of decoder isbeginoutp(0) <= '1' when inp = "000" else '0';outp(1) <= '1' when inp = "001" else '0';outp(2) <= '1' when inp = "010" else '0';outp(3) <= '1' when inp = "011" else '0';outp(4) <= '1' when inp = "100" else '0';outp(5) <= '1' when inp = "101" else '0';outp(6) <= '1' when inp = "110" else '0';outp(7) <= '1' when inp = "111" else '0';end behave;步骤三:1、选择菜单“File”→“New ” →“ Schematic File”,即弹出原理图编辑框。

EDA实验指导书

1.1

5

EDA 技术实验指导书

4. MAX+PlusII 的使用: 安装好后, 第一次运行 MAX+PlusII 时还需要多许多的工作才能保证软件的正常运行。 (1)在 MAX+PlusII 的软件目录下,双击 MAX+PlusII 10.2 BASELINE 的图标。第一 次运行时屏幕上会出现关于授权协议的提示窗口,如图 1.2 所示。 (2)阅读完授权协议信息以后,选择 Yes,出现防止复制的警告信息。选择 No,则 退出 MAX+PlusII。 (3)将你所申请的授权码文件 License.dat 文件拷贝到\ maxplus2 的文件夹下面。 (4)设置授权码的过程是:在 MAX+PlusII 界面中,选择菜单命令 Options/License Setup,出现 1.3 的所示的对话框,通过 Browse 按钮选择 License .dat 文件。 (5)是设置好授权文件后,选择 OK 按钮,就会回到 MAX+PlusII 管理器界面中进 行设计了。

1.2

1.3

6

EDA 技术实验指导书

MAX+PlusII 图形设计输入方法

1. 指定设计项目名称 MAX+PlusII 编译的工作对象是项目,所有在进行一个逻辑设计的时候,要指定设计的 项目名称,每个项目都应该建立一个单独的子目录 (只能是数字或者是英文字符不能是中 文),对于初学者而言,每个设计必须要有一个项目名,并且保证项目名和设计文件名一致。 2. 建立新文件 (1) 在 File 菜单中选择 New,如图 2.1 所示,将出现 New 的对话框,如图 2.2 所示

4

EDA 技术实验指导书

MAX+PlusII 的安装

EDA 实验指导书

EDA技术基础实验指导书海南大学信息学院编目录实验一MAX –plusII及开发系统使用 1 实验二高速四位乘法器设计7 实验三秒表的设计9 综合性设计性实验实验四序列检测器的设计12 实验五数字频率计的设计14 数字密码锁17 交通灯控制器182EDA实验指导书实验一MAX –plusII及开发系统使用一、实验目的1、熟悉利用MAX-plusⅡ的原理图输入方法设计简单的组合电路2、掌握层次化设计的方法3、熟悉DXT-BⅢ型EDA试验开发系统的使用二、主要实验设备PC 机一台(中档以上配置),DXT-B3 EDA实验系统一台。

三、实验原理数字系统设计系列实验是建立在数字电路基础上的一个更高层次的设计性实验。

它是借助可编程逻辑器件(PLD),采用在系统可编程技术(ISP),利用电子设计自动化软件(EDA),在计算机(PC)平台上进行的。

因为本实验是在计算机平台上进行,因此实验方式,实验手段和实验仪器与传统的实验有很大的区别,主要体现在以下几个方面:1、实验器材集中化,所有实验基本上在一套实验设备上进行。

传统的实验每作完一个实验,实验器材基本上都要变动(个别除外)。

而做本实验时,只要在计算机上把不同的程序输进去,其它步骤所有实验都一致;2、实验耗材极小(基本上没有耗材);3、在计算机上进行,自动化程度高,人机交互性好,修改、验证实验简单;4、下载后,实验结果清晰;5、实验仪器损耗少,维护简单;下面,我们就本套实验设备做一个简单的介绍。

3(一)Max+plusⅡ10.0的使用。

1、Max+PlusII软件的安装步骤:第一步:系统要求奔3CPU以上,128M内存以上,4G 以上硬盘,98 操作系统(98或Me操作系统才可以下载,其他操作系统下载必须安装驱动,否则只能仿真,如果大家只进行仿真的话,对系统没要求)第二步:安装点击安装可执行文件进行安装,安装完毕后会弹出一对话框,点击是或否都可以。

第三步:将安装文件夹中的License 文件夹打开,里面有一个License.bat 注册文件,将此文件复制到你的安装目录下(你的安装目录可放在任一个驱动器下,然后建立一个Max10的文件夹,将系统安装在此文件夹中,安装后此文件夹中会有三个文件夹)的任一个文件夹中,要清楚位置。

EDA实验指导(基于verilog)

图1-19管脚分配

在图1-19中以锁定端口A的管脚为例,其它端口的管脚锁定与其基本一致。选择端口A的对应Assignment Name待其变为蓝色,双击之,出现下拉菜单选取如图1-19所示的Location(Accepts wildcards/groups)选项。选择端口A的对应Value栏,待其变为蓝色,依照表1-2和表1-3所示的硬件与FPGA的管脚连接表(或附录),输入对应的管脚名AH12,按回车键,软件将自动将其改为PIN_AH12,同时蓝色选择条会自动跳转到Value栏的下一行,这表明软件已经将输入端口A分配到FPGA的AH12引脚上,如图1-20所示。

LED9display

LED[9]

Pin_F22

JP2_96

LED10display

LED[10]

Pin_E22

JP2_97

LED11display

LED[11]

Pin_F21

JP2_98

LED12display

表1-3 LED灯与FPGA管脚连接表

四、实验步骤

下面将通过这个实验,向读者介绍QUARTUSII的项目文件的生成、编译、管脚分配以及时序仿真等的操作过程。

图1-12设计文件的输入

图1-13保存设计文件对话框

3、对设计文件进行编译

QUARTUSII编译器窗口包含了对设计文件处理的全过程。在QUARTUSII软件中选择Processing>Compiler Tool菜单项,则出现QUARTUSII的编译器窗口,如图1-14所示,图中标明了全编译过程各个模块的功能。

在QUARTUSII图形编辑器窗口(图1-10)中,根据个人爱好,可以随时改变Block Editor的显示选项,如导向线和网格间距、橡皮筋功能、颜色以及基本单元和块的属性等。

EDA实验指导书V3.2

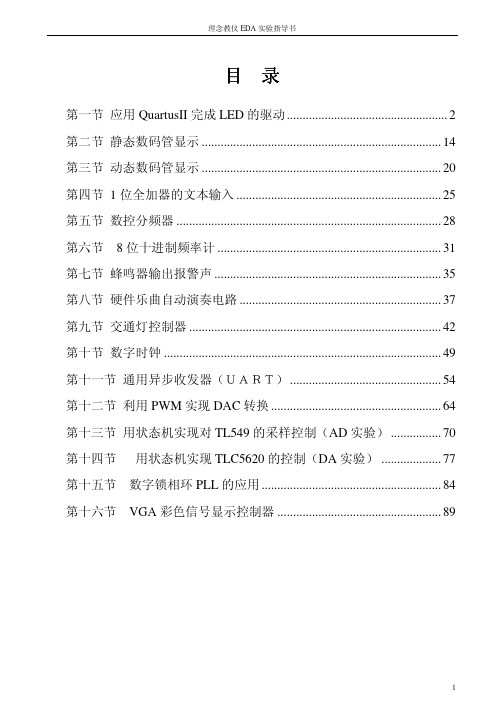

第一节 应用 QuartusII 完成 LED 的驱动

1、实验目的 通过此实验让学生逐步了解、 熟悉和掌握 FPGA 开发软件 QuartusII 的使用方法及 Verilog HDL 的编程 方法。 本实验力求以详细的步骤和讲解让学生一最快的方式了解 EDA 技术开发以及软件的使用,从而快速 入门并激起读者对 EDA 技术的兴趣。 2、实验内容 实验平台 (EP2C5 核心板) 上有 1 个发光二极管 H1, 其硬件原理图如图 1.1 所示。 H1 与 FPGA (EP2C5) 的 32 管脚相连。

4

理念教仪 EDA 实验指导书

图 1.5 新建工程添加文件对话框 由于是新建工程,暂无输入文件,所以直接单击 Next,进入图 1.6 所示的指定目标器件对话框。这 里我们选择的是 EP2C5-2C8 核心板上 CycloneII 系列 EP2C5Q208C8。

图 1.6 新建工程器件选择对话框 在图 1.6 右边的过滤器栏(Filters)中,设计者可以通过指定封装、引脚数以及器件速度等级来加快器 件查找的速度。 指定完器件后,单击 Next 进入图 1.7 所示的指定 EDA 工具对话框。

图 1.15 完整的顶层模块图 h) 选择 File>>Save 保存 BDF 文件。

(5)选择器件型号 每种型号的 FPGA 芯片的引脚可能都不相同, 因此在进行引脚分配之前都应选择相应目标 FPGA 芯片 型号。这一步其实在第 1)步中已经完成,这里只是让读者了解,在 Quartus II 工程创建好后仍然可以选择 并修改器件型号。 如图 1.16 所示,选择 Assignments>>Device 打开器件选择对话框如图 1.17 所示。在对话框中,指定所 需的目标器件型号,本实验为 EP2C5Q208C8。

EDA实验指导书Verilog版

实验一QUARTUS Ⅱ的设计流程[输入方式:文本输入、图形输入、波形输入等]一、实验目的:一、掌握QUARTUSⅡ安装进程;二、熟悉QUARTUSⅡ设计环境;3、掌握QUARTUSⅡ的设计进程。

二、实验内容:用文本输入法设计一个半加器。

三、实验步骤:一、安装QUARTUS II。

注:第一次安装QUARTUS要安装license。

二、QUARTUSⅡ设计开发步骤(一)、创建工作文件夹在windows中成立一个文件夹(又称工作库或WORK LIBRARY),用于保留设计工程项目的有关文件。

注:设计工程项目的有关文件不能保留在根目录下,必需保留在一个文件夹之下。

例如成立的文件夹:E:\HADD(二)、启动Quartus II点击QUARTUSⅡ图标打开QUARTUSⅡ设计窗口。

(三)、设计文件输入1、打开输入文件编辑器点击菜单File\new…新成立一个文本设计文件。

用文本输入法输入程序。

程序见附录。

2、保留文件,文件名名同实体名。

后缀.v(四)、全编译(逻辑综合)1、创建工程点击菜单File\New Project Wizard…….进行工程设置。

完成工作文件夹的选定、工程名、顶层设计文件名、编程器件的肯定等工程。

2、编译前的相关设置设置⑴选择PLD芯片:Assignmenmts\Settings\Device弹出的窗口当选择选择芯片。

⑵选择配置芯片的工作方式:Assignmenmts\Settings\Device\Device&Pin Options 弹出的窗口中首选General项,在Options栏当选择Auto-restart-configuration after error.⑶选择配置芯片和编程方式:Assignmenmts\Settings\Device\Device&Pin Options 弹出的窗口当选择Configuration栏,在窗口中设置配置方式,配置芯片和是不是生成紧缩的配置文件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA实验指导书熊利祥编武汉理工大学华夏学院2011年9月前言一、实验课目的EDA实验课是电子工程类专业教学中重要的实践环节,包括了ISE开发环境基本操作及Verilog语言、组合逻辑电路设计、流水灯设计、计数器设计、扫描显示电路的驱动、综合层次性实验——交通灯或数字秒表设计实验。

要求学生通过实验学会正确使用EDA技术,掌握FPGA器件的开发,熟练使用ISE开发环境,掌握Verilog 语言的编程,掌握数字电路和系统的设计。

通过实验,使学生加深对课堂专业教学内容的理解,培养学生理论联系实际的能力,实事求是,严谨的科学作风,使学生通过实验结果,利用所学的理论去分析研究EDA技术。

培养学生使用EDA实验设备的能力以及运用实验方法解决实际问题的能力。

二、实验要求:1.课前预习①认真阅读实验指导书,了解实验内容;②认真阅读有关实验的理论知识;③读懂程序代码。

2.实验过程①按时到达实验室;②认真听取老师对实验内容及实验要求的讲解;③认真进行实验的每一步,观察程序代码与仿真结果是否相符;④将实验过程中程序代码和仿真结果提交给老师审查;⑤做完实验后,整理实验设备,关闭实验开发板电源、电脑电源后方可离开。

3.实验报告①按要求认真填写实验报告书;②认真分析实验结果;③按时将实验报告交给老师批阅。

三、实验学生守则1.保持室内整洁,不准随地吐痰、不准乱丢杂物、不准大声喧哗、不准吸烟、不准吃东西;2.爱护公务,不得在实验桌及墙壁上书写刻画,不得擅自删除电脑里面的文件;3.安全用电,严禁触及任何带电体的裸露部分,严禁带电接线和拆线;4.任何规章或不按老师要求操作造成仪器设备损坏须论价赔偿。

目录实验一 ISE开发环境入门_五人表决器 (4)实验二加法器、乘法器、比较器的设计 (26)实验三流水灯 (28)实验四计数器 (30)实验五综合层次性实验——交通灯设计 (32)实验六综合层次性实验——数字秒表设计 (34)附录一 basys 2开发板资料 (36)实验一ISE开发环境入门一、实验目的1.了解ISE开发环境及基本操作。

2.熟悉设计方法和步骤。

3.掌握电路的综合和实现。

4.掌握电路仿真与时序分析。

5.熟悉3/8线译码器工作原理和五人表决器设计。

二、实验内容和基本原理1.以3/8线译码器为例,总体思路以Basys 2开发板中的三个拨位开关,SW2,SW1,SW0为三个输入信号,可以代表8种不同的状态,该译码器对这8种状态译码,并把所译码的结果在八个发光二级管(LD7~LD0)上显示。

2.输入与输出之间逻辑关系3.以Basys 2开发板中的五个拨位开关,SW4,SW3,SW2,SW1,SW0为五个输入信号,可以代表五个表决的人,当五个人中有三个以上同意时,则表决通过,并将表决的结果在LD0上显示出来。

4. 其真值表:输入输出A B C D E F0 0 1 1 1 10 1 0 1 1 10 1 1 0 1 10 1 1 1 0 11 0 0 1 1 11 0 1 0 1 11 0 1 1 0 11 1 0 0 1 11 1 0 1 0 11 1 1 0 0 10 1 1 1 1 11 0 1 1 1 11 1 0 1 1 11 1 1 0 1 11 1 1 1 0 11 1 1 1 1 1others 0 5.输入与输出之间逻辑关系f=abc+abd+abe+acd+ace+ade+bcd+bce+bde+cde;三、主要仪器和设备主要仪器和设备:计算机,Basys 2开发板。

图1 Basys 2开发板四、ISE开发环境1、建立工程。

①选择菜单“File”→“New Preject”。

点击New②进入新建工程向导对话框输入工程名字:experiment1工程所在目录顶层源文件类型点击“Next”按纽②点击“Next”后,进入工程设置对话框。

对如下选项进行设置:Family:Spartan3EDevice:XC3S100EPackage:CP132TOP-Level Source:HDLSynthesis Tool:XST(VHDL/Verilog)Simulator:ISim(VHDL/Verilog)Preferred Language:Verilog③点击“Next”后,进入工程摘要对话框。

产品范围(product category)芯片的系列(Family)具体的芯片型号(Device)封装类型(Package)速度信息(speed)综合工具(Synthesis Tool)仿真工具(Simulator)喜欢的语言(VHDL/Verilog)点击“Next”按钮点击“Finish”按钮④点击“Finish”后,完成工程的创建。

工程名器件名字生成了空的工程框2、建立Verilog源文件。

①选中器件名字,点击鼠标右键,弹出一个快捷菜单。

②选中“New Source ”,进入新建源文件向导对话框,输入文件名。

选中器件名字,点击鼠标右键选中New Source0 IP 生成向导0 0 0 0 0 0 0 0 0原理图文件 用户文档文件 Verilog 模块模板文件 Verilog 测试平台模板文件 VHDL 模块模板文件 VHDL 库模板文件 VHDL 包模板文件 VHDL 测试平台模板文件 片上系统设计向导③点击“Next ”后,进入定义模块对话框,进行端口指定。

选择VHDL Module输入”experiment ”作为VHDL 模块的名字点击“Next”按钮指定端口名指定端口方向指定位宽点击“Next”④点击“Next”后,进入概要对话框。

点击“Finish”⑤点击“Finish”后,回到ISE主界面。

生成的experiment1.v文件添加代码到experiment1.v文件中⑥输入源程序代码:module experiment1(output [7:0] ld,input [2:0] sw);assign ld[0]=~sw[2]&~sw[1]&~sw[0];assign ld[1]=~sw[2]&~sw[1]& sw[0];assign ld[2]=~sw[2]& sw[1]&~sw[0];assign ld[3]=~sw[2]& sw[1]& sw[0];assign ld[4]= sw[2]&~sw[1]&~sw[0];assign ld[5]= sw[2]&~sw[1]& sw[0];assign ld[6]= sw[2]& sw[1]&~sw[0];assign ld[7]= sw[2]& sw[1]& sw[0];endmodule3、综合。

选中experiment1.v文件双击进行综合4、仿真。

①先选中Simulation,然后选中器件名字,点击鼠标右键,弹出一个快捷菜单。

②点击“New Source”后,进入选择源文件类型对话框。

③选择关联文件④概要⑤进入仿真测试文件编辑窗口⑥输入测试程序代码module test;reg [2:0] sw;wire [7:0] ld;experiment1 uut (.ld(ld),.sw(sw));initial beginsw = 8'b000;#100 sw = 3'b001;#100 sw = 8'b010;#100 sw = 8'b011;#100 sw = 8'b100;#100 sw = 8'b101;#100 sw = 8'b110;#100 sw = 8'b111;endendmodule⑦右键单击“Simulate Behavioral Model”弹出快捷菜单,点击“run”命令。

⑧进入ISim仿真器界面,选中Simulation菜单中的“Run”命令。

⑨显示仿真波形时序图。

5、编写约束文件。

①选中器件名字,点击鼠标右键,弹出一个快捷菜单。

选中器件名字,点击鼠标右键选中New Source②选中“New Source”,进入新建源文件向导对话框,输入约束文件名。

选中实现约束文件输入约束文件名点击“Next”按钮③点击“Next”后,进入概要对话框。

点击“Finish”按钮④点击“Finish”后,回到ISE主界面,编辑约束文件。

⑤输入约束文件代码NET "sw<2>" LOC="K3";NET "sw<1>" LOC="L3";NET "sw<0>" LOC="P11";NET "ld<7>" LOC="G1";NET "ld<6>" LOC="P4";NET "ld<5>" LOC="N4";NET "ld<4>" LOC="N5";NET "ld<3>" LOC="P6";NET "ld<2>" LOC="P7";NET "ld<1>" LOC="M11";NET "ld<0>" LOC="M5";6、实现7、生成编程文件8、下载双击进行实现选中experiment1.v文件双击生成编程文件选中experiment1.v文件①将Basys 2开发板右上角的Mode左边两个引脚(PC)用跳帽短接(JTAG模式)。

②将Basys 2开发板左下角的Power开关打开。

③打开Digilent Adept下载软件,浏览选中编程文件,并进行下载。

浏览选中下载文件编程下载9、功能测试五、实验步骤1、新建一个工程,命名为vote5.xise。

2、新建一个Verilog源文件,命名为vote5.v,编写源文件。

3、综合4、新建一个测试文件,命名为test.v,编写测试文件进行波形仿真。

5、新建一个约束文件,命名为vote.ucf。

6、实现7、生成编程文件8、下载9、功能测试六、实验报告要求1.写出设计思想及框图2.简述设计步骤和调试过程。

包括总体电路设计、相应模块设计,以及在ISE上完成的设计和仿真。

相关文档包括:Verilog HDL语言的源代码(程序要有详细的注释和功能说明)、引脚分配的约束文件、验证设计功能等设计的所有文档与调试的结果。