FPGA实验报告

FPGA实习报告

FPGA实习报告一、实习概况本次实习我进入了一家高科技公司,参与了FPGA(Field-Programmable Gate Array,现场可编程门阵列)相关的项目。

通过与团队成员合作,我了解了FPGA的基本知识和应用,并在项目中完成了一些任务。

在这次实习中,我学到了很多东西,也发现了自己的不足之处。

二、FPGA介绍FPGA是一种可编程逻辑器件,与ASIC(Application Specific Integrated Circuit,专用集成电路)相比,FPGA具有灵活性高、开发周期短等优点。

它可以根据需要进行编程,实现各种逻辑功能。

由于其广泛应用于通信、计算机、医疗等领域,我对FPGA技术充满了兴趣。

三、项目任务在本次实习中,我主要参与了一个数字信号处理项目。

具体任务如下:1. 学习FPGA编程语言:我首先学习了FPGA的编程语言,包括VHDL (VHSIC Hardware Description Language)和Verilog HDL(Hardware Description Language)。

这两种语言可以用于描述硬件电路,并在FPGA上实现。

3.进行性能优化:为了提高数字滤波器的性能,我进行了一系列优化工作。

首先,我对代码进行了优化,减少了资源占用和功耗。

同时,我对硬件设计进行了优化,使用并行计算等技术提高了滤波器的运算速度。

四、实习心得1.学到了很多知识:通过这次实习,我学到了很多关于FPGA的知识,包括编程语言、硬件设计、性能优化等方面。

这些知识对于我今后的学习和工作都有很大的帮助。

2.提高了动手能力:在项目中,我需要从零开始设计和实现一个数字滤波器。

通过不断的尝试和实践,我提高了自己的动手能力和解决问题的能力。

3.感受到了团队合作的重要性:在项目中,我和团队成员密切合作,共同解决了很多技术难题。

这让我意识到团队合作的重要性,团队的力量会比个人更加强大。

4.发现了自己的不足之处:在实习中,我发现了自己在硬件设计和性能优化方面的不足之处。

fpga 实验报告

fpga 实验报告FPGA实验报告引言:FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,广泛应用于数字电路设计和嵌入式系统开发中。

本实验报告旨在介绍FPGA的基本原理、应用领域以及实验过程和结果。

一、FPGA的基本原理FPGA由可编程逻辑单元(PLU)和可编程互连资源(ICR)组成。

PLU是FPGA 的核心,由逻辑门、寄存器和查找表等组成,通过编程可以实现不同的功能。

ICR用于连接PLU之间的信号线,实现不同模块之间的通信。

FPGA的可编程性使其具有灵活性和可重构性,适用于多种应用场景。

二、FPGA的应用领域1. 数字电路设计:FPGA可以实现各种数字电路,如逻辑门、加法器、乘法器等。

其可重构性使得电路设计师可以在硬件开发过程中进行快速迭代和调试,提高开发效率。

2. 通信系统:FPGA广泛应用于通信系统中的信号处理和协议转换等功能。

通过编程实现不同的通信协议,提高系统的兼容性和灵活性。

3. 图像处理:FPGA在图像处理领域有着广泛的应用。

通过并行计算的能力,可以实现实时图像处理和图像增强等功能,提高处理速度和效果。

4. 汽车电子:FPGA在汽车电子领域的应用越来越广泛。

例如,用于驾驶辅助系统、车载娱乐系统和车身控制等方面,提高汽车的安全性和性能。

三、实验过程和结果本次实验旨在设计一个简单的数字电路,并在FPGA上实现。

首先,我们使用HDL(Hardware Description Language)编写了一个4位二进制加法器的逻辑电路描述。

然后,使用FPGA开发工具将逻辑电路描述烧录到FPGA芯片中。

在实际操作中,我们按照实验指导书的步骤进行了硬件连线和编程配置。

通过FPGA开发工具提供的仿真功能,我们验证了逻辑电路的正确性。

在实际测试中,我们输入了两个4位的二进制数,并观察了输出结果。

实验结果表明,FPGA成功实现了4位二进制加法器的功能。

四、实验总结通过本次实验,我们深入了解了FPGA的基本原理和应用领域。

fpga实验报告

fpga实验报告FPGA实验报告引言随着科技的发展和计算机应用的广泛应用,人们对于计算机硬件的需求也越来越高。

在这个背景下,FPGA(Field Programmable Gate Array)作为一种可编程逻辑器件,被广泛应用于数字电路设计和嵌入式系统开发。

本篇文章将就FPGA的基本原理、实验设计和实验结果进行探讨。

一、FPGA的基本原理FPGA是一种可编程逻辑器件,它由一系列可编程逻辑单元(PLU)和可编程互连资源(PIM)组成。

PLU可以根据用户的需求进行编程,实现不同的逻辑功能。

PIM则用于连接不同的PLU,构成用户所需的电路结构。

FPGA的可编程性使得它能够根据不同的应用需求进行灵活的配置和重构,具有很高的可扩展性和适应性。

二、FPGA实验设计在FPGA实验设计中,我们通常需要进行电路设计、编程和仿真等步骤。

1. 电路设计FPGA实验中的电路设计是实验的核心环节。

我们需要根据实验要求,设计出符合要求的逻辑电路。

在设计过程中,我们可以使用硬件描述语言(HDL)如Verilog或VHDL来描述电路结构和功能。

通过对电路进行分析和优化,我们可以得到满足实验要求的电路设计。

2. 编程在电路设计完成后,我们需要将电路设计转化为FPGA可识别的编程文件。

这一步骤通常使用专门的软件工具来完成,如Xilinx ISE或Quartus II。

通过这些软件工具,我们可以将电路设计转化为FPGA可执行的bit文件。

3. 仿真在将编程文件下载到FPGA之前,我们通常需要进行仿真验证。

通过仿真,我们可以验证电路设计的正确性和性能。

仿真可以帮助我们发现潜在的问题和错误,从而提前解决,确保实验的顺利进行。

三、FPGA实验结果在实验过程中,我们通过将编程文件下载到FPGA上,使其实现我们设计的逻辑电路。

通过实验,我们可以获得电路的输出结果,并对其进行验证和分析。

1. 输出验证通过与设计预期结果进行比对,我们可以验证电路的输出是否符合预期。

FPGA实验报告

FPGA实验报告一、实验目的本次FPGA实验目的是通过使用FPGA开发板,了解FPGA的基本原理和应用,培养学生对数字电路设计的基本能力。

二、实验原理FPGA(Field-Programmable Gate Array)是一种可编程逻辑芯片,通过在芯片中加入多个查找表、可编程互连和触发器等基本模块,使得用户可以根据实际需求程序设计芯片的逻辑功能和互连关系。

FPGA的主要优点是能快速更新设计并且重配置灵活,而且速度快、功耗低。

本次实验我们使用的FPGA开发板是Xilinx Spartan-6系列,采用的开发环境是Xilinx ISE Design Suite。

三、实验内容1.实验用到的器件及端口我们使用的FPGA开发板上有多个输入输出端口,如LED灯、开关、按键等。

其中LED灯作为输出端口,开关和按键作为输入端口。

实验中,我们通过控制开关的状态,来控制LED灯的亮与灭。

2.设计电路我们的实验电路主要由一个FPGA芯片、多个LED灯、多个开关和按键等组成。

具体设计如下:(插入电路图)3.编写代码我们使用Verilog语言来描述逻辑电路的功能,并将其编写成代码。

代码示例如下:module led_controllerinput wire CLK,input wire [3:0] SWITCH,output reg [7:0] LEDcase(SWITCH)endcaseendendmodule4.烧录代码通过Xilinx ISE Design Suite的工具链,将上述代码综合、实现、生成比特文件。

然后通过JTAG接口将比特文件烧录到FPGA芯片中。

5.实验结果实验结果是通过观察LED灯的亮灭情况来验证代码的正确性。

根据开关的不同状态,LED灯的亮灭也不同。

四、实验总结通过本次实验,我们深入了解了FPGA的基本原理和应用,并且使用了Xilinx Spartan-6系列的开发板完成了LED控制的实验。

通过观察LED灯的亮灭情况,验证了我们编写的代码的正确性。

fpga实训报告

fpga实训报告本报告旨在总结和分享我在FPGA实训课程中的学习和实践经验。

我将介绍我在实训过程中所遇到的挑战、学到的知识以及对未来发展的展望。

1. 概述FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具有灵活性和可重构性,广泛应用于嵌入式系统、数字电路设计和计算机硬件加速等领域。

在本次实训中,我们团队学习了FPGA的基本原理和使用方法,并基于Verilog语言开发了几个具体的项目。

2. 实训内容2.1 FPGA基础知识我们首先学习了FPGA的基础知识,包括FPGA的结构和工作原理、FPGA开发流程、Verilog语言基础等。

通过理论学习和实际操作,我们对FPGA的内部结构和原理有了更深入的了解。

2.2 FPGA开发工具在实训中,我们使用了主流的FPGA开发工具。

通过熟练掌握这些工具的使用,我们能够进行FPGA的设计、仿真和下载等操作,为后续的实验项目做好准备。

2.3 FPGA实验项目在实训过程中,我们完成了多个FPGA实验项目,包括数字逻辑电路设计、时序电路设计、数码管显示、LED闪烁、有限状态机设计等。

通过这些项目,我们将理论知识应用到实际场景中,提高了自己的设计能力和实践能力。

3. 实训经验和收获3.1 团队合作在实训中,我们组成了小组合作完成各项实验项目。

通过合作,我们不仅学会了协作和沟通,还互相帮助解决问题,提高了团队凝聚力和协作能力。

3.2 动手实践FPGA实训的一个重要特点是强调实践操作。

通过大量的实验练习,我们不仅掌握了基本的FPGA开发技能,还了解了FPGA在各个领域中的广泛应用,并在实践中提高了自己的问题解决能力。

3.3 创新思维在一些项目中,我们需要设计和实现独特的功能,这要求我们发挥创新思维,灵活运用所学知识。

通过这个过程,我们培养了创新意识和解决实际问题的能力。

4. 未来展望通过FPGA实训的学习和实践,我对FPGA的应用和发展前景有了更深入的认识和理解。

FPGA实验报告

南京理工大学泰州科技学院FPGA系统设计实验报告教材名称:FPGA系统设计与应用开发指导教师:周莉莉实验室:4401学院(系):电子电气工程学院专业班级:10电信(1)班姓名:周根生朱守超学号:1002040149 1002040150实验学期:2013-2014学年第一学期总评成绩:教师签字:南京理工大学泰州科技学院FPGA系统设计实验报告目录实验一Max+plusII原理图设计输入 (1)实验二简单逻辑电路设计与仿真 (6)实验三组合逻辑电路设计(一) (11)实验四组合逻辑电路设计(二) (16)实验五有限状态机的设计 (26)实验六数字频率计 (32)南京理工大学泰州科技学院FPGA系统设计实验报告课程: FPGA系统设计班级:10电信1班姓名:周根生朱守超学号:10020401491002040150指导教师:周莉莉实验日期:实验题目:Max+plusII原理图设计输入成绩:一、设计任务采用原理图设计输入法,设计一个具有四舍五入功能的电路,其输入为4位二进制数,要求输入大于或等于0101时,电路输出为高电平,小于0101时电路输出为低电平。

二、设计过程根据设计要求列出四舍五入的真值表,如图1.1所示。

图1.1 四舍五入真值表由图1.1可得化简的表达式为OUT=A+BD+BC,由逻辑表达式可知,要设计的电路图有四个输入端(A,B,C,D)和一个输出端OUT,整个电路由两个2输入端的与门和一个3输入的或门组成。

启动MAX+plusII,新建Graphic Editor file文件,后缀为.gdf。

在编辑界面空白处双击左键,出现输入元件对话框如图1.2所示,在Symbol Name栏中直接输入元件的符号名OK,输入端(input),输出端(output),连接电路如图1.3所示。

图1.2 操作图1.3 原理图芯片型号选择单击Assign,选择Device,如图1.4所示。

图1.4 型号引脚命名双击PIN_NAME,使其变黑后输入引脚名,并保存文件然后编译,如图1.5所示。

FPGA实验报告整理版.doc

目录实验一分频器实验三 ADC0809 模数转换实验实验二七段数码管扫描显示实验四双向移位寄存器实验一分频器一、实验目的1.学习分频器的设计,进一步了解、熟悉和掌握FPGA开发软件Quartus II 的使用方法2.学习Verilog HDL 和VHDL的编程方法3.学会使用Vector Wave功能仿真4.掌握使用多种方法分配管脚二、实验内容编写一个分频器的Verilog 代码和VHDL代码并仿真,编译下载验证三、实验原理在数字电路中,时钟信号的分频是很常见的电路。

分频器除了可以对时钟信号频率做除以二的计算外,分频器同时很类似涟波计数器。

涟波计数器是计数器的一种,它属于异步设计。

因为触发器并非皆由同一个时钟信号同步操作,所以它非常节省电路面积。

本实验要设一个带选择的分频时钟,SEL[1:0]用于选择是几分频。

分频器设原理框图如图1所示:图1 分频器原理图从原理图中可见,核心板的时钟是50MHz ,通过sel[1:0]选择分频数,00:不分频;01:12.5M分频;10:25M四分频;11:50M分频。

采用SW1 ‐SW2 设置分频值,SW3 复位。

LED1为时钟的输出,通过调整SW1 、SW2 ,可以得到不同的闪烁频率。

引脚分配情况如表1所示表1 引脚分布情况四、实验步骤1.新建工程,取名为frediv ,如下图2所示。

图2 新建工程2.新建VHDL设计文件,选择“File|New ”,在New 对话框中选择Device Design Files下的VHDL File,单击OK,完成新建设计文件。

3.在新建设计文件中输入VHDL程序。

4.生成“Symbol ”文件,新建“Block Diagram/Schematic File”文件,在文件中添加刚刚生成的“Symbol ”以及输入输出管脚,最后完整的系统顶层模块图如图3 所示。

图3 顶层模块图5.保存文件,使用qsf或者tcl 进行管脚分配(相应的文件在本工程里面都可以找到)。

FPGA 实验报告

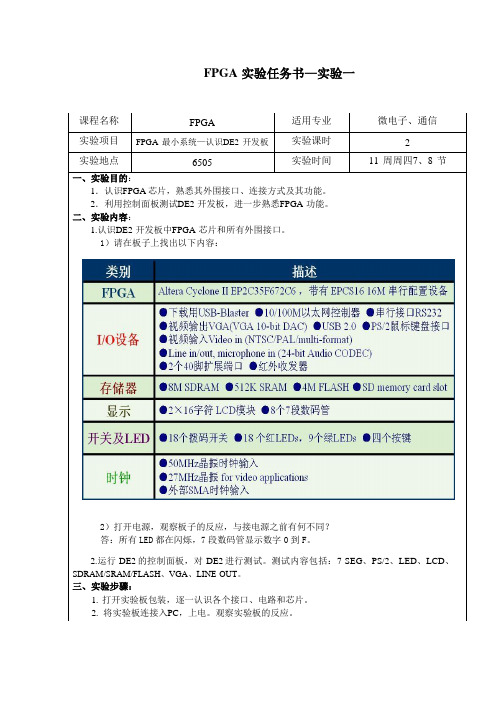

FPGA 实验任务书—实验一课程名称FPGA 适用专业微电子、通信实验项目FPGA 最小系统—认识D E2 开发板实验课时 2实验地点6505 实验时间11 周周四7、8 节一、实验目的:1.认识F PGA 芯片,熟悉其外围接口、连接方式及其功能。

2.利用控制面板测试D E2 开发板,进一步熟悉F PGA 功能。

二、实验内容:1.认识D E2 开发板中F PGA 芯片和所有外围接口。

1)请在板子上找出以下内容:2)打开电源,观察板子的反应,与接电源之前有何不同?答:所有LED都在闪烁,7段数码管显示数字0到F。

2.运行DE2的控制面板,对DE2进行测试。

测试内容包括:7-SEG、PS/2、LED、LCD、SDRAM/SRAM/FLASH、VGA、LINE OUT。

三、实验步骤:1. 打开实验板包装,逐一认识各个接口、电路和芯片。

2. 将实验板连接入P C,上电。

观察实验板的反应。

3.打开Q uartus II,运行第一个程序。

打开控制面板,逐一对主要外围接口进行测试,并记录。

4.运行 DE2_control_panel 目录下的 DE2_Control_Panel.exe,Open->Open_USB_port,下面即可对开发板进行测试了;图 2- 4 DE2 Control Panel5.PS2 和 7-SEG 的测试。

在开发板的插上键盘,输入字符即可显示在上图文本框中;设置HEX0 到 HEX7 的数字,点击 Set,开发板上相应位置的数码管显示相应数字。

6.LED 和 LCD 的测试。

如同上一步。

7.VGA 测试。

将一台显示器数据线连接到开发板的 VGA 口上。

选择 SRAM,将 File Length单选框选中。

点击下面的 Write a File to SRAM,打开DE2_demonstration\pictures\picture.dat;100%完成。

如下图示选 VGA 项。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA课程设计报告专业班级: 13电信1班学号: 130101011104姓名:汪远通指导老师:祝宏实验日期:2015.11.27—2015.12.18文华学院信息学部多功能数字钟电路设计一、设计题目多功能数字钟电路的分层次设计7二、设计要求技术指标设计一个具有时、分、秒计时的电子钟电路,按24小时制计时。

三、设计分析在设计一个比较复杂的数字电路或系统时,通常采用自上而下和自下而上的设计方法。

在自上而下设计中,先定义顶层模块,然后再定义顶层模块中用到的子模块。

而在自下而上设计中,底层的各个子模块首先被确定下来,然后将这些子模块组合起来构成顶层模块。

将电路分为不同层次和多个模块分别进行设计,然后将这些模块组合起来实现电路逻辑功能,这种方法通常被称为分层次的电路设计。

工作原理:振荡器产生的稳定的高频脉冲信号,作为数字钟的时间基准,再经分频器输出标准秒脉冲。

秒计数器计满60后向分计数器进位,分计数器计满60后向小时计数器进位,小时计数器按照24进制规律计数。

计数器的输出送译码显示电路,即可显示出数码(时间)。

计时出现误差时可以用校时电路进行校时和校分。

仿电台报时和定时闹钟为扩展电路,只有在计时主题电路正常运行的情况下才能进行功能扩展。

虚线框内的部分用Verilog HDL进行描述,然后用FPGA/CPLD 实现,译码显示电路用中规模IC实现,振荡器由集成电路定时器555与RC电路组成1kHz的多谐振荡器。

四、设计步骤①多功能数字钟主体电路逻辑设计:采用自下而上的设计方法,首先定义数字钟下层的各个模块,再调用这些模块组合成顶层的数字钟电路。

1.模24计数器的Verilog HDL设计小时计数器的计数规律为00-01-…-09-10-11-…-22-23-00…,即在设计时要求小时计数器的个位和十位均按8421BCD码计数。

//文件名:counter24.v(BCD计数:0~23)module counter24(CntH,CntL,nCR,EN,CP);input CP,nCR,EN; //分别为计时脉冲CP、清0信号、nCR和使能信号EN output [3:0] CntH,CntL; //计时计数器的十位和个位输出信号reg [3:0] CntH,CntL; //输出为8421BCD码always @(posedge CP or negedgenCR)beginif(~nCR) {CntH,CntL}<=8'h00; //异步清零else if (~EN) {CntH,CntL}<={CntH,CntL}; //对使能信号无效的处理else if ((CntH>2)||(CntL>9)||((CntH==2)&&(CntL>=3))){CntH,CntL}<=8'h00; //对小时计数器出错的处理else if ((CntH==2)&&(CntL<3)) //进行20-23计数beginCntH<=CntH; CntL<=CntL+1'b1;endelse if (CntL==9) //小时十位级的计数beginCntH<=CntH+1'b1; CntL<=4'b0000;endelse //小时个位的计数beginCntH<=CntH; CntL<=CntL+1'b1;endendendmodule2.模60计数器的Verilog HDL设计分和秒计数器的计数规律为00-01-…-09-10-11-…-58-59-00…,可见个位计数器从0~9计数,是一个十进制计数器;十位计数器则从0~5计数,是一个六进制计数器。

设计时,可以先分别设计一个十进制计数器模块(counter8.v)和一个六进制计数器模块(counter6.v),然后将这两个模块组合起来,构成六十进制计数器。

//counter60.v (BCD:00~59)//六十进制计数器:调用十进制和六进制底层模块构成module counter60(Cnt,nCR,EN,CP);inputCP,nCR,EN;output [7:0] Cnt; //模六十计数器的输出信号wire [7:0] Cnt; //输出为8421BCD码wire ENP; //计数器十位的使能信号(中间变量) counter10 UC0 (Cnt[3:0],nCR,EN,CP); //计数器的个位counter6 UC1 (Cnt[7:4],nCR,ENP,CP); //计数器的十位assign ENP=(Cnt[3:0]==4'h9); //产生计数器十位的使能信号endmodule//counter10.v (BCD:0~9)module counter10(Q,nCR,EN,CP);inputCP,nCR,EN;output [3:0] Q;reg [3:0] Q;always @ (posedge CP or negedgenCR)beginif (~nCR) Q<=4'b0000; //nCR=0,计数器被异步清零else if (~EN) Q<=Q; //EN=0,暂停计数else if (Q==4'b1001) Q<=4'b0000;else Q<=Q+1'b1; //计数器增1计数endendmodule//counter6.v (BCD:0~5)module counter6(Q,nCR,EN,CP);inputCP,nCR,EN;output [3:0] Q;reg [3:0] Q;always @ (posedge CP or negedgenCR)beginif (~nCR) Q<=4'b0000; //nCR=0,计数器被异步清零else if(~EN) Q<=Q; //EN=0,暂停计数else if(Q==4'b0101) Q<=4'b0000;else Q<=Q+1'b1; //计数器增1计数endendmodule3.数字钟主体电路的Verilog HDL设计//top_clock.vmoduletop_clock(Hour,Minute,Second,_1Hz,nCR,AdjMinKey,AdjHrKey);input _1Hz,nCR,AdjMinKey,AdjHrKey; //定义输入端口变量output [7:0] Hour,Minute,Second; //定义输出端口变量wire [7:0] Hour,Minute,Sncond; //说明输出变量类型supply1 Vdd; //定义VDD为高电平wire MinCP,HrCP; //分别为分钟、小时计数器时钟信号(中间变量) //Hour:Minute:Second countercounter60 UT1 (Second,nCR,Vdd,_1Hz); //秒计数器counter60 UT2 (Minute,nCR,Vdd,~MinCP); //分计数器counter24 UT3 (Hour[7:4],Hour[3:0],nCR,Vdd,~HrCP); //小时计数器//产生分钟计数器时钟信号AdjMinkey=1,校正分钟;Adjminkey=0,分钟正常计时assignMinCP=AdjMinKey ? _1Hz:(Second==8'h59);//产生小时计数器时钟信号。

AdjHrkey=1,校正小时;AdjHrkey=0,小时正常计时assignHrCP = AdjHrKey ? _1Hz:({Minute,Second}==16'h5959);endmodule数字钟主体电路包括正常计时和对时间进行校正两部分电路,其Verilog HDL为top_clock。

整个程序分为两个层次三个模块,底层有两个六十进制计数器模块(counter60.v)和一个二十四进制计数器模块(counter24.v),这三个模块组成一个顶层模块(top_clock.v)完成数字钟的主要功能。

又由于六十进制计数器模块由两个下层模块组成,所以整个程序实际上形成三个层次。

电路的工作工程:对小时和分钟进行校正的控制端分别为AdjHrkey和AdjMinkey,进行时间调整,AdjHrkey和AdjMinkey均为高电平,此时将1Hz信号直接输入到小时、分钟计数器,每秒钟来1个时钟信号,计数器加1计数,就可以实现对小时和分钟的校正。

正常计时时,秒计数器接受分频器送来的标准秒脉冲信号,每隔1秒钟,计数器的值增1,当秒计数器计到59秒时,产生的输出信号作为分计数器的时钟信号,使分计数器加1,分、秒计数器同时计到最大值(59分59秒)时,产生的输出信号作为小时计数器的时钟信号,使小时计数器加1,从而实现计时功能。

程序中,MinCP和HrCp分别为分钟计数器和小时计数器的时钟信号,将程序"assign MinCP=AdjMin ? _1Hz:(Second==8'h59);"综合后,会得到一个2选1数据选择器电路。

当AdjMinkey=1时,选择1Hz信号作为分钟计数器的时钟信号MinCP,实现分钟校正;当AdjMinkey=0时,选择秒计数器进位信号(Second==8'h59)作为分钟计数器的时钟信号MinCP,实现分钟正常计时。

小时计数器时钟信号HrCP的选择原理类似。

②多功能数字钟扩展电路逻辑设计:1.仿电台正点报时模块的Verilog HDL设计//Radio.vmodule Radio (ALARM_Radio,Minute,Second,_1kHzIN,_500Hz);input _1kHzIN,_500Hz; //定义输入端口变量input [7:0]Minute,Second;output ALARM_Radio; //定义输入端口变量regALARM_Radio; //说明变量的类型always@(Minute or Second) //generate alarm signal if(Minute == 8'h59)case (Second)8'h51,8'h53,8'h55,8'h57:ALARM_Radio= _500Hz;8'h59:ALARM_Radio= _1kHzIN;default:ALARM_Radio=1'b0;endcaseelseALARM_Radio=1'b0;endmodule仿广播电台正点报时模块的程序为Radio.v。