FC(倒装)

倒装工艺FC和扇出工艺FOWLP第一部分

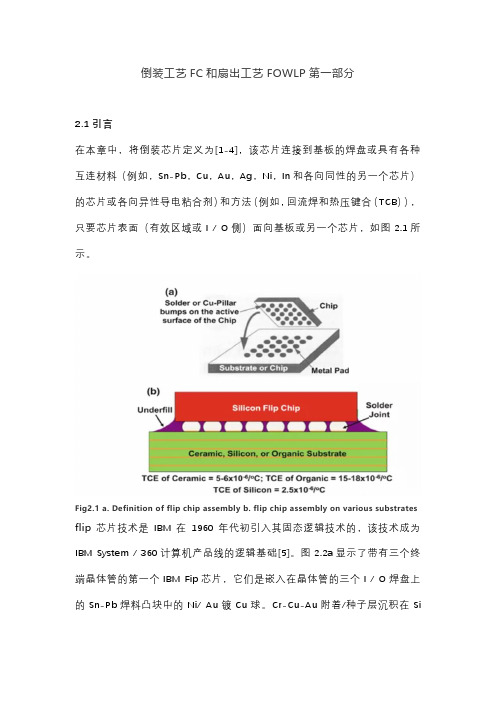

倒装工艺FC和扇出工艺FOWLP第一部分2.1引言在本章中,将倒装芯片定义为[1-4],该芯片连接到基板的焊盘或具有各种互连材料(例如,Sn-Pb,Cu,Au,Ag,Ni,In和各向同性的另一个芯片)的芯片或各向异性导电粘合剂)和方法(例如,回流焊和热压键合(TCB)),只要芯片表面(有效区域或I / O侧)面向基板或另一个芯片,如图2.1所示。

Fig2.1 a. Definition of flip chip assembly b. flip chip assembly on various substrates flip芯片技术是IBM在1960年代初引入其固态逻辑技术的,该技术成为IBM System / 360计算机产品线的逻辑基础[5]。

图2.2a显示了带有三个终端晶体管的第一个IBM Fip芯片,它们是嵌入在晶体管的三个I / O焊盘上的Sn-Pb焊料凸块中的Ni/ Au镀Cu球。

Cr-Cu-Au附着/种子层沉积在Si芯片上的Al-Si接触垫和焊料凸点之间。

图2.2b显示了在陶瓷基板上的第一个IBM倒装芯片组件(三个芯片)。

随着I / O的增加,铜球被焊料凸块代替。

所谓的C4(受控塌陷芯片连接)技术[6]利用沉积在芯片上可湿性金属端子上的高铅焊料凸点和基板上可湿性焊料端子的匹配占地面积。

焊有凸点的倒装芯片与基板对齐,并且通过回流焊锡同时制造所有焊点。

今天,倒装芯片技术的应用已扩展到[7-12]芯片对芯片,面对面和面对面。

图2.3显示了Amkor的DoublePOSSUM软件包[12]。

可以看出,封装实际上是由两个层次的嵌套模具定义的。

这三个子模具是倒装芯片,固定在较大的母模上,然后再固定在最大的祖母模上。

然后将祖母芯片倒装芯片到封装基板上。

子管芯和子管芯之间的凸点是微型凸块(带焊料盖的铜柱)。

在母模和祖母模之间以及祖母模和封装基板之间使用C4凸块。

倒装芯片技术已广泛用于大型机,服务器,个人计算机,笔记本电脑,智能手机,平板电脑,游戏等的处理器,网络,电信等的专用集成电路(ASIC)和存储器大部分的倒装芯片组件都大量销售。

声表面波器件工艺原理-9倒装焊工艺原理

九,声表器件倒装焊工艺原理序:倒装芯片(FC)技术,是在芯片的焊接区金属上制作凸焊点,然后将芯片倒扣在外壳基座上,以实现机械性能和电性能的连接,由于FC是通过凸焊点直接与底座相连,因此与其它互连技术相比,FC具有最高的封装密度、最小的封装尺寸(线焊可焊的最小陶瓷外壳为3×3mm,而FC可以作到芯片级)、最好的高频性能(电感小)、最小的高度、最轻的重量,以及产品高可靠、生产高工效等。

倒装焊工艺:主要由UBM的形成、凸点的制作、倒装焊接三部分组成。

(一)UBM的形成:当凸焊点材料与芯片上的焊接区金属不能很好浸润粘附时(或接触电阻大,或热匹配差,或两种材料间易形成会导致键合强度降低的金属间化合物),需要在凸焊点与芯片压焊块之间置入一层既能与芯片焊接区金属良好粘附、又能与凸焊点良好浸润、还能有效阻挡两者之间相互反应扩散的金属膜(UBM),因我们无法找到可同时满足上述要求的材料,所以通常UBM由多层金属膜组成。

(说明:与凸点连接的还有底座上相应的焊接点,由于在底座制作时该部位已镀有多层金属,能满足要求,固在此不于讨论。

)1,对UBM的各层要求及材料选择:1)粘附层:要求与铝膜及钝化层间的粘附性好,低阻接触,热膨涨系数接近,热应力小。

常选用材料有:Cr、Ti、Ti-W、Al、V等,因它们与Al浸润性很好,固该层可较薄。

2)扩散阻挡层:能有效阻挡凸焊点材料与铝间的相互扩散,以免形成不利的金属间化合物,特别是金凸焊点,在高温下与铝可生成Al2Au、AlAu、AlAu2、Al2Au5等脆性金属间化合物及在接触处相互扩散形成空洞,导致键合强度降低甚至失效。

该层常用材料有:Ti、Ni、Cu、Pd、Pt、Ti-W等。

(当用软焊料如PbSn作凸点时,由于其回流时会吃掉浸润层,直接与阻挡层接触;此时阻挡层应足够厚,且与凸点相浸润,不反应产生有害物)3)浸润层:要求一方面能和凸焊点材料良好浸润,可焊性好,且不会形成不利于键合的金属间化合物;另一方面还能保护粘附层和阻挡层金属不被氧化、粘污。

倒装工艺FC和扇出工艺FOWLP第三部分

2.7 Preassembly Underfill对于预装底部填充,底部填充的应用是在基板或晶圆上,并且在倒装芯片组装之前。

G4 [137]首次提出了带有底漆的C4凸块的回流焊,被称为NUF。

如图2.16c所示,Amkor[138]首先研究了在基板上填充非导电性胶(TC-NCP)的C2凸点的高结合力TCB [138],已将其用于为三星的Galaxy智能手机组装高通公司的SNAPDRAGON应用处理器。

在图2.37中NUF和NCP底料可以旋转,用针头分配或真空辅助。

通过从玻璃上芯片技术中学习,研究了C2凸点在晶圆上具有非导电膜(NCF)填充的高结合力TCB。

例如,三洋[139],日立[140、141],东北[142、143],陶氏[144],海力士[145],KAIST/三星[146、147],Amkor / Qualcomm [148]和东丽[ 149–151]用于2.5D / 3DIC集成[7–10]。

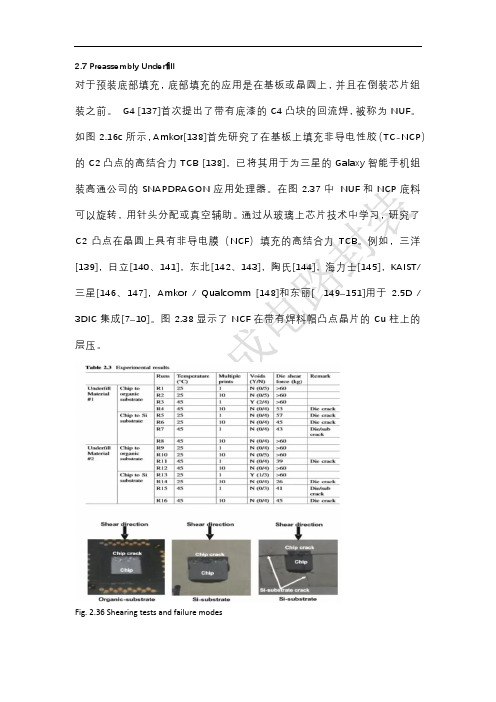

图2.38显示了NCF在带有焊料帽凸点晶片的Cu柱上的层压。

Fig. 2.36 Shearing tests and failure modes三星已经在其基于TSV的双数据速率4型动态随机存取存储器(DRAM)上生产了用于C2芯片和NCF的高键合力TCB(从叠层晶圆切割后)以进行3D IC集成,图2.38,并由Hynix在AMD图形处理器单元(GPU)代码名为Fiji的高带宽内存(HBM)上进行。

这个3D立方体由高强度TCB的C2芯片和NCF一次堆叠在一起,每个芯片需要* 10 s的时间填充胶膜,焊料熔化,胶膜固化和焊料巩固。

吞吐量是个问题!为了解决这个问题,Toray [150,151]提出了一种集体粘合方法,如图2.39所示。

可以看出,带有NCF的C2芯片是在温度= 80°C的阶段上预粘结的(粘结力= 30 N,温度= 150°C,时间<1 s)。

对于后期粘合(第一步(3 s):粘合力= 50 N,温度=220–260°C,第二步(7 s):粘合力= 70 N,温度= 280°C),初期温度= 80°C。

倒装芯片FC技术

倒装芯片FC技术一、SMT技术天地http://www.sm /二、新技术简介倒装芯片在产品成本,性能及满足高密度封装等方面体现出优势,它的应用也渐渐成为主流。

由于倒装芯片的尺寸小,要保证高精度高产量高重复性,这给我们传统的设备及工艺带来了挑战。

器件的小型化高密度封装形式越来越多,如多模块封装(MCM)、系统封装(SiP)、倒装芯片(FC,Flip-Chip )等应用得越来越多。

这些技术的出现更加模糊了一级封装与二级装配之间的界线。

毋庸置疑,随着小型化高密度封装的出现,对高速与高精度装配的要求变得更加关键,相关的组装设备和工艺也更具先进性与高灵活性。

由于倒装芯片比BGA 或CSP 具有更小的外形尺寸、更小的球径和球间距、它对植球工艺、基板技术、材料的兼容性、制造工艺,以及检查设备和方法提出了前所未有的挑战。

器件的小型化高密度封装形式越来越多,如多模块封装(MCM)、系统封装(SiP)、倒装芯片(FC,Flip-Chip)等应用得越来越多。

这些技术的出现更加模糊了一级封装与二级装配之间的界线。

毋庸置疑,随着小型化高密度封装的出现,对高速与高精度装配的要求变得更加关键,相关的组装设备和工艺也更具先进性与高灵活性。

由于倒装芯片比BGA或CSP具有更小的外形尺寸、更小的球径和球间距、它对植球工艺、基板技术、材料的兼容性、制造工艺,以及检查设备和方法提出了前所未有的挑战。

1.倒装芯片的发展历史倒装芯片具备以下特点:基材是硅;电气面及焊凸在器件下表面;球间距一般为4-14mil、球径为2.5-8mil、外形尺寸为1-27mm;组装在基板上后需要做底部填充。

其实,倒装芯片之所以被称为“倒装”,是相对于传统的金属线键合连接方式(Wire Bonding)与植球后的工艺而言的。

传统的通过金属线键合与基板连接的芯片电气面朝上(图1),而倒装芯片的电气面朝下(图2),相当于将前者翻转过来,故称其为“倒装芯片”。

在圆片(Wafer)上芯片植完球后(图3),需要将其翻转,送入贴片机,便于贴装,也由于这一翻转过程,而被称为“倒装芯片”。

倒装封装(FC)方案(一)

倒装封装(FC)方案背景与目标随着中国半导体产业的快速发展,传统封装技术已无法满足市场对高性能、高可靠性产品的需求。

倒装封装(FC)技术作为第三代封装技术,具有高密度、高性能、低成本等优势,成为产业结构改革的重要方向。

本方案旨在推广倒装封装技术在中国的应用,促进半导体产业的发展。

工作原理倒装封装(FC)技术是一种基于芯片底部连接的封装方法。

通过在芯片底部制作凸点,实现与基板的连接。

该技术可实现更高的I/O密度、更短的连接距离和更好的电性能。

此外,FC技术还具有高可靠性和低成本的优点。

实施计划步骤1.技术研究与开发(R&D): 首先,进行必要的技术研究与开发,包括凸点制作、芯片与基板连接技术、底部填充材料等关键技术。

2.设备采购与调试: 根据技术要求,采购相应的生产设备,并进行调试与验证,确保设备的稳定性和可靠性。

3.小批量试产: 在技术验证通过后,进行小批量试产,进一步验证生产流程和产品性能。

4.大规模量产: 在小批量试产成功后,进行大规模量产,以满足市场需求。

5.持续改进与优化: 根据市场反馈和生产数据,不断优化生产工艺和流程,提高产品质量和生产效率。

适用范围倒装封装技术适用于多种领域,如移动通信、汽车电子、云计算等。

特别是对于高性能、高可靠性、低成本的产品需求,倒装封装具有显著优势。

创新要点1.凸点制作技术创新: 开发适用于倒装封装的凸点制作技术,实现高密度、高性能的连接。

2.材料选择与优化: 选择合适的底部填充材料和其他相关材料,确保产品的可靠性和性能。

3.生产流程优化: 通过工艺研究和设备调试,实现生产流程的优化,提高生产效率和产品质量。

4.市场推广与应用拓展: 加强与客户的沟通和合作,将倒装封装技术推广到更多领域和应用场景。

预期效果预计通过本方案的实施,可以带来以下预期效果:1.提高半导体产业的技术水平和竞争力;2.促进中国半导体产业的结构改革和升级;3.满足市场对高性能、高可靠性产品的需求;4.提高企业的生产效率和产品质量;5.增强中国半导体产业的国际竞争力。

31Fc150倒装焊机结构1对准...

JSM-6390 :电子枪为钨灯丝的SEM

53

(1)真空系统

先用RP将电子枪和试样室抽真空(预抽)

54

(2)电子束系统

a)电子枪: 钨灯丝,用于产生电

子

b)磁透镜: 用于聚焦电子束

作用:将聚焦后的细小的 电子束在样品表面扫描

55

(3)成像系统

主要用于收集电子 束系统产生的各种 信息:二次电子、 背散射电子相应的 接收器。

D

=

d0

tan α c

临界分辨本领 = 电子束入射半角

αo一般为1mrad

故:景深为最小可分辨的1000倍

51

SEM分类

热电子发射SEM(钨灯丝或六硼化镧) 场发射SEM

钨灯丝

六硼化镧单晶

场发射尖端(钨单晶)

52

JSM-6390结构

真空柱 成像系统 样品室

真空泵

电子枪

电子束系统

(1)真空系统

(真空柱+真空泵)

分辨率 μm

较高

性能 精度 线宽 μm μm

较高 较窄

样品要求

切深 μm

样品材料

样品 大小

样品 厚度μm

浅

GaAs、 InP

≤4inch

≤100

钻石刀 划片机

一般

一般 较窄

浅

Sapphir e、GaN

≤3inch

≤100

激光 划片机

砂轮 划片机

高 一般

高

窄

较深

Sapphir e、GaN

≤3inch

≤100

一般 一般 深

Si、 Glass

≤8inch 一般均可

FEMC的技术难点与产品应用

芯片级 封装

传统PPA、 支架式 PCT、EMC 封装 支架

陶瓷和COB封装约占LED封装器件的3%,EMC约占20%,PLCC约占75%,支架式封装占目前LED封装的大 部分,在支架式封装中导入倒装芯片,对传统封装,将是一次革命

三、FEMC的产品优势

国内首

FEMC

热阻/结温 电压 饱和电流 热稳态流明 贴装便利性 成本优势 生产规模及良 率 特点 ☆☆☆☆☆ ☆☆☆☆☆ ☆☆☆☆☆ ☆☆☆☆☆ ☆☆☆☆☆ ☆☆☆☆☆ ☆☆☆☆☆ 3D 支架导入倒装芯片

FEMC的技术难点与产品应用

陈华

研发总监

提 纲

一、什么是FEMC 二、支架式倒装的意义 三、FEMC的产品优势 四、FEMC的产品规格及应用领域 五、支架式倒装封装的实现方式

一、什么是FEMC

FEMC = FC倒装芯片 + EMC支架

二、支架式倒装的意义

倒装芯片及倒装封装市场预期

Source: LED Packaging 2014,Yole Development, October 2014

单颗105lm以上

12颗LED全串连接

吸顶灯、筒灯

采用FEMC

整个模组光通 量大于3700lm 1颗FEMC 3030可替代2颗5730,可减少贴片 数量,增加效率,降低成本。 当前市场在吸顶灯、筒灯方案使用 5730(0.5W)为N串*2并方案。

球泡灯

2525--9V/100mA规格

FEMC25 5℃以上。

际领 国 ! 家

先!

普通SMD

☆☆☆ ☆☆☆ ☆☆☆ ☆☆ ☆☆☆☆☆ ☆☆☆☆ ☆☆☆☆☆

陶瓷(FC)

☆☆☆☆ ☆☆☆☆☆ ☆☆☆☆☆ ☆☆☆☆ ☆☆☆☆ ☆☆ ☆☆

FC简介

B. 压力烘箱原理视图:

C. Underfill 点胶模拟(Glass die):

Underfill 点胶视图

14

Thanks!

点胶机:Protec

Normal & Pressure烘箱

Nozzle Epoxy PCB

点胶前

Underfill

点胶后

SAT扫描

13

倒装芯片封测流程

Underfill (底部填充-CUF):

A. 毛细作用及原理视图:指液体在细管状 物体内侧,由于内聚力与附着力的差异、 克服地心引力而上升的现象;

倒装芯片封测流程

Pre-bake

基板预烘烤 锡膏印刷 表面贴装

UF Pre-bake Plasma UF

UF预烘烤 离子清洗 UF点胶 UF胶固化

Chip mount 上板&S/M Pre-bake FCA Reflow

SMT

Printing

UF

上Carrier 基板预烘烤 芯片倒装 回流炉 去Flux清洗 Fail

UF Cure

SAT 清洗 烘烤 3/O QA

Pass 3rd 检验 QA 3rd 检验 下Carrier

SAT抽检 抽检基板清洗 抽检基板除湿

FCA

Deflux

下板

倒装芯片封测流程

Surface Mount Technology (表面元件贴装):

通过锡膏印刷的方式进行元件贴装,将电容、电阻、电感等元器件贴焊于基板上.

Die attach

Process simulation

倒装芯片封测流程

Flipchip Attach (芯片倒装):

芯片倒装Process 产品贴装之后通过X-ray确认芯片贴装效果,含芯片偏移/虚焊/桥接 /Bump空洞等确认项.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

倒装芯片

Flip chip(倒装芯片):一种无引脚结构,一般含有电路单元。

设计用于通过适当数量的位于其面上的锡球(导电性粘合剂所覆盖),在电气上和机械上连接于电路。

起源于60年代,由IBM率先研发出,具体原理是在I/Opad上沉积锡铅球,然后将芯片翻转加热利用熔融的锡铅球与陶瓷板相结合,此技术已替换常规的打线接合,逐渐成为未来封装潮流。

Flip Chip既是一种芯片互连技术,又是一种理想的芯片粘接技术.早在30年前IBM公司已研发使用了这项技术。

但直到近几年来,Flip-Chip已成为高端器件及高密度封装领域中经常采用的封装形式。

今天,Flip-Chip封装技术的应用范围日益广泛,封装形式更趋多样化,对Flip-Chip封装技术的要求也随之提高。

同时,Flip-Chip也向制造者提出了一系列新的严峻挑战,为这项复杂的技术提供封装,组装及测试的可靠支持。

以往的一级封闭技术都是将芯片的有源区面朝上,背对基板和贴后键合,如引线健合和载带自动健全(TAB)。

FC则将芯片有源区面对基板,通过芯片上呈阵列排列的焊料凸点实现芯片与衬底的互连.硅片直接以倒扣方式安装到PCB从硅片向四周引出I/O,互联的长度大大缩短,减小了RC延迟,有效地提高了电性能.显然,这种芯片互连方式能提供更高的I/O密度.倒装占有面积几乎与芯片大小一致.在所有表面安装技术中,倒装芯片可以达到最小、最薄的封装。

Flip chip又称倒装片,是在I/O pad上沉积锡铅球,然后将芯片翻转佳热利用熔融的锡铅球与陶瓷机板相结合此技术替换常规打线接合,逐渐成为未来的封装主流,当前主要应用于高时脉的CPU、

GPU(GraphicProcessor Unit)及Chipset 等产品为主。

与COB相比,该封装形式的芯片结构和I/O端(锡球)方向朝下,由于I/O引出端分布于整个芯片表面,故在封装密度和处理速度上Flip chip已达到顶峰,特别是它可以采用类似SMT技术的手段来加工,因此是芯片封装技术及高密度安装的最终方向。

倒装片连接有三种主要类型C4(Controlled Collapse Chip Connection)、DCA(Direct chip attach)和FCAA(Flip Chip Adhesive Attachement)。

C4是类似超细间距BGA的一种形式与硅片连接的焊球阵列一般的间距为0.23、 0.254mm。

焊球直径为0.102、0.127mm。

焊球组份为97Pb/3Sn。

这些焊球在硅片上可以呈完全分布或部分分布。

由于陶瓷可以承受较高的回流温度,因此陶瓷被用来作为C4连接的基材,通常是在陶瓷的表面上预先分布有镀Au或Sn的连接盘,然后进行C4形式的倒装片连接。

C4连接的优点在于:

1)具有优良的电性能和热特性

2)在中等焊球间距的情况下,I/O数可以很高3)不受焊盘尺寸

的限制

4)可以适于批量生产

5)可大大减小尺寸和重量

DCA和C4类似是一种超细间距连接。

DCA的硅片和C4连接中

的硅片结构相同,两者之间的唯一区别在于基材的选择。

DCA采用的基

材是典型的印制材料。

DCA的焊球组份是97Pb/Sn,连接焊接盘上的焊料是共晶焊料(37Pb/63Sn)。

对于DCA由于间距仅为0.203、0.254mm共晶焊料漏印到连接焊盘上相当困难,所以取代焊膏漏印这种方式,在组装前

给连接焊盘顶镀上铅锡焊料,焊盘上的焊料体积要求十分严格,通常要比

其它超细间距元件所用的焊料多。

在连接焊盘上0.051、0.102mm厚的焊料由于是预镀的,一般略呈圆顶状,必须要在贴片前整平,否则会影响焊球

和焊盘的可靠对位。

FCAA连接存在多种形式,当前仍处于初期开发阶段。

硅片与基材

之间的连接不采用焊料,而是用胶来代替。

这种连接中的硅片底部可以有

焊球,也可以采用焊料凸点等结构。

FCAA所用的胶包括各向同性和各

向异性等多种类型,主要取决于实际应用中的连接状况,另外,基材的选

用通常有陶瓷,印刷板材料和柔性电路板。

倒装芯片技术是当今最先进的

微电子封装技术之一。

它将电路组装密度提升到了一个新高度,随着21

世纪电子产品体积的进一步缩小,倒装芯片的应用将会越来越广泛。

Flip-Chip封装技术与传统的引线键合工艺相比具有许多明显的优点,

包括,优越的电学及热学性能,高I/O引脚数,封装尺寸减小等。

Flip-Chip封装技术的热学性能明显优越于常规使用的引线键合工艺。

如今许多电子器件;ASIC,微处理器,SOC等封装耗散功率10-25W,甚至

更大。

而增强散热型引线键合的BGA器件的耗散功率仅5-10W。

按照工作条件,散热要求(最大结温),环境温度及空气流量,封装参数(如使用外

装热沉,封装及尺寸,基板层数,球引脚数)等,相比之下,Flip-Chip封装通常能产生25W耗散功率。

Flip-Chip封装杰出的热学性能是由低热阻的散热盘及结构决定的。

芯片产生的热量通过散热球脚,内部及外部的热沉实现热量耗散。

散热盘与

芯片面的紧密接触得到低的结温(θjc)。

为减少散热盘与芯片间的热阻,在两者之间使用高导热胶体。

使得封装内热量更容易耗散。

为更进一步改

进散热性能,外部热沉可直接安装在散热盘上,以获得封装低的结温(θjc)。

Flip-Chip封装另一个重要优点是电学性能。

引线键合工艺已成为高频及某些应用的瓶颈,使用Flip-Chip封装技术改进了电学性能。

如今许多

电子器件工作在高频,因此信号的完整性是一个重要因素。

在过去,2-3GHZ

是IC封装的频率上限,Flip-Chip封装根据使用的基板技术可高达10-40 GHZ 。