无锡华桑FPGA培训之modelsim仿真篇

Modelsim的仿真教程

ModelSim的仿真1.仿真的分类仿真过程是正确实现设计的关键环节,用来验证设计者的设计思想是否正确,及在设计实现过程中各种分布参数引入后,其设计的功能是否依然正确无误。

仿真主要分为功能仿真和时序仿真。

功能仿真是在设计输入后进行;时序仿真是在逻辑综合后或布局布线后进行。

1). 功能仿真( 前仿真)功能仿真是指在一个设计中,在设计实现前对所创建的逻辑进行的验证其功能是否正确的过程。

布局布线以前的仿真都称作功能仿真,它包括综合前仿真(Pre-Synthesis Simulation )和综合后仿真(Post-Synthesis Simulation )。

综合前仿真主要针对基于原理框图的设计; 综合后仿真既适合原理图设计, 也适合基于HDL 语言的设计。

2). 时序仿真(后仿真)时序仿真使用布局布线后器件给出的模块和连线的延时信息,在最坏的情况下对电路的行为作出实际地估价。

时序仿真使用的仿真器和功能仿真使用的仿真器是相同的,所需的流程和激励也是相同的;惟一的差别是为时序仿真加载到仿真器的设计包括基于实际布局布线设计的最坏情况的布局布线延时,并且在仿真结果波形图中,时序仿真后的信号加载了时延,而功能仿真没有。

后仿真也称为时序仿真或者布局布线后仿真,是指电路已经映射到特定的工艺环境以后,综合考虑电路的路径延迟与门延迟的影响,验证电路能否在一定时序条件下满足设计构想的过程,是否存在时序违规。

其输入文件为从布局布线结果中抽象出来的门级网表、Testbench 和扩展名为SDO 或SDF 的标准时延文件。

SDO 或SDF 的标准时延文件不仅包含门延迟,还包括实际布线延迟,能较好地反映芯片的实际工作情况。

一般来说后仿真是必选的,检查设计时序与实际的FPGA运行情况是否一致,确保设计的可靠性和稳定性。

2.仿真的作用1).设计出能工作的电路:因此功能仿真不是一个孤立的过程,其和综合、时序分析等形成一个反馈工作过程,只有这个过程收敛,各个环节才有意义。

modesim仿真使用教程

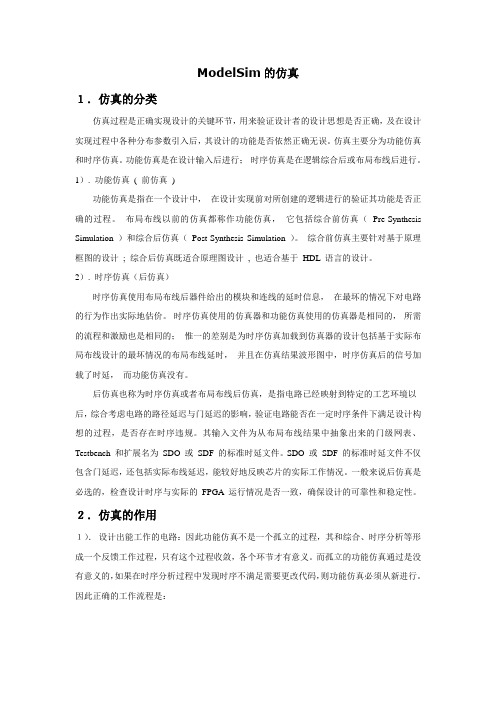

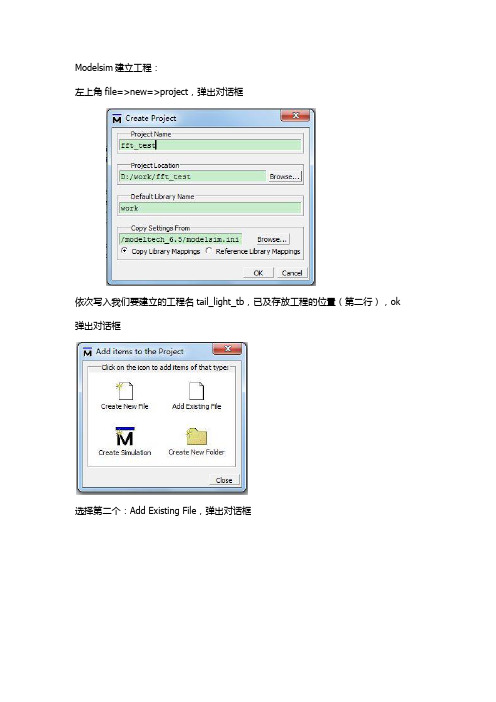

Modelsim建立工程:左上角file=>new=>project,弹出对话框依次写入我们要建立的工程名tail_light_tb,已及存放工程的位置(第二行),ok 弹出对话框选择第二个:Add Existing File,弹出对话框点击Browse,选择我们需要的文件(,此处我们需要4个文件,分别是led_matrix_mod.v,pulse_clk_nco.v,tail_light_mod.v, tail_light_tb.v)然后右击,弹出对话框,选择compile all,编译所有文件编译完成后,选择tool下面tcl选项,如图:弹出对话框选择tail_light_tb.tcl,打开弹出波形文件工程说明1逐行解释程序内部注释的有2设计思路见txt文档3每个模块的主要功能:tail_light_sys.v:开发板工程的顶层模块,用来连接各个子模块jitter_clear_mod.v:消抖模块,用来消除按键按下时带来的抖动tail_light_mod.v:汽车尾灯状态生成模块,根据不同的按键,解析成汽车尾灯的状态led_matrix_mod.v:led流水灯控制模块,根据刹车油门左右转等不同状态来控制led 流水灯的亮灭pulse_clk_nco.v:分频扫描模块,用于产生控制led流水灯速度的脉冲信号tail_light_tb.tcl:modelsim的脚本文件,可方便的进行modelsim仿真tail_light_tb.v:modelsim仿真的顶层文件,提供其仿真的时钟复位按键等模拟环境4:仿真波形简单说明按照上述操作结束后,弹出一个波形文件,点击上边的放大缩小等按钮,可方便观察波形本仿真主要观察模拟的4个按键,如下以及对应状态下的3组灯的变化状态,如下可点击放大按钮,看具体变化值,如下可点击左边的+号,可看每一个灯的变化,如下。

第4章 基于ModelSim的仿真

工作区

脚本区

命令输入

数据流窗口

数据流窗口(Dataflow)是一般仿真软件都提供的 一个通用窗口,通过该窗口可以跟踪设计中的物理连 接,跟踪设计中事件的传播,也可以用来跟踪寄存器、 网线和进程,极大地丰富了调试方法。数据流窗口中 可以显示进程(可以是 Verilog 的一个模块) 、信 号、网线和寄存器等,也可以显示设计中的内部连接。 窗口中有一个内置的符号表,映射了所有的 Verilog 基本门,例如与门、非门等,这些符号可以在数据流 窗口中显示。其他的 Verilog 基本组件可以使用模 块或者用户定义的符号在数据流窗口中显示。

22

6.开始仿真 点击workspace下的sim,点击count_tp,选择add add to wave 然后点run –all,开始仿真

23

7.退出仿真 在仿真调试完成后退出仿真,在主窗口中选择simulate end simulation

24

补充:

(1)也可以不加testbench,仿真步骤跟前面相似, 装载文件时双击muxtop 在sim中点击muxtop,add add to wave 对输入信号sel、a、b编辑测试波形

4.1.4 ModelSim调试功能

在波形窗口中监视信号,查看仿真的波形

改变当前目录到要变异的文件所在的目录 建立工作库并编译相关源文件 加载设计的激励文件 向波形窗口中添加项目,即要监视的信号 缩放波形显示 在波形窗口中使用光标 保存波形窗口格式

4.1.4 ModelSim调试功能

4.1.5功能仿真

功能仿真需要的文件

1.设计HDL源代码:可以使VHDL语言或Verilog语言。 2.测试激励代码:根据设计要求输入/输出的激励程序 3.仿真模型/库:根据设计内调用的器件供应商提供的模块而定,如:FIFO、 ADD_SUB等

重要】详细介绍使用modelsim对lpm作仿真的步骤操作

如何使用ModelSim對Megafunction或LPM作仿真? (SOC) (MegaCore) (ModelSim)Abstract在FPGA開發中,常會用到Altera所提供的Megafunction與LPM加速開發,這要如何使用ModelSim作仿真呢?Introduction使用環境:Quartus II 8.1 + ModelSim-Altera 6.3g_p1 + ModelSim SE 6.3e在(筆記) 如何使用ModelSim作前仿真與後仿真? (SOC) (Quartus II) (ModelSim)中,提到如何使用ModelSim對Verilog作仿真,包含前仿真與後仿真,若使用了Altera的Megafunction 與LPM,則仿真的方法稍有不同,本文分別使用ModelSim-Altera與ModelSim SE,並對Megafunction:dcfifo作仿真。

my_dcfifo.v / Verilog使用MegaWizard產生的dcfifo。

1// megafunction wizard: %FIFO%2// GENERATION: STANDARD3// VERSION: WM1.04// MODULE: dcfifo56// ============================================================7// File Name: my_dcfifo.v8// Megafunction Name(s):9// dcfifo10//11// Simulation Library Files(s):12// altera_mf13// ============================================================ 14// ************************************************************ 15// THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE!16//17// 8.1 Build 163 10/28/2008 SJ Full Version18// ************************************************************ 192021//Copyright (C) 1991-2008 Altera Corporation22//Your use of Altera Corporation's design tools, logic functions 23//and other software and tools, and its AMPP partner logic24//functions, and any output files from any of the foregoing25//(including device programming or simulation files), and any26//associated documentation or information are expressly subject 27//to the terms and conditions of the Altera Program License28//Subscription Agreement, Altera MegaCore Function License29//Agreement, or other applicable license agreement, including, 30//without limitation, that your use is for the sole purpose of31//programming logic devices manufactured by Altera and sold by 32//Altera or its authorized distributors. Please refer to the33//applicable agreement for further details.343536// synopsys translate_off37 `timescale 1 ps / 1 ps38// synopsys translate_on39module my_dcfifo (40 aclr,41 data,42 rdclk,43 rdreq,44 wrclk,45 wrreq,46 q,47 rdempty,48 rdusedw,49 wrfull);5051input aclr;52input [7:0] data;53input rdclk;54input rdreq;55input wrclk;56input wrreq;57output [7:0] q;58output rdempty;59output [4:0] rdusedw; 60output wrfull;6162wire sub_wire0;63wire sub_wire1;64wire [7:0] sub_wire2;65wire [4:0] sub_wire3;66wire rdempty = sub_wire0;67wire wrfull = sub_wire1;68wire [7:0] q = sub_wire2[7:0];69wire [4:0] rdusedw = sub_wire3[4:0];7071 dcfifo dcfifo_component (72 .wrclk (wrclk),73 .rdreq (rdreq),74 .aclr (aclr),75 .rdclk (rdclk),76 .wrreq (wrreq),77 .data (data),78 .rdempty (sub_wire0),79 .wrfull (sub_wire1),80 .q (sub_wire2),81 .rdusedw (sub_wire3)82// synopsys translate_off83 ,84 .rdfull (),85 .wrempty (),86 .wrusedw ()87// synopsys translate_on88 );89defparam90 dcfifo_component.intended_device_family = "Cyclone II",91 dcfifo_component.lpm_hint = "MAXIMIZE_SPEED=5,",92 dcfifo_component.lpm_numwords = 32,93 dcfifo_component.lpm_showahead = "OFF",94 dcfifo_component.lpm_type = "dcfifo",95 dcfifo_component.lpm_width = 8,96 dcfifo_component.lpm_widthu = 5,97 dcfifo_component.overflow_checking = "ON",98 dcfifo_component.rdsync_delaypipe = 4,99 dcfifo_component.underflow_checking = "ON",100 dcfifo_e_eab = "ON",101 dcfifo_component.write_aclr_synch = "OFF",102 dcfifo_component.wrsync_delaypipe = 4;103104105endmodule106107// ============================================================ 108// CNX file retrieval info109// ============================================================ 110// Retrieval info: PRIVATE: AlmostEmpty NUMERIC "0"111// Retrieval info: PRIVATE: AlmostEmptyThr NUMERIC "-1"112// Retrieval info: PRIVATE: AlmostFull NUMERIC "0"113// Retrieval info: PRIVATE: AlmostFullThr NUMERIC "-1"114// Retrieval info: PRIVATE: CLOCKS_ARE_SYNCHRONIZED NUMERIC "0"115// Retrieval info: PRIVATE: Clock NUMERIC "4"116// Retrieval info: PRIVATE: Depth NUMERIC "32"117// Retrieval info: PRIVATE: Empty NUMERIC "1"118// Retrieval info: PRIVATE: Full NUMERIC "1"119// Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone I I"120// Retrieval info: PRIVATE: LE_BasedFIFO NUMERIC "0"121// Retrieval info: PRIVATE: LegacyRREQ NUMERIC "1"122// Retrieval info: PRIVATE: MAX_DEPTH_BY_9 NUMERIC "0"123// Retrieval info: PRIVATE: OVERFLOW_CHECKING NUMERIC "0"124// Retrieval info: PRIVATE: Optimize NUMERIC "2"125// Retrieval info: PRIVATE: RAM_BLOCK_TYPE NUMERIC "0"126// Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0" 127// Retrieval info: PRIVATE: UNDERFLOW_CHECKING NUMERIC "0"128// Retrieval info: PRIVATE: UsedW NUMERIC "1"129// Retrieval info: PRIVATE: Width NUMERIC "8"130// Retrieval info: PRIVATE: dc_aclr NUMERIC "1"131// Retrieval info: PRIVATE: diff_widths NUMERIC "0"132// Retrieval info: PRIVATE: msb_usedw NUMERIC "0"133// Retrieval info: PRIVATE: output_width NUMERIC "8"134// Retrieval info: PRIVATE: rsEmpty NUMERIC "1"135// Retrieval info: PRIVATE: rsFull NUMERIC "0"136// Retrieval info: PRIVATE: rsUsedW NUMERIC "1"137// Retrieval info: PRIVATE: sc_aclr NUMERIC "0"138// Retrieval info: PRIVATE: sc_sclr NUMERIC "0"139// Retrieval info: PRIVATE: wsEmpty NUMERIC "0"140// Retrieval info: PRIVATE: wsFull NUMERIC "1"141// Retrieval info: PRIVATE: wsUsedW NUMERIC "0"142// Retrieval info: CONSTANT: INTENDED_DEVICE_FAMILY STRING "Cyclone II"143// Retrieval info: CONSTANT: LPM_HINT STRING "MAXIMIZE_SPEED=5," 144// Retrieval info: CONSTANT: LPM_NUMWORDS NUMERIC "32"145// Retrieval info: CONSTANT: LPM_SHOWAHEAD STRING "OFF"146// Retrieval info: CONSTANT: LPM_TYPE STRING "dcfifo"147// Retrieval info: CONSTANT: LPM_WIDTH NUMERIC "8"148// Retrieval info: CONSTANT: LPM_WIDTHU NUMERIC "5"149// Retrieval info: CONSTANT: OVERFLOW_CHECKING STRING "ON"150// Retrieval info: CONSTANT: RDSYNC_DELAYPIPE NUMERIC "4"151// Retrieval info: CONSTANT: UNDERFLOW_CHECKING STRING "ON"152// Retrieval info: CONSTANT: USE_EAB STRING "ON"153// Retrieval info: CONSTANT: WRITE_ACLR_SYNCH STRING "OFF"154// Retrieval info: CONSTANT: WRSYNC_DELAYPIPE NUMERIC "4"155// Retrieval info: USED_PORT: aclr 0 0 0 0 INPUT GND aclr156// Retrieval info: USED_PORT: data 0 0 8 0 INPUT NODEFVAL data[7..0] 157// Retrieval info: USED_PORT: q 0 0 8 0 OUTPUT NODEFVAL q[7..0]158// Retrieval info: USED_PORT: rdclk 0 0 0 0 INPUT NODEFVAL rdclk159// Retrieval info: USED_PORT: rdempty 0 0 0 0 OUTPUT NODEFVAL rdempty 160// Retrieval info: USED_PORT: rdreq 0 0 0 0 INPUT NODEFVAL rdreq161// Retrieval info: USED_PORT: rdusedw 0 0 5 0 OUTPUT NODEFVAL rdusedw [4..0]162// Retrieval info: USED_PORT: wrclk 0 0 0 0 INPUT NODEFVAL wrclk163// Retrieval info: USED_PORT: wrfull 0 0 0 0 OUTPUT NODEFVAL wrfull 164// Retrieval info: USED_PORT: wrreq 0 0 0 0 INPUT NODEFVAL wrreq165// Retrieval info: CONNECT: @data 0 0 8 0 data 0 0 8 0166// Retrieval info: CONNECT: q 0 0 8 0 @q 0 0 8 0167// Retrieval info: CONNECT: @wrreq 0 0 0 0 wrreq 0 0 0 0168// Retrieval info: CONNECT: @rdreq 0 0 0 0 rdreq 0 0 0 0169// Retrieval info: CONNECT: @rdclk 0 0 0 0 rdclk 0 0 0 0170// Retrieval info: CONNECT: @wrclk 0 0 0 0 wrclk 0 0 0 0171// Retrieval info: CONNECT: rdempty 0 0 0 0 @rdempty 0 0 0 0172// Retrieval info: CONNECT: rdusedw 0 0 5 0 @rdusedw 0 0 5 0173// Retrieval info: CONNECT: wrfull 0 0 0 0 @wrfull 0 0 0 0174// Retrieval info: CONNECT: @aclr 0 0 0 0 aclr 0 0 0 0175// Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components. all176// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo.v TRUE177// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo.inc FALSE178// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo p FALSE179// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo.bsf FALSE180// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo_inst.v FALSE181// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo_bb.v TRUE182// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo_waveforms.html TR UE183// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo_wave*.jpg TRUE184// Retrieval info: LIB_FILE: altera_mfmy_dcfifo_tb.v / Verilogdcfifo的testbench。

MODELSIM仿真

1、实验要求........................................................................... - 1 -2、八选一数据选择器的实现 .............................................. - 1 -2.1、八选一数据选择器的功能...................................... - 1 -2.2、八选一数据选择器的主程序.................................. - 2 -2.3、八选一数据选择器的激励程序.............................. - 2 -2.4采用modelsim对八选一数据选择器的仿真及分析- 3 - 3全加器的实现...................................................................... - 4 -3.1一位全加器的功能 ..................................................... - 4 -3.2全加器的主程序 ......................................................... - 5 -3.3全加器的激励模块 ..................................................... - 6 -3.4采用modelsim对全加器的仿真及分析 .................. - 7 -4、体会心得........................................................................... - 7 -1、实验要求(1)、熟悉verilog语言的语法并能够熟练的编写简单的程序实现相应的功能;(2)、用verilog语言编写八选一数据选择器和全加器的程序代码实现其功能;(3)、用verilog语言编写相应的激励代码用modelsim软件对八选一数据选择器和全加器进行相应的功能仿真;2、八选一数据选择器的实现2.1、八选一数据选择器的功能图2.1.1八选一数据选择器八选一数据选择器的数据输入端为:a,b,c,d,e,f,g,h八选一数据选择器的地址输入端为:s0,s1,s2八选一数据选择器的输出端为:out八选一数据选择器的功能:当S0S1S2=0时,输出out=a;当S0S1S2=1时,输出out=b;当S0S1S2=2时,输出out=c当S0S1S2=3时,输出out=d当S0S1S2=4时,输出out=e当S0S1S2=5时,输出out=f当S0S1S2=6时,输出out=g当S0S1S2=7时,输出out=h2.2、八选一数据选择器的主程序/* a,b,c,d,e,f,g,h为数据输入端口,s0,s1,s2为地址输入端口,out 为输出端口*/module option(a,b,c,d,e,f,g,h,s0,s1,s2,out);input [2:0] a,b,c,d,e,f,g,h;// a,b,c,d,e,f,g,h为输入端且为寄存器型数据input s0,s1,s2;// s0,s1,s2位输入端output [2:0] out; //out为输出端且为寄存器型reg [2:0] out;always@(a or b or c or d or e or f or g or h or s0 or s1 or s2)begincase({s0,s1,s2})3'd0 : out=a;3'd1 : out=b;3'd2 : out=c;3'd3 : out=d;3'd4 : out=e;3'd5 : out=f;3'd6 : out=g;3'd7 : out=h;endcaseendendmodule2.3、八选一数据选择器的激励程序module sti;reg [2:0] A,B,C,D,E,F,G,H;reg S0,S1,S2;wire [2:0] OUT;option dtg(A,B,C,D,E,F,G,H,S0,S1,S2,OUT);initialbeginA=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=0;#100A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=1;#100A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=0;#100A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=1;#100A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=0;#100A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=1;#100A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=1;S2=0;#100A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=1;S2=1;endendmodule2.4采用modelsim对八选一数据选择器的仿真及分析图2.4.1八选一数据选择器的仿真波形波形分析如下:输入数据为A=000,B=001,C=010,D=011,E=100,F=101,g=110,h=111;S0,S1,S2,为选择控制端,它们组成一个三位数,记为enable,控制数据的输出,其中S0为最高位,S1次之,S2为最低位。

modelsim使用教程

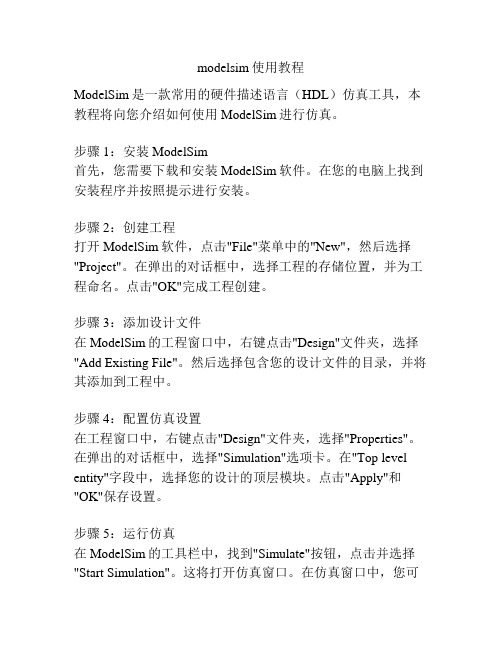

modelsim使用教程ModelSim是一款常用的硬件描述语言(HDL)仿真工具,本教程将向您介绍如何使用ModelSim进行仿真。

步骤1:安装ModelSim首先,您需要下载和安装ModelSim软件。

在您的电脑上找到安装程序并按照提示进行安装。

步骤2:创建工程打开ModelSim软件,点击"File"菜单中的"New",然后选择"Project"。

在弹出的对话框中,选择工程的存储位置,并为工程命名。

点击"OK"完成工程创建。

步骤3:添加设计文件在ModelSim的工程窗口中,右键点击"Design"文件夹,选择"Add Existing File"。

然后选择包含您的设计文件的目录,并将其添加到工程中。

步骤4:配置仿真设置在工程窗口中,右键点击"Design"文件夹,选择"Properties"。

在弹出的对话框中,选择"Simulation"选项卡。

在"Top level entity"字段中,选择您的设计的顶层模块。

点击"Apply"和"OK"保存设置。

步骤5:运行仿真在ModelSim的工具栏中,找到"Simulate"按钮,点击并选择"Start Simulation"。

这将打开仿真窗口。

在仿真窗口中,您可以使用不同的命令来控制和观察设计的行为。

步骤6:查看仿真结果您可以在仿真窗口中查看信号波形、调试设计并分析仿真结果。

在仿真窗口的菜单栏中,您可以找到一些常用的查看和分析工具,如波形浏览器、信号分析器等。

步骤7:结束仿真当您完成仿真时,可以选择在仿真窗口的菜单栏中找到"Simulate"按钮,并选择"End Simulation"以结束仿真。

modelsim新手入门仿真教程

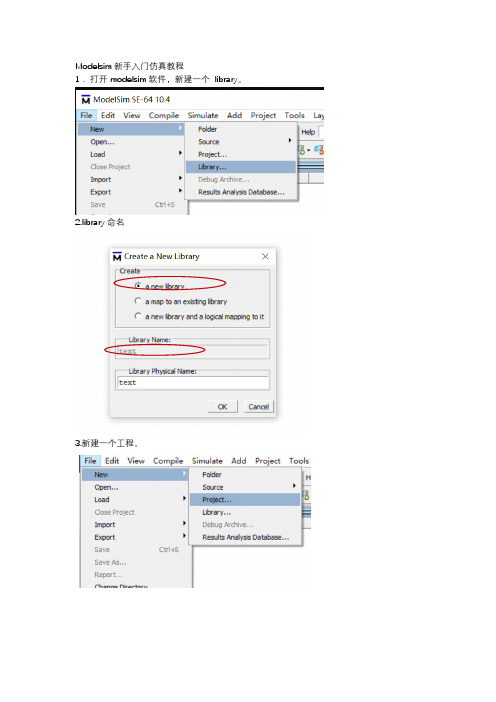

Modelsim新手入门仿真教程1.打开modelsim软件,新建一个library。

2.library命名3.新建一个工程。

3.出现下面界面,点击close。

4.新建一个verilog文件键入主程序。

下面以二分之一分频器为例。

文件代码:module half_clk(reset,clk_in,clk_out); input clk_in,reset;output clk_out;reg clk_out;always@(negedge clk_in)beginif(!reset)clk_out=0;elseclk_out=~clk_out;endendmodule编辑完成后,点击保存。

文件名要与module后面的名称相同。

5.再新建一个测试文件,步骤同上面新建的主程序文件,文件名后缀改为.vt程序代码如下:`timescale 1ns/100ps`define clk_cycle 50module top;reg clk,reset;wire clk_out;always #`clk_cycle clk=~clk;initialbeginclk=0;reset=1;#10 reset=0;#110 reset=1;#100000 $stop;endhalf_clk m0(.reset(reset),.clk_in(clk),.clk_out(clk_out));Endmodule6.添加文件,编译文件先右键点击左边空白处,选择add to project→existing File选择刚刚新建的两个文件。

按ctrl键可以同时选择两个,选择打开,下一步点击ok7选中其中一个,右键,选择complie→complie all出现两个勾,说明编译通过。

出现×,说明文件编译出错,双击×,可以查看错误。

8.终于可以仿真了选择simulate→start simulate。

选择刚刚新建的库里面的top,或者测试文件名称,左下角的enable optimization一定要去掉勾,有勾的画不会出来波形,一定要去掉勾!一定要去掉勾!一定要去掉勾!(本人也不清楚原因,都是初学者,嘻嘻)跳出界面,右键测试文件,选择如下图接下来,选择仿真,run→run all点击缩小键,如图,就可以看到波形啦到此结束!初学者,如有错误,欢迎指出。

10_软件篇_Modelsim软件的使用_联合仿真

后仿真也称为时序仿真或者布局布线后仿真,是指电路已经 映射到特定的工艺环境以后,综合考虑电路的路径延迟与门延迟 的影响,验证电路能否在一定时序条件下满足设计构想的过程, 能较好地反映芯片的实际工作情况。

目录

2 Modelsim联合仿真(自动仿真)

目录

3 Modelsim手动仿真

《手把手教你学FPGA》

《手把手教你学FPGA》

M1 Modelsim简介 2 Modelsim联合仿真(自动仿真) 3 Modelsim手动仿真

目录

1

Modelsim简介

Modelsim简介

ModelSim是Mentor Graphics公司的仿真软件,该软件可 以用来实现对设计的硬件描述语言VHDL、Verilog HDL 或是两 种语言混合的程序进行仿真。

Modelsim无论是从使用界面和调试环境,还是从仿真速度 和效果上看,都可以算的上是业界比较优秀的HDL语言仿真软 件。它还提供了最友好的调试环境,具有个性化的图形界面和 用户接口,为用户加快调试提供强有力的手段,它是 FPGA/ASIC设计的首选仿真软件。

Modelsim简介

前仿真

前仿真也称为功能仿真,主旨在于验证电路的功能是否符合 设计要求,其特点是不考虑电路门延迟与线延迟,主要是验证电 路与理想情况是否一致。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

华桑电子科技有限公司华桑电子科技有限公司华桑电子科技有限公司Modelsim SE 仿真速度快需要编译库支持Verilog/vhdl混仿支持代码覆盖率测试Modelsim PE需要编译库不支持Verilog/vhdl混仿不支持代码覆盖率测试仿真速度慢Modelsim XE 针对Xilinx器件不需要编译Xilinx库Modelsim Altera 针对Altera器件不需要编译Altera库华桑电子科技有限公司华桑电子科技有限公司功能仿真验证语言设计的电路结构和功能是否和设计意图相符(设计电路时不可依赖仿真查错)综合后仿真验证综合后的电路结构是否与设计意图相符、是否存在歧义综合结果(综合后网表文件尚未包含布线延时)布局布线后仿真验证是否存在时序违规(布局布线后网表文件包含全部延时)华桑电子科技有限公司华桑电子科技有限公司modelsim.ini Compxlib.exe modelsim.ini取消只读属性编译库设置只读属性编译Xilinx库步骤:华桑电子科技有限公司批处理编译Xilinx库参考:attrib ‐R D:\modelsim\modeltech_6.6d \modelsim.ini1modelsim_lib.bat234pause D:\xilinx\13.2\ISE_DS\ISE\bin\nt64\compxlib.exe ‐s mti_se ‐arch all ‐lib all ‐l all ‐dir D:\modelsim\modeltech_6.6d\xilinx_libs_13.2 ‐w ‐p D:\modelsim\modeltech_6.6d\win32attrib +R D:\modelsim\modeltech_6.6d \modelsim.ini华桑电子科技有限公司Compxlib常用参数说明:‐s 仿真器类型(mti_se /mti_pe…vcs_mxi )Device (spartan3/spartan6…/all )Language (verilog/vhdl/all )仿真库(unisim/simprim /xilinxcorelib /all )Compxlib‐arch ‐lib ‐l华桑电子科技有限公司华桑电子科技有限公司Modelsim仿真步骤:建立work库映射库到物理目录编译源代码启动仿真器执行仿真1111113245华桑电子科技有限公司华桑电子科技有限公司仿真环境结构:RTL 设计OUTPUT INPUT输出校验激励生成TB_TOPDevicecmd.txt cmd.txt cmd.txt cmd.txt cmd.txt log.txtSIM 华桑电子科技有限公司仿真环境文件夹结构:tb_ptndowave_do sim_modelswork SIMwavelog cov Input File Output File华桑电子科技有限公司仿真环境搭建步骤:编写编译、添加波形、运行等do文件根据仿真说明书编写测试pattern编写仿真激励和输出校验文件编写仿真说明书华桑电子科技有限公司1编写仿真说明书华桑电子科技有限公司设计仿真架构编写测试操作说明书按功能模块细分测试pattern123华桑电子科技有限公司2编写仿真激励和输出校验文件华桑电子科技有限公司输入输出端口定义信号定义输出信号初始化时钟复位生成激励生成TASK编写输出校验TASK编写Log 信息写入Command文件读取Command 分析编写Log 文件打开Log 信息写入123华桑电子科技有限公司Command文件读取1、宏定义文件路径parameter p_TB_NAME= "tb_xxxx_xx" ;parameter p_CMD_IDIR= "tb_pattern/" ;2、定义寄存器矩阵(二位数组)reg[1:80] cmd[1:500];3、读取文件$readmemh({p_CMD_IDIR,p_TB_NAME,"/cmd.txt"},cmd) ;华桑电子科技有限公司时间精度与延时单位设置时间精度:格式:`timescale 单位时间/时间精度例子:`timescale 1ns / 1ps (单位时间为1ns,可精确到0.001)# 40.001;表示延时40.001ns延时单位:格式:#times [ns/us/ms/min]示例:#2ns; 延时2ns#40 ; 延时40个单位时间华桑电子科技有限公司时钟生成`timescale 1ps / 1psinitial beginr_CLK_100M = 0 ;# 10000 ;while (simend== 1'b0) begin# 5000 r_CLK_100M = ~ r_CLK_100M ;endend华桑电子科技有限公司Log文件写入1、宏定义文件路径parameter p_TB_NAME= "tb_xxxx_xx" ;parameter p_LOG_ODIR= "tb_pattern/ " ;2、信号定义integer LOG ;3、打开文件,文件写入,文件关闭LOG = $fopen( { p_LOG_ODIR, p_TB_NAME, "/log.txt" }, "w") ;4、写入文件$fdisplay(LOG,"Simulation Successful End ") ;5、关闭文件$fclose(LOG) ;华桑电子科技有限公司2编写测试pattern华桑电子科技有限公司Command定义Command文件编写编写测试pattern华桑电子科技有限公司Command定义实例华桑电子科技有限公司Command文件编写实例华桑电子科技有限公司2编写编译、添加波形、运行等do文件华桑电子科技有限公司vlib Modelsim常用命令vlib‐建立一个新的工作库参数:库名:工作库的名称(缺省值为work)实例:vlib work 在工作目录下建立一个work工作库华桑电子科技有限公司vmap Modelsim常用命令vmap‐工作库的映射参数:库名:工作库的名称路径:工作库的路径实例:vmap work work映射work库work目录下华桑电子科技有限公司vlog Modelsim常用命令vlog‐编译verilog源代码常用参数:‐work<libname>:指定编译的工作库‐cover<mode> :添加仿真覆盖率测试实例:vlog‐cover sbce‐work work*.v华桑电子科技有限公司vcom Modelsim常用命令vcom‐编译vhdl源代码常用参数:‐work<libname>:指定编译的工作库‐cover<mode> :添加仿真覆盖率测试实例:vcom‐cover sbce‐work work*.vhd华桑电子科技有限公司vsim Modelsim常用命令vsim‐启动仿真器常用参数:‐c:让vism工作在命令行模式‐t:指定仿真的时间分辨率(缺省为ns)‐l:输出log文件‐L :指定工作逻辑库‐wav :添加波形文件‐do:开始仿真后运行tcl脚本‐novopt:仿真优化选项work.*:指定仿真的top module实例:vsim‐t 1ps ‐c ‐l tb.log ‐L work ‐wav tb.wlf work.tb_top华桑电子科技有限公司run Modelsim常用命令run ‐运行仿真常用参数:<数量><单位>:指定运行时间(如5ns)@<数量>:运行仿真到<数量>个单位时间‐all:指定一直运行仿真‐continue:继续已停止的仿真实例:run‐allrun1msrun@1000华桑电子科技有限公司force Modelsim常用命令force ‐强制赋值语法:force <item_name> <value> <time>, <value> <time>‐value▶被强制的项的值‐time▶指定值的时间单位▶相对当前仿真时间,用@ character指定绝对时间▶时间单位能被指定,缺省值是仿真分辨率实例:force r_XRST0 @10ps ,1 @100ns , 0 @10ms华桑电子科技有限公司add wave Modelsim常用命令add wave ‐添加信号到波形文件参数:‐format : 显示格式(analog‐step,logic, literal )‐color: 波形的颜色(”red”,#257f77 )‐divider: 添加一个分割线,通常按功能模块分割‐radix: 数值显示形式(binary, ascii, decimal, octal, hex)‐group: 信号分组显示实例:add wave ‐noupdate‐format Logic ‐radix hexadecimal /tb_top/*华桑电子科技有限公司do文件种类compile_rtl.do compile_sim.do compile_lib.do tb_xx.do wave_xx.do 编译RTL 文件编译仿真文件编译其他库文件起动仿真器并运行仿真添加波形华桑电子科技有限公司华桑电子科技有限公司测试仿真覆盖率步骤:报告仿真覆盖率整合ucdb 文件,生成dat文件运行仿真,测试所有仿真pattern ,生成ucdb文件编译RTL文件时加上测试仿真覆盖率参数华桑电子科技有限公司编译RTL加仿真覆盖率参数实例vlog+cover=sbce‐work work BPI_IF.V华桑电子科技有限公司起动仿真器加仿真覆盖率参数实例vsim‐novopt‐coverage ‐t 1ps ‐c work.tb_top‐L work work.glbl‐wav ./wave/tb_01.wlf华桑电子科技有限公司仿真覆盖率文件整合报告实例vcover merge cov/merge_all.dat cov/*.ucdbvcover report ‐html ./cov/merge_all.dat ‐htmldir./cov/html_rpt华桑电子科技有限公司华桑电子科技有限公司待续……。