modelsim仿真详细过程.doc

实验五 Modelsim仿真 教案

实验五ﻩModelSim仿真【实验内容】1。

仔细阅读ModelSim软件简要使用说明(下文)。

(“实例代码”压缩包用于ModelSim 软件学习用)2。

Testbench写法简要介绍。

(可以参考“Testbench模版”)3.用ModelSim完成10位全加器的功能仿真。

ModelSim软件简要使用说明ModelSim是对VHDL,Verilog,SystemC以及混合语言编写的设计文件进行仿真和调试的工具软件。

1.仿真流程在ModelSim中对一个设计进行仿真的基本步骤如下图所示:2.仿真具体步骤Create a new project选择“File > New > Project”,会弹出对话框,如图所示:其中:“Project Name”项:填写要创建的工程的名字。

“Project Location”项:确定创建的工程所要存放的位置。

请在E盘下建文件夹!“Default Library Name"项:填写工程的工作库的名字。

注:在用ModelSim进行仿真之前,必须要对设计文件进行编译,生成与设计文件逻辑功能相对应的设计单元。

由于ModelSim是用库文件来进行仿真的,所以编译后的设计单元需要存放在库文件里。

这个库文件叫作“工作库”.926以上三项填写完毕后,点击“OK”按钮,会在指定的位置处创建工程及工作库,如图所示:在工作库文件夹内,有一个名为“_info"的特殊格式文件,如图所示:这个文件指定了此文件夹为ModelSim的工作库文件夹.在编译步骤内生成的所有设计单元都会被添加到工作库文件夹内。

Adding objects to the project在上一步点击OK后,ModelSim会弹出一个对话框,如图所示:其中:“Create New File”项:在工程中创建新的设计文件。

“Add Existing File”项:把已经存在的设计文件加入到工程中。

modelsim+ISE后仿真流程

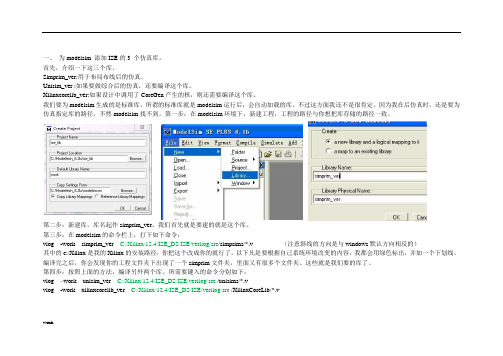

一、为modelsim 添加ISE的3 个仿真库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。

所谓的标准库就是modelsim运行后,会自动加载的库。

不过这方面我还不是很肯定。

因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。

我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:vlog -work simprim_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src/simprims/*.v (注意斜线的方向是与windows默认方向相反的)其中的c:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。

以下凡是要根据自己系统环境改变的内容,我都会用绿色标出,并加一个下划线。

编译完之后,你会发现你的工程文件夹下出现了一个simprim文件夹,里面又有很多个文件夹。

这些就是我们要的库了。

第四步:按照上面的方法,编译另外两个库。

所需要键入的命令分别如下:vlog –work unisim_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src /unisims/*.vvlog -work xilinxcorelib_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src /XilinxCoreLib/*.v第五步:把库建好后,接下来的事情就是使它成为modelsim的标准库。

这只要修改modelsim安装目录下的modelsim.ini文件就可以了。

modelsim实验01_计数器仿真实验步骤

一、新建工程 a) 如图,打开modelsim后点击FileNewProject...

b) 弹出如下图对话框,输入Project Name后,点击OK c) 弹出如下对话框,点击Close 二、在建好的工程中添加Verilog程序文件并进行编译 a) 新建好的空工程如下图,在空白处右击,选择Add to ProjectNew File...

b) 弹出如下对话框,将type选项改为Verilog,然后输入名称,点击OK c) 双击新建好的文件,在右侧的编辑框里输入程序

d) 输入完成后,点击左上角工具栏的保存按钮 e) 同样的步骤建立一个测试文件,然后在空白处右击选择CompileCompile All,进行编译 f) 编译成功后,会出现如下变化,否则请检查程序重新编译 三、进行仿真 a) 编译成功后,点击下方Library选项,在展开的work文件夹中右击刚才建立的测试文件,选择Simulate b) 此时弹出如下sim选项界面,在任意处右击选择Add toWaveAll items in region c) 添加波形完成后,会弹出右侧如下波形框,将上方工具栏中的时间长度100ps改为1ms,然后点击傍边的run工具按钮 d) 点击运行之后,出现如下波形图,通过调节工具栏上的放大、缩小、适应屏幕的按

钮,以及拖动下方的进度条,就会出现合适的波形视图,如下 PS: 鼠标右击波形框中的测试文件名,选择RadixUnsigned,可以将二进制改为十进制,如

下图,可以看到,计数器随着时钟频率的上升沿,开始计数 四、附录Verilog计数器实验源程序

module counter3b(clk,cnt); //counter3b.v input clk; output reg[2:0]cnt=3'b0; always @(posedge clk) begin cnt<=cnt+1; end endmodule

交大最新ModelSim仿真教程

1. ModelSim概览ModelSim仿真软件是由Midel技术公司开发的工业界上最为通用的仿真器之一,它可以用于Verilog仿真,VHDL仿真或者两者的混合仿真。

ModelSim仿真软件产品的类型很多,我们在这里要介绍的是ModelSim/S,它是ModleSim的首要版本,功能最为强大,包含了ModelSIm/PLUS的所有功能及其附加功能。

ModelSim/SE随着时间的推移不断地推出新的版本,我们要介绍的是Mentor Graphis公司于2005年6月推出的ModelSim/Se 6.1版本的使用。

图1.1 ModelSim/Se 6.1用户界面在UNIX操作系统的命令行中首先输入fpga.setup命令,然后输入vsim命令,便可以得到图1.1所示的ModelSim图形用户界面。

为了完成后续的实验内容,请先将ModelSimLAB 文件夹(内部包含lab1、lab2、lab3、lab4四个文件夹)复制到自己的根目录下面。

2. 基本的仿真步骤ModleSim 有三种实现方法。

第一种是交互式的命令行,这种操作方法没有用户界面,唯一的界面是控制台的命令行。

第二种是用户界面(UI),它能够接收菜单输入和命令行输入。

第三种是批处理模式,是用DOS 或UNIX 命令行运行批处理文件。

我们在这里主要讨论第二种——用户界面的方式。

2.1建立ModelSim 库(物理库)这里要插入怎么创作的命令,进到哪个目录,运行什么命令?从主菜单里面:File->New->Library 点击Library 得到Create a New Library 对话框。

选择a new library and a logical mapping to it ,在Library Name 中输入work ,相应的在Library Physical Name 中也会出现物理名work 。

然后点击OK 确定。

此时在工作空间workspace 的Library 内会出现一个名为work 的库。

modelsim使用教程

modelsim使用教程ModelSim是一款常用的硬件描述语言(HDL)仿真工具,本教程将向您介绍如何使用ModelSim进行仿真。

步骤1:安装ModelSim首先,您需要下载和安装ModelSim软件。

在您的电脑上找到安装程序并按照提示进行安装。

步骤2:创建工程打开ModelSim软件,点击"File"菜单中的"New",然后选择"Project"。

在弹出的对话框中,选择工程的存储位置,并为工程命名。

点击"OK"完成工程创建。

步骤3:添加设计文件在ModelSim的工程窗口中,右键点击"Design"文件夹,选择"Add Existing File"。

然后选择包含您的设计文件的目录,并将其添加到工程中。

步骤4:配置仿真设置在工程窗口中,右键点击"Design"文件夹,选择"Properties"。

在弹出的对话框中,选择"Simulation"选项卡。

在"Top level entity"字段中,选择您的设计的顶层模块。

点击"Apply"和"OK"保存设置。

步骤5:运行仿真在ModelSim的工具栏中,找到"Simulate"按钮,点击并选择"Start Simulation"。

这将打开仿真窗口。

在仿真窗口中,您可以使用不同的命令来控制和观察设计的行为。

步骤6:查看仿真结果您可以在仿真窗口中查看信号波形、调试设计并分析仿真结果。

在仿真窗口的菜单栏中,您可以找到一些常用的查看和分析工具,如波形浏览器、信号分析器等。

步骤7:结束仿真当您完成仿真时,可以选择在仿真窗口的菜单栏中找到"Simulate"按钮,并选择"End Simulation"以结束仿真。

用ModelSim仿真带测试文件的流程

执行以下步骤的环境是,计算机上安装了ModelSim。

其中由于ModelSim软件不支持中文,空格的安装路径,所以其他各软件的安装路径也不能包含中文与空格,否则会导致ModelSim 软件不能正常运行。

下面以二与门为例进行说明。

一.首先使用某种文本编辑器,编写程序and_2.v与验证测试程序and2_test.v。

module and_2(A,B,F);// and_2.vinput A,B;output F;and U(F,A,B);endmodule`timescale 10ns/1ns //The unit of simulation and precision is 1ns. and2_test.v//'timescalemodule and_2_test; //ce shi di ceng mo kuaireg A,B; //shu ru ding yi wei ji cun qi xingwire F; //shu chu ding yi wei xian wang xingand_2 and_2(A,B,F); //diao yong di ceng mo kuaiinitialbeginA=0;B=0;#100 A=1;#100 A=0;B=1;#100 A=1;#200 $finish;endendmodule二.如果对已经存在的具有测试程序的ModelSim工程进行仿真,则双击工程文件,转第七步。

如果是第一次运行,则在ModelSim主窗口中,单击File-〉New-〉Project…进行新建工程的工作。

三.在出现的Creat Project对话框中输入工程名、工程路径以及缺省库名(一般这库名work 不用改)。

四.在出现的Add items to the Project对话框中,单击Add Existing File,在出现的Add file to Project对话框中点击Browse…找到刚才的and_2.v与验证测试程序and2_test.v。

Modelsim仿真流程-经验总结

Modelsim仿真流程-经验总结1.Modelsim简介略。

2.modelsim仿真流程:modelsim基本的仿真流程包括建立库、建立工程并编译、仿真、调试、但在libero环境中运行modelsim时,软件自动映射库和生成工程文件。

其中功能仿真、综合仿真以及后仿真分别映射presynth、postsynth和postlayout库。

基本流程是:建立工作库→编译源代码→启动仿真→分析、调试。

2.1建立库并映射在modelsim中,任何使用VHDL、Verilog HDL、SystemC等语言实现的设计,都被编译到一个库中。

♥方法一:File>New>Library选择新建并映射到该库;♥方法二:在modelsim>提示符下运行命令vlib work2-建立库,vmap work work2-建立映射库;2.2建立工程Modelsim仿真需要建立自己的工程,同时modelsim还提供了文件夹管理工程的功能。

♥step1:File>New>project,并指定库文件名;♥step2:新建文件或导入文件;2.3编译文件建立好工程后,使用compile功能对源文件进行编译。

Libero环境启动modelsim时,系统执行run.do脚本文件自动编译源文件。

♥鼠标右击文件,选择compile All对所有的工程文件执行编译操作;♥启动仿真,使用simulation>start simulation>选择design选项卡功能使modelsim进入仿真状态,之后可以运行仿真。

在libero环境下,运行modelsim直接从运行仿真这一步骤开始。

♥运行仿真可以设置仿真时间或选择仿真全部♥tcl命令:do run.do –当设计修改后,使用此命令重新导入设计;Do wave.do-打开波形列表文件,或者向当前波形添加列表;Restart-复位当前仿真,从0时刻重新仿真;Run 1ms-运行仿真1ms时间;Run all-运行全部的仿真;在libero环境下,可以自己编写脚本文件代替run.do文件,在项目比较大的情况下可以大大简化仿真的操作。

使用ModelSim的仿真步骤

使用ModelSim的仿真步骤:

1.建立工程:选file/new/project菜单,打开Create Project窗口.

填Project Name栏,为你的工程启一个名子.

按Browse按纽,为你的工程指定一个盘上目录,作为以后工程文件的存放位置.

指定缺省库名为Work库.

2.在出现的ADD ITEMS TO THE PROJECT窗口中选Create New File为当前工程加入一个新建文件,或选Add existing File为当前工程加入一个已存在的文件.

3.选Compile/compile All对当前设计工程进行编译.

4.选Simulate/Star Simulation菜单项,打开仿真器.

5.在仿真器中选Design页,点击WORK页前的加号,打开WORK 库,选一个仿真文件,选好后,点击右下脚的OK按纽.

6.在出现的Object窗口中,会有芯片的引脚列表.选一个引脚,压鼠标右键,弹出一菜单,在其中选Add to wave/Selected Signal菜单项,可将引脚对象加入到Wave窗口中.重复上述过程,将全部引脚加入到Wave波形窗口中.

7.在WAVE中,选一个引脚,用WAVE窗口的工具画加在引脚上的波形.

8.画完输入引脚的波形后,输入RUN –ALL,回车,执行仿真.

注:上述仿真过程,可用命令:

vsim work.filename

启动仿真窗口.

view wave

打开波形窗口

add wave –dec *

加入所有波形信号,以十进制方式force

为每个引脚加入驱动信号

run –all

执行仿真任务。

modelsim仿真详解 -回复

modelsim仿真详解-回复什么是ModelSim仿真?ModelSim是一种著名的仿真工具,用于数字和模拟电路的功能仿真和时序仿真。

它是由美国Mentor Graphics公司开发的,提供了一整套的仿真、调试和验证功能,广泛应用于电子设计自动化领域。

ModelSim仿真工具可以模拟数字电路的行为和时序,在仿真过程中可以观察和分析电路的运行状态,以验证设计的正确性。

它支持Verilog和VHDL两种高级硬件描述语言,并且提供了强大的波形编辑和调试功能,便于用户分析和调试设计中的问题。

ModelSim仿真的基本原理和流程是什么?ModelSim仿真的基本原理是利用编译过程将Verilog或VHDL代码转化为可执行的仿真模型,然后通过激励文件对模型进行驱动和刺激,最后观察波形输出并进行分析。

下面是ModelSim仿真的基本流程:1. 编写设计代码:使用Verilog或VHDL语言编写设计代码,包括设计模块、信号连接、时钟和复位逻辑等。

2. 创建测试平台:编写测试平台代码,包括生成激励信号和检查输出结果的内容。

3. 编译设计代码:使用ModelSim提供的编译器将设计代码编译成仿真模型,产生可执行的仿真对象文件。

4. 创建仿真模型:使用ModelSim提供的工具和命令,创建仿真模型并加载仿真对象文件。

5. 配置仿真环境:设置仿真时钟、仿真时间、仿真启动方式等仿真环境参数,准备仿真的相关设置。

6. 运行仿真:启动仿真过程,模拟电路的行为和时序,并根据测试平台的激励信号来驱动设计,产生波形输出。

7. 观察波形:利用ModelSim提供的波形窗口,观察和分析仿真波形结果,验证设计的正确性。

8. 调试和分析:根据波形结果来调试和分析电路中的问题,定位和解决设计中的错误,优化电路的性能。

ModelSim仿真工具的优势是什么?ModelSim仿真工具在电子设计自动化领域具有很高的知名度和广泛的应用,其主要优势如下:1. 支持多种设计语言:ModelSim支持Verilog和VHDL两种常用的硬件描述语言,用户可以根据自己的需求选择合适的语言进行设计和仿真。

modelsim实验计数器仿真实验步骤

modelsim实验-计数器仿真实验步骤————————————————————————————————作者:————————————————————————————————日期:一、新建工程a)如图,打开modelsim后点击File→New→Project...b)弹出如下图对话框,输入Project Name后,点击OKc)弹出如下对话框,点击Close二、在建好的工程中添加Verilog程序文件并进行编译a)新建好的空工程如下图,在空白处右击,选择Add to Project New File...b)弹出如下对话框,将type选项改为Verilog,然后输入名称,点击OKc)双击新建好的文件,在右侧的编辑框里输入程序d)输入完成后,点击左上角工具栏的保存按钮e)同样的步骤建立一个测试文件,然后在空白处右击选择Compile Compile All,进行编译f)编译成功后,会出现如下变化,否则请检查程序重新编译三、进行仿真a)编译成功后,点击下方Library选项,在展开的work文件夹中右击刚才建立的测试文件,选择Simulateb)此时弹出如下sim选项界面,在任意处右击选择Add to→Wave→All items in regionc)添加波形完成后,会弹出右侧如下波形框,将上方工具栏中的时间长度100ps改为1ms,然后点击傍边的run工具按钮d)点击运行之后,出现如下波形图,通过调节工具栏上的放大、缩小、适应屏幕的按钮,以及拖动下方的进度条,就会出现合适的波形视图,如下PS: 鼠标右击波形框中的测试文件名,选择Radix Unsigned,可以将二进制改为十进制,如下图,可以看到,计数器随着时钟频率的上升沿,开始计数四、附录Verilog计数器实验源程序module counter3b(clk,cnt); //counter3b.v input clk;output reg[2:0]cnt=3'b0;always @(posedge clk) begincnt<=cnt+1;endendmodule`timescale 1 ns/10 ps // counter3b_tb module counter3b_tb();reg clk=0;wire [2:0]cnt;always #100 clk=~clk;counter3b i1(.clk(clk),.cnt(cnt)); endmodule。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

由于我们只需要了解仿真的完整过程,所以不需要自己写源文件和测试文件(也称为testbench)。

一下就是简单的源文件和测试文件(亲自测试过)。

//源文件

module compare(equal,a,b); input a,b; output equal;

assign equal=(a==b)?1:0; endmodule

//测试文件

`timescale 1ns/1ns `include./compare.v module comparetest; reg a,b; wire equal; initial begin a=0; b=0; #100 a=0;b=1; #100 a=1;b=1;

#100 a=1;b=0; #100 $stop; end

compare compare1(.equal(equal),.a(a),.b(b)); endmodule

有了源文件和测试文件下面就开始用modelsim进行仿真了。

步骤一:新建工程和.v文件(也就是源文件和测试文件)

打开modelsim软件,点击file,选择new—>project 然后就会弹出下面窗口:

然后在project name那一栏写上工程名(随便去,一般是字母),在project location选择工程路径(路径最好没有中文,听说的),然后点OK。

进入下个界面:

然后点击小框里面的“create new file”.弹出界面:

在file name中写下源文件名,由于这是比较两数的大小,我取为:compare。

在“add file as type”中选择verilog,点OK,然

后有:

双击compare.v文件会弹出编译窗口:

复制上面源文件代码,粘贴到上图右边窗口里面。

然后点击保存图标,然后再新建测试文件。

点击下图的新建文件图标。

过程如同上。

你会看见下图的两个.v文件。

步骤二:编译文件

在添加文件在已建的工程后,两个文件的status都是问号,编译后就变成勾。

具体步骤为:

点击compile all图标就可以了。

步骤三:仿真,添加波形

选中compare.v文件,点击仿真图标如下图:

接着会弹出界面:

选中comparetest,点击OK,有:

选中compare1 右击鼠标,选择add,继续选择To Wave.,我用的是10.0a版本,还要选择all items in region.然后就有界面:

点击run图标就会出现仿真波形。