基于FPGA的硬件滤波器设计及仿真

基于FPGA的IIR数字滤波器的设计与实现

关 键 词 : 阶 节 ,R 数 字 滤波 器 ,P 二 I I F GA

Ab ta t s rc

Ths ap nr du s eho sig as a i p erito ce a m t d ofu n c c ded s o der oc s ec nd or bl k whch i ba e on PGA o m pl s F t i emen h pr c— tte i i n

张书召 ( 桐柏 鑫 泓银 制 品有限 责任公 司 , 南 西峡 4 4 5 ) 河 7 7 0

彭 杰 ( 广东工业大学 自动化学院, 广东 广州 5 0 9 ) 10 0

摘 要

介 绍一 种 使 用 二 阶 节级 联 方 法在 F GA 上 实现 任 意 阶 数 的 I ( 限 脉 冲 响 应 ) 数 字 滤 波 器 的 原 理 和 方 法 。 首 先 在 P I 无 R

pe a d meh d o n r e u e I ( f i mp le rs o s ) dgtlf e i th i ri a c r a c t e ur— i n to fa y od rn mb rf R i it i us e p n e nn e ii i r r , e ft n c od n e wi rq i a l Fst t l e h e

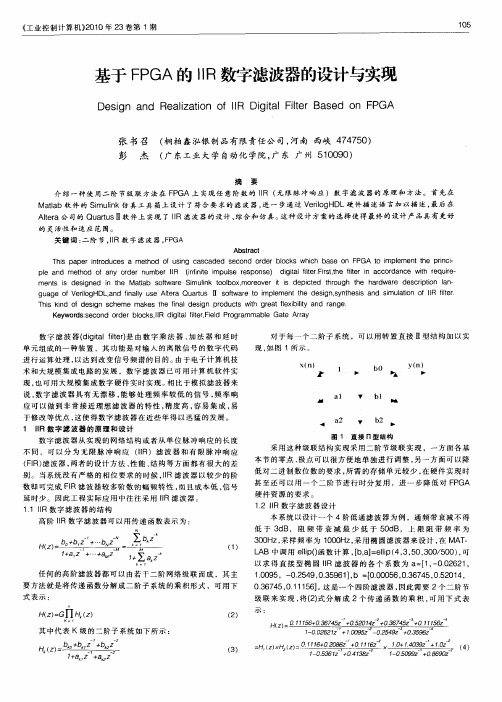

1 I I R数 字 滤 波器 的 原 理 和 设计

_

al

丫

bl

. a I 2

丫

b 2

数 字滤 波 器 从 实 现 的 网络 结 构 或 者 从 单位 脉 冲响 应 的 长 度

图 1 直 接 n型 结 构

不 同 ,可 以 分 为 无 限 脉 冲响 应 (R)滤 波 器 和 有 限 脉 冲 响 应 I I

基于FPGA的图像处理硬件设计与实现

基于FPGA的图像处理硬件设计与实现概述:图像处理是数字信号处理领域的重要应用领域之一,它在计算机视觉、医学影像、图像识别等方面有着广泛的应用。

FPGA(Field Programmable Gate Array)作为一种可编程逻辑器件,具有并行计算能力和高速数据处理能力,特别适合用于图像处理的硬件设计与实现。

本文将介绍基于FPGA的图像处理硬件设计的基本流程和关键技术,以及实现一个基于FPGA的图像滤波系统的案例。

第一部分:图像处理硬件设计的基本流程1. 系统需求分析:在进行图像处理硬件设计之前,首先需要明确系统的需求和目标。

包括图像处理的功能要求、延迟要求、资源利用率要求等。

2. 硬件平台选择:选择适合图像处理的FPGA开发板或芯片。

根据系统需求,考虑各种性能指标,如时钟频率、资源量、功耗等。

3. 硬件架构设计:设计图像处理系统的硬件架构,包括模块划分、数据通路设计、控制器设计等。

4. 算法实现:根据图像处理的算法和功能需求,将算法转化为硬件设计的形式。

对于复杂的算法,可以采用高层次综合工具进行优化。

5. RTL设计与验证:使用硬件描述语言如VHDL或Verilog来进行RTL (Register Transfer Level)级别的设计和验证。

通过仿真验证电路设计的正确性和功能实现。

6. 综合与布局布线:对RTL设计进行综合优化,将其映射到目标FPGA平台的可用资源上,再进行布局布线。

7. 系统集成与调试:将各个模块进行集成并进行整体调试,确保系统的稳定性和性能。

第二部分:基于FPGA的图像滤波系统设计与实现案例在本部分,我们以图像滤波为例,展示一个基于FPGA的图像处理系统的设计与实现。

1. 系统需求分析:我们的目标是实现一个基于FPGA的图像平滑滤波器。

我们需要处理彩色图像,具体要求为:支持不同尺寸的图像输入,实现高质量的平滑滤波效果,并且具备实时处理的能力。

2. 硬件平台选择:我们选择了一款高性能的FPGA开发板,该板上搭载了一颗高性能的FPGA芯片,具有丰富的资源和高时钟频率。

基于FPGA的IIR滤波器研究及仿真实现

现 有 的 D P处 理 器难 以 同时 满 足 这 两 方 面 的要 求 。随 着 可 编 程 逻 辑 器 件 和 E A 技 术 的 发 展 , P S D F GA

( i dP o rmma l G t Ara ) 性 能 、 本 、 活 性 和 功 耗 等 方 面 的 优 势 突 显 出来 , 于 F GA 的信 Fe — rga l be ae ry 在 成 灵 基 P 号 处 理 器 已 广 泛应 用 于各 种 信 号 处 理 领 域 。数 字 滤 波 器 是 现 代 数 字 信 号 处 理 系 统 的 重 要 组 成 部 分 之

1 lt 字 滤 波 器 的基 本 理 论 I数 F

1 1 数 字 滤 波 器 的 定 义 和 分 类 .

数字 滤波是 提 取有 用 信 息 非 常重 要 、 活 灵 的方 法 , 现代 信 号处 理 的重 要 内容 。在 数 字 是 通信 、 音 图像处理 、 分析 、 式识别 、 语 谱 模 自动控

s op fle BSF)z 。 t it r, E?

地运 用在大 规模集 成 电路 设计 中。它既解 决 了 定制 电路 的不 足 , 又克 服 了原 有 可编 程 器件 门 电路 数有 限的缺 点 。F G 技 术设计 I 滤波 P A I R

12 数 字 滤 波 器 的 优 越 性 .

够方便 快 捷 的 实 现 滤 波 器 设 计 、 真 和 实 现 。 仿

而其 相对 低 廉 的价 格 、 巧 的体积 和 高效 的运 小

变输 入信号所 含频 率成分 的相 对 比例 或者滤 除

某 些频 率成分 的器件 _ 。 1 ]

行速率 , 助 于 降 低 成 本 , 有 降低 系 统 体 积 与重 量, 提高效 率 和性能 。所 以运用 F GA 技 术设 P

基于FPGA的数字滤波器的设计与实现

基于FPGA的数字滤波器的设计与实现数字滤波器是一种非常重要的数字信号处理技术,用于消除输入信号中的噪声,并提高信号品质和可靠性。

FPGA(Field Programmable Gate Array)是一种用于构建数字电路的可编程逻辑器件,因其高度的可定制性、可重构性和高性能而被广泛应用于数字信号处理中。

本文将介绍基于FPGA的数字滤波器的设计和实现,包括滤波器原理、数字滤波器设计方法、FPGA实现技术以及实验结果分析等内容。

一、数字滤波器原理数字滤波器是滤波器的一种,其实现基于数字信号处理技术。

数字滤波器的输入信号是离散时间信号,输出信号也是离散时间信号。

数字滤波器通过在离散时间域上对输入信号进行滤波,实现对输入信号中某些频率成分的滤除或保留。

数字滤波器通常分为FIR(有限脉冲响应)滤波器和IIR(无限脉冲响应)滤波器两类。

FIR滤波器是一种线性相位滤波器,其系统函数是一个有限长度的冲激响应权重系数序列。

FIR滤波器通过对输入信号的每个样本与权重系数的乘积进行累加,输出得到滤波后的信号。

FIR滤波器具有零相位失真、线性相应特性、易于设计、易于实现等优点。

IIR滤波器是一种具有无限脉冲响应的滤波器,其系统函数是一个有理多项式。

与FIR滤波器相比,IIR滤波器具有更高的滤波效率、更低的计算复杂度和更好的逼近性,但也存在稳定性差、相位失真大等问题。

二、数字滤波器设计方法数字滤波器的设计方法主要包括滤波器性能要求的确定、滤波器类型的选择、滤波器设计的数学模型的建立、滤波器参数的计算、滤波器实现等几个方面。

在确定滤波器性能要求方面,需要考虑滤波器的通频带、阻带、通带和阻带带宽、滤波器响应曲线、阶数等方面的参数。

在滤波器类型的选择方面,需要根据滤波器的性能要求、实现难易度、计算复杂度和开销等方面的因素进行综合考虑。

在滤波器设计的数学模型的建立方面,需要根据选定的滤波器类型建立其对应的数学模型。

在滤波器参数的计算方面,需要根据滤波器的数学模型进行参数的计算和优化。

基于FPGA的FIR滤波器设计

基于FPGA 的FIR 滤波器设计一 、设计目的为了帮助学生深入理解和消化基本理论、进一步提高综合应用能力并且锻炼独立解决问题的能力,我们将《数字信号处理》、《集成电路原理与应用》和《《FPGA 系统设计与应用》几门课程融合在一起开设的FPGA 综合实验课程设计。

本次完成的是利用FPGA 来完成FIR 滤波器的设计、程序设计和实验调试任务。

二、设计要求(1)基本要求利用所学知识,采用VHDL 语言完成FIR 滤波器的设计仿真。

要求用VHDL 编程设计底层文件,顶层文件可任意(可用原理图方式或文本方式);完成仿真文件(包括MATLAB 和QUARTUSII 两种仿真)并对其结果比较。

具体设计指标如下: (1)采样频率S F =80KHz ;(2)截止频率KHz F C 10=;(3)输入序列为10位(最高位为符号位); (4)窗口类型为kaiser 窗,β=0.5 ; (5)滤波器长度为16 ; (6)输出结果保留10位。

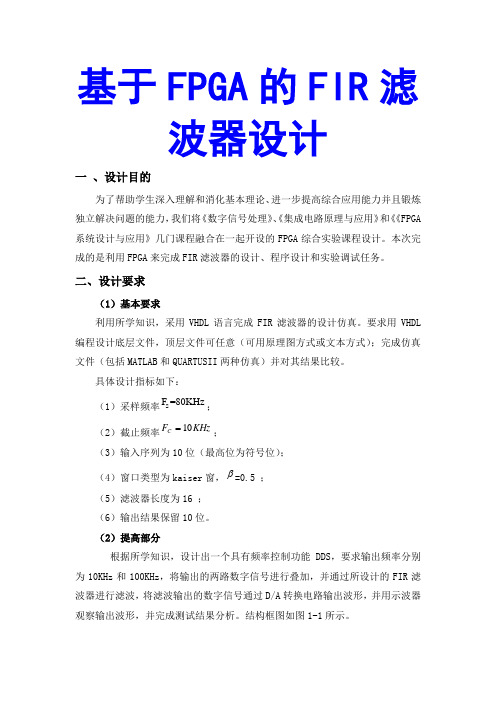

(2)提高部分根据所学知识,设计出一个具有频率控制功能DDS ,要求输出频率分别为10KHz 和100KHz ,将输出的两路数字信号进行叠加,并通过所设计的FIR 滤波器进行滤波,将滤波输出的数字信号通过D/A 转换电路输出波形,并用示波器观察输出波形,并完成测试结果分析。

结构框图如图1-1所示。

图2-1 整体结构框图三、设计原理3.1 FIR 滤波器由线性系统理论可知,在某种适度条件下,输入到线性系统的一个冲击完全可以表征系统。

当我们处理有限的离散数据时,线形系统的响应(包括对冲击的响应)也是有限的。

若线性系统仅是一个空间滤波器,则通过简单地观察它对冲击的响应,我们就可以完全确定该滤波器。

通过这种方式确定的滤波器称为有限冲击响应(FIR)滤波器。

3.2 线性FIR 滤波器原理FIR 滤波器响应(简称FIR )系统的单位脉冲响应()h n 为有限长序列,系统函数()H z 在有限z 平面上不存在极点,其运算结构中不存在反馈支路,即没有环路。

基于FPGA的FIR滤波器设计与仿真

数字滤波器; 分布 式 算 法 ;P A FG 中图分 类 号 T 3 1 P 1 文 献标 志 码 A

滤波器需 要执行 无 限数量 卷 积 , 能得 到较 好 的 幅度特性 , 相位 特性 其 是非线性 的 ; I 波器 由有 限个 采样 值 组 成 , 构 成 的系 统总 是稳 FR滤 其 定 的 , 易于实现 线性相 位 …. 且 由于 在语音 信 号处 理 、 图像 处理 、 数字 通信等传 输过程 中不能有 明显 的相位失真 , FR滤波器在 满足一定 而 I 对称条件 下可 以实现 I I R滤波器 难 以实 现 的线 性相 位 , 因而得 到广泛

特 别适合如 FR、丌 等数 字信号处 理任务 . I F 利用 F G P A可 以重 复配置 高精 度的 FR滤波器 , 用 V D I 使 H L硬件 描述语 言改变滤 波器 的系数和

阶数 , 能实 现大 量 的卷 积运 算算 法 J 结合 M xls 具软 件 的辅 并 . apu 工

案速 度 快 、 时性 好 、 省 硬 件 资 源 , 实 节 具 有重 要 的 工程 应 用价 值 . 关 键 词

实 现数字化 是 控 制 系统 的重 要发 展 方 向 , 而数 字 信 号处 理 已在

通信 、 语音 、 图像 、 自动控 制 、 达 、 事 、 空 航 天等 领 域 广 泛应 用 . 雷 军 航 数 字信号 处 理 方 法 通 常 涉 及 变 换 、 波 、 谱 分 析 、 码 解 码 等 处 滤 频 编 理¨. 数字滤 波是数 字信号处 理重 要 环节 , 它能 满 足滤 波器 对幅度 和 相 位特性 的严格 要 求 , 克服 模 拟 滤 波器 所 无 法解 决 的 电压 和 温度 漂 移 以及噪声 等 问题 , 而有 限冲激 响应 FR滤 波器在设计 任意 幅频 特性 I 的同时能够保证 严格 的线性相 位特性 . 数 字滤波器 根 据其 冲激 响应 函数 的 时域 特性 , 分 为无 限 长 冲 可

基于FPGA的FIR数字滤波器设计与仿真

a in ls p rto , so ai n o h p n . I l r i w d l s d b c u e o t t c h s itrin a d s a p c t o s s a e a ain r t r t rs a ig F R f t s i ey u e e a s fi s i tp a e d s t o n h r u — f g e o i e s r o

c a a trsi. h a i h o yo i i lf tra d t e meh d o a iai n a e r s a c e . h e i n o e rq i d d gt l h r c e i cT eb sc t e r fd gt le n h t o f e l t r e e r h dT e d sg ft e u r ii t a i r z o h e a i e sgv n u ig t e smu ae s f r fMAT AB.n h i l t r s l i ie . f tri ie sn h i lt o t a e o l w L a d t e smua e e u t sgv n Ke r sf t r d gt l c nr ls se / cl y i sal t n r v e d sr u e l oi m ; n o f n t n y wo d :i e ; ii ; o to y t msf i t n tl i e iw; it b t d ag rt l a a i ao i h wi d w c i u o

y∑c]2 + b2f = 【l ∑X ] n一 [ n

n = 0 L = 0 J

( 3 )

分 布 式 算 法 是 一 种 以 实 现 乘 加 运 算 为 目的 的运 算 方 法 。 它 与传 统 算 法 实 现 乘 加 运 算 的 不 同 在 于执 行 部 分 积 运 算 的先 后顺序。 该算 法 利 用一 个 查 找 表 (U ) 现 映射 , 用 一 个 2 L T实 即 字 宽 、 先 编 好 程 序 的 L T接 收 一个 Ⅳ 位 输 入 向 量 X= 】 预 U I 【 , x0 %[ , , [- l 映 射 , 查 找 表 的 查 找后 直接 输 出 部 分 积 。 1 … x N l】 】  ̄ 的 经 与传 统 算 法 相 比 , 布式 算 法 可 极 大 的 减 少 硬 件 电路 的规 模 , 分

基于 FPGA 的数字滤波器设计与实现

基于 FPGA 的数字滤波器设计与实现引言:数字滤波器是现代信号处理的重要组成部分。

在实际应用中,为了满足不同信号处理的需求,数字滤波器的设计与实现显得尤为重要。

本文将围绕基于 FPGA的数字滤波器的设计与实现展开讨论,介绍其工作原理、设计方法以及优势。

同时,还将介绍一些实际应用场景和案例,以展示基于 FPGA 的数字滤波器在实际应用中的性能和效果。

一、数字滤波器的基本原理数字滤波器是一种将输入信号进行滤波处理,改变其频谱特性的系统。

可以对频率、幅度和相位进行处理,实现信号的滤波、去噪、增强等功能。

数字滤波器可以分为无限脉冲响应滤波器(IIR)和有限脉冲响应滤波器(FIR)两种类型。

IIR滤波器是通过递归方式实现的滤波器,其输出信号与过去的输入信号和输出信号相关。

FIR滤波器则是通过纯前馈结构实现的,其输出信号仅与过去的输入信号相关。

两种类型的滤波器在性能、复杂度和实现方式上存在一定差异,根据具体的应用需求选择适合的滤波器类型。

二、基于 FPGA 的数字滤波器的设计与实现FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,通过可编程逻辑单元(PLU)、可编程连线(Interconnect)和可编程I/O(Input/Output)实现。

其可编程性使得 FPGA 成为数字滤波器设计与实现的理想平台。

1. FPGA的优势FPGA具有以下几个优势,使得其成为数字滤波器设计与实现的首选平台:灵活性:FPGA可以根据设计需求进行自定义配置,可以通过修改硬件逻辑来满足不同应用场景的需求。

可重构性:FPGA可以重复使用,方便进行修改和优化,减少芯片设计过程中的成本和风险。

高性能:FPGA具有并行处理的能力,可以实现多通道、高速率的实时数据处理,满足对于实时性要求较高的应用场景。

低功耗:FPGA可以进行功耗优化,通过减少冗余逻辑和智能布局布线来降低功耗。

2. 数字滤波器的实现方法基于 FPGA 的数字滤波器的实现方法主要有两种:直接法和间接法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、 f

} l |

Fo ur / c r q e  ̄ KH

/ ,

图 1

一

质量监督・ 消费指导 57

广 质 监 导 西 量 督 报

在 FG PA中使 用将 1 位 定点 数据 。 因此在 使 用 Gnrt 6 eeae HL D 工具生成 FG 设计所 需要 的 Vr g PA el 文件 之前,我们还要将 o

三、Smui i lk中的仿真 n

为 了进一步验证仿真我们设计 的滤 波器 ,在 Sm l k iu n 环境 i

下,将我们设计的滤波器作为模块导出,并输入信号为 S() t

=i (002 t sn (00 t ,设 计如 图 2 示的仿 s 10 )+i 300 2 ) n 所

图5

陈 然 ’胡代弟 (. 1 郑州铁路职业技术学院。河南 郑州 4 0 5 ; 5 0 2

2 郑州大学西亚斯学院 。河南 郑 州 4 05 ) 。 502

一

、

引言

FA ol(i e ei DTo Fl rDs n& Aa s o1 t g nl i To)是 H TA 信 号 ys实现 。首先 ,我们使 用 M TA 生成 A LB A LB 输入波形数据 ,为 了便于 比较 ,我们取 与 Sm l k iui 中相同的仿 n 真数据。在 M TA 中建立 SN I. 文件 ,内容如下 : ALB I_NM

xO 9 = :9 ;

广西质量监督导报

基于 F G P A的硬件滤波器设计及仿真

[ 要]本文通过对~个四阶 I 摘 I R椭圆滤波器的设计 ,介绍利用 MTA 及 A LB

QATI软件 实现基 于 Atr 公司的 FG U R I l a e PA器件 的滤波器设计及仿 真的方法。

[ 关键词] FG ;I 滤波器;M TA PA I R A LB

m=X;

执 行仿 真 后 ,分 别 将 滤 波 器 的输 入 和 输 出 数据 显 示 在 Soe 和 Soe ,波形分别为图 3和图 4所示 。 cpl cp 上

通常会使用到 MTA 软件作为设计和仿真的工具。 A LB

本 文使 用 MTA 制 一 个 四 阶 I ALB定 I 圆 滤 波 器 ,通 过 R椭

FA ol DT o 工具生成适于 FG PA的硬件描述语言 ,并 将其导入

QATI中进 行设计仿 真。 UR I

二、I I R数字滤波器的设计

信号处理过程中,对信号的过滤、检测、预测等,都要使 用滤波器,数字滤波器是数字信号处理中使用最广泛的一种器

件。FG 具有使 用灵活、可并行工作 、运算速 度高等优 点 ,越 PA 来越多地运用到数字信号处理中。 传统的数 字滤波器 的设计使 用公 式繁琐 ,参 数改变后 需要 重新计算 ,从而在设计滤波器时工作量很大。现代滤 波器设 计 ,

F1 rai mtc 置为 F e—on;Fl ritra j e r hei 设 t t i d pi x t i e nenl 的 t s中

Ru dn o e o n ig m d 设置为 F o :O ef w m d l r v rl oe设置 为 St r e o o a ua 。 t

处理工具箱专用的滤波器设计分析工具,操作简单、灵活,可 以采用多种方法设计 FR I 滤波器。在 H TA 命令窗口输 I和 I R ALB 入 FA ol DTo 后回车就会弹出FAol DTo 界面。

首先 在 Fl rTp i e ye中选 择 l a ( 通 滤 波 器 ) t o ps 低 w s :在 Ds nMto 选项 中选 择 I :接 着在相邻 的右则选 项 中选 择 ei ehd g I R El t ( 圆 型 ); 指 定 Fl r Od r项 中 的 Sei l pi 椭 i c i e re t pcf y Odr 4 然 后 在 Feuny Sei ctos中 选 择 Ui re= : rqec pc iain f nt为 Kz 给 出 采 样 频 率 F= O , 通 带 Fa = 0 最 后 在 H, s lO ps 2 i s Mgiue pc iain 中 选 择 Ui 为 d , Aas l antd Sei ctos f nt b ps , = Atp 2。设 置 完成 后点 击 Dsg i e s =0 o einFl r即可得 到所 设 计 的 t I 滤波器。 I R

I 数字滤波器与 FR I R I 数字滤 波器相比 ,它可 以用较低 的阶

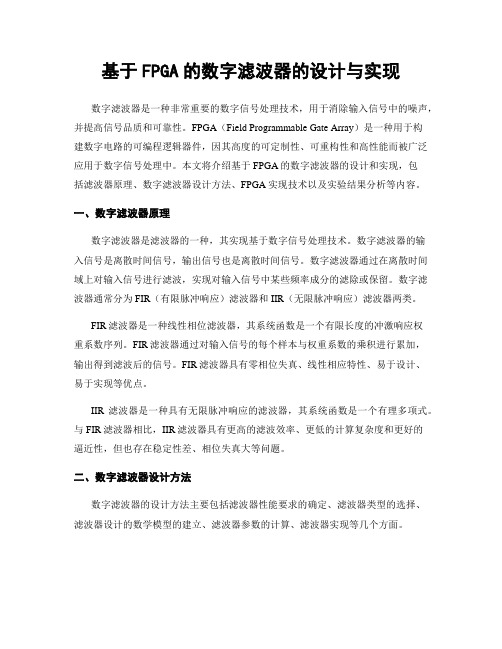

设计完后的幅频响应如图 1所示。

数获得高选择性 ,所用逻辑资源少、效率高 ,在相同门级规模

和 相同时钟速 度下可以提供 更好的特性。本文的设计为 4阶 I I R 椭 圆滤波器 ,采样频率为 1 0 H , 止频率为 2 H ,阻带衰 O z 截 K 0 z K 减 为 2 B 0 的低通 滤波 器。 d 本 文使用到 MTA 信号处理工具箱 中的滤波器设计 和分析 ALB

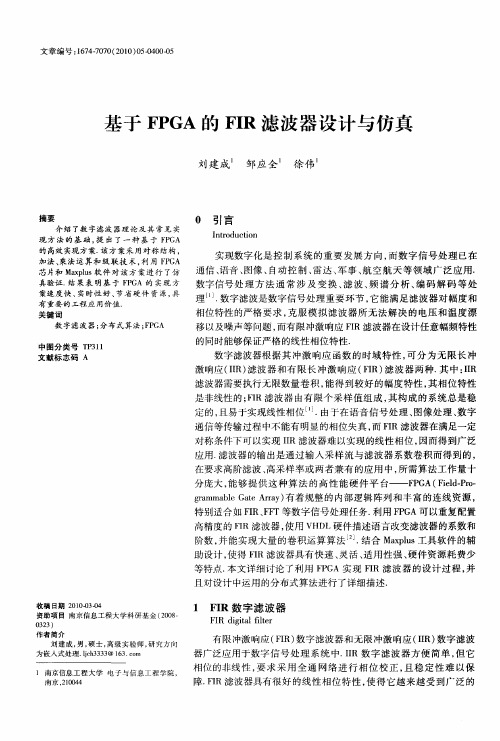

四、Q A T中模块生成及仿真 UR

打开 QAT I,新建一个 工程 ,导入 FAol UR I DTo 生成 的 Vr g文件 ,并在顶层图中生成相应的模块。为便于仿真 ,设 el o

计如图 5 所示 的顶层设计图。

设置 完成后 ,使 用 G nr eHL eea O 工具生成 FG 设 计所需要 的 t PA Vr g el 文件 ,并且保存为 fl r a。 o i e. d t f

图中,Im rm 模块是一个 RM p —o O O 模块,仿真开始之前将输 入的波形数据保存在 RN中。仿真时 ,在时钟的作用下,由 O ad d 模块将 RM中的数据顺序送到滤波器模块 Fl r O i e 中,滤波 t 输出的数据传送到fl rot i e u 引脚。 t

由于 FG 仿真数 据也不能直观地反映 波形 ,因此我们在仿 PA