基于FPGA芯片的最小系统设计

EDA技术简介

实体说明

图5-3 mux21a实体 实体

ARCHITECTURE one OF mux21a IS BEGIN y <= a WHEN s = '0' ELSE b ; END ARCHITECTURE one ;

EDA技术 EDA技术

2、主流器件 、

◆ FPGA 现场可编程门阵列) (Field Programmable Gate Array现场可编程门阵列) 现场可编程门阵列 ◆ CPLD 复杂可编程逻辑器件) (Complex Programmable Logic Device复杂可编程逻辑器件) 复杂可编程逻辑器件

功能仿真

逻辑综合器

FPGA/CPLD

适配

结构综合器

时序与功能 门级仿真

1、功能仿真 、 2、时序仿真 、

FPGA/CPLD 编程下载

EDA技术 EDA技术

二、 FPGA最小系统 最小系统

EDA技术 EDA技术 1、EP1K100B+ 零售价:450元(含EPC2芯片 零售价: 元 芯片) 、 芯片

EDA技术 EDA技术

技术? 一、EDA技术? 技术

EDA( Automation电子设计自动化 电子设计自动化) ● EDA(Electronic Design Automation电子设计自动化) 是指利用计算机完成电子系统的设计。 是指利用计算机完成电子系统的设计。

EDA技术是以计算机和微电子技术为先导, 技术是以计算机和微电子技术为先导 ● EDA技术是以计算机和微电子技术为先导, 汇集了计算机图 形学、 拓扑、 逻辑学、 形学、 拓扑、 逻辑学、 微电子工艺与结构学和计算数学 等多种计算机应用学科最新成果的先进技术。 等多种计算机应用学科最新成果的先进技术。 EDA技术以计算机为工具, 技术以计算机为工具 ● EDA技术以计算机为工具, 代替人完成数字系统的逻辑综 合、布局布线和设计仿真等工作。 布局布线和设计仿真等工作。 等工作

基于EPF10K10LC84-3的FPGA最小系统

《电子设计自动化(EDA)技术》课程实训报告题目: 基于EPF10K10LC84-3的FPGA最小系统姓名:院系:专业:学号:指导教师:完成时间: 年月日目录1 课程设计题目、内容与要求……………………………………4页1.1 设计内容…………………………………………………4页1.2 具体要求…………………………………………………4页2 系统设计…………………………………………………………5页2.1系统原理…………………………………………………5页2.2 设计思路…………………………………………………6页3 系统实现……………………………………………………… 6页3.1电源电路和复位电路模块………………………………6页3.2 外部时钟模块……………………………………………6页3.3 下载电路模块……………………………………………7页4 硬件验证操作说明………………………………………………7页4.1 PCB工程项目的环境创建…………………………………7页4.2原理图的编写和ERC检查…………………………………8页4.3元件的封装检查……………………………………………9页4.4 PCB图中元件的布局和布线………………………………9页5总结………………………………………………………………12页6 参考书目…………………………………………………………12页基于EPF10K10LC84-3的FPGA最小系统摘要:提出一种新的FPGA最小系统开发板的设计思想,开发板以ALTERA公司的的ACEX1K 系列的EPF10K10LC84-3为主芯片,整体采用模块的设计,文章对最小系统的原理框图、信号的运行流程进行了详细地阐述,并给出了实际的制作过程图例。

此FPGA实用价值不错,并且FPGA与以微处理器为核心的数字系统相比,具有可靠性高,可实时升级、体积小巧、结构简单、运行速度快的优点。

关键词:FPGA 设计最小系统1 课程设计题目、内容与要求1.1 设计题目基于EPF10K10LC84-3的FPGA最小系统1.2 设计内容芯片电源和复位电路时钟脉冲电路接口电路1.3 具体要求1.电源电路将产生一个3.3V和1.5V的输出电路,复位电路利用高低电平的原理设计;2.显示电路由7段数码管进行显示;3.下载电路连接芯片与电脑之间的数据传输;4.外部时钟电路将产生标准1Hz的秒脉冲信号2 系统设计2.1 设计原理基于EPF10K10LC84-3的FPGA最小系统2.2设计思路1.电源电路将产生一个3.3V和1.5V的输出电路,复位电路利用高低电平的原理设计;2.显示电路由7段数码管进行显示;3.下载电路连接芯片与电脑之间的数据传输;4.外部时钟电路将产生标准1Hz的秒脉冲信号3 系统实现3.1电源电路和复位电路模块电源电路VREF一般是3.3V,假定VCC出入为5V,则此电路可输出一个3.3V和1.5V 的电压。

基于RISC-V的计算机系统综合实验设计

计算机工程与设计COMPUTER ENGINEERING AND DESIGNApr.2021Vol.42 No.42021年4月第42卷第4期基于RISC-V 的计算机系统综合实验设计孙卫真1!刘雪松朱威浦2 !向 勇3 +(1首都师范大学 信息工程学院,北京100048; 2.中国科学院计算技术研究所,北京101407;3.清华大学 计算机科学与技术系,北京100084)摘要:针对目前高校计算机系统各课程实验衔接不紧密、实验成本较高的问题!提出设计基于小型FPGA 开发板、以 RISC-V CPU 和Rut 操作系统内核为核心的计算机系统综合实验平台。

硬件实验以在低成本FPGA 芯片上搭建picorv32 RISC-V CPU 为核心!软件实验以在硬件实验基础上移植Rut 编写的rCore 教学操作系统为核心。

以较低成本在同一平台 完成计算机组成原理与操作系统实验设计!使其形成一个有机的整体,在资源与成本有限的情况下构建一个较为完整的实验体系。

实例结果表明!实验平台以软硬件协作的方式,适应技术的发展!及时更新实验内容!可满足高校计算机系统教学综合实验的基本要求。

关键词:RISC-V &系统编程语言;组成原理实验&操作系统实验&软硬件协作中图法分类号:TP301 文献标识号:A 文章编号:1000-7024 (2021 041159-07doi : 10. 16208/j. issnl 000-7024. 2021. 04. 037De?ign for comprehen?ive laboratory of computer?y?tem ba?ed onRISC-VSUN Wei-zhen 1, LIU Xue-song 1, ZHU Wei-pu 2, XIANG Yong 3+(1. I n f o r m a t i o n E n g i n e r i n g C o l e g e , C a p i t a l N o r m a l U n i v e r s i t y # B e i j n g 10048, C h i n a ;2. I n s t i u t e o f C o m p u t i n g T e c h n o l o g y , C h i n e s e A c a d e m y o f S c i e n c e s , B e i j n g 101407 , C h i n a ;3. Department of Computer Science and Technology , Tsinghua University , Beijing 100084 , China)Abstract: A i m i n g a t r y i n g t o i m p r o v e t h e e x p e r i m e n t a l c o n e c t i o n a m o n g t h e c o m p u t e r s y s t e m c o u r s e s i n t h e u n i v e r s i t e s a n d r e - d u c e t h e x p e r i m e n t c o s t #a c o m p r e h e n s i v e c o m p u t e r s y s t e m e x p e r i m e n t a l p l a t f o r m b a s e d o n a s m a lF PG Ab o a r d a n d a t e a c h i n g o p e r a t i o n s y s t e m w a s p r o p o s e d . T h e h a r d w a r e e x p e r i m e n t w a s b u i l d i n g a s y s t e m o n c h i p (S o C ) w i t h p i c o r v 32 R I S C -V C P U o n a l o w -c o s t F P G A c h i p . T h e s o f t w a r e e x p e r i m e n t w a s t r a n s p l a n t i n g t h e r C o r e t e a c h i n g o p e r a t i o n s y s t e m w r i t e n b y R u s t o n t h e i r o w n S o C . T h e c o m p u t e r c o m p o s i t o n p r i n c i p l e a n d o p e r a t i o n s y s t e m e x p e r i m e n t a l d e s i g n o n t h e s a m e p l a t f o r m a t a l o w e r c o s t wa s F o m p l e t e d #a n d a n o r g a n i F w h o l e w a s f o r m e d . T h e e x p e r i m e n t a l s y s t e m w a s a r e l a t i v e F o m p l e t e p l a t f o r m w i t h l i m i t e d F o s t s . E x a m p l e s h o w t h a t #t h e x p e r i m e n t a l F o n t e n t s a r e t i m e l y u p d a t e d f o r t r a F i n g F o m p u t e r t e F h n o l o g y t r e n d s i n a s o f t w a r e -h a r d - w a r e c o p e r a t i v e m a n e r t o m e t h e b a s i c r e q u i r e m e n t s o f c o m p u t e r s y s t e m t e a c h i n g e x p e r i m e n t s i n u n i v e r s i t e s .Keywords :RI S C -V ; s y s t e m p r o g r a m mi n g l a n g u a g e ; c o m p o s i t o n p r i n c i p l e e x p e r i m e n t ; o p e r a t i n g s y s t e m e x p e r i m e n t ; s o f t w a r e h a r d w a r e c o p e r a t i v e4引言目前,高校进行计算机系统教学实验主要有以下几种教学方式:其一是使用纯硬件搭建实验平台,虽该方式可深入接触计算机硬件模块,但实验操作机械死板、硬件平台开发成本较高;其二是采用软件系统仿真的方式,该方法成本较低、易于上手,但受教育者不能在实验过程中较好体会到计算机与硬件的紧密结合!为了优化上述问题,实现设计目标,本文从硬件支持、 处理器构建、系统编程语言选择三方面考虑,构建计算机 系统实验平台。

FPGA开发平台硬件系统设计及实现

研发设计 I RESEARCH DESIGN樓块图1系统总体设计框图近几年,随着FPGA (可编程逻辑器件)规模的日益增大, 我国数字电路设计取得了迅猛发展,硬件设计环境不断向实 用化、可靠化方向发展,为功能电路设计工作的有序开展提 供了硬件支持。

为此,如何科学设计和实现FPGA 开发平台 硬件系统、不断完善相关功能电路是相关软件开发人员必须思考和解决的问题。

1.系统总体设计FPGA 开发平台硬件系统主要由网 络模块、PS 2接口模 块和U S B 模块等模 块组成,系统总体 设计框图如图1所 示。

为了保证该系 统的运行性能,相关软件开发人员要重视对这些模块的设计与实现,为用户带 来良好的体验感。

1.1网络(D M 900A )模块电路设计网络(DM 900A )作为一种先进的接口芯片,充分利用 了以太网的应用优势,具有以下几种特征:①能够实现物理 层接口的全面集成;②内部含有FIFO 缓存,主要用于对大 量字节的接收和发送:③能够很好地兼容和支持不同类型的 主机工作模式;④在HP 证背景下,能够很好地实现自动翻 转功能和直接互联功能;⑤能够充分利用tcp /tp 加速器的应 用优势,避免CPU 承担过高的存储负担,从而实现对整机 运行性能的全面提高:⑥极大地缩短了读写时间。

总之,在 以太网控制器的应用背景下,相关软件开发人员要严格遵循 相关网络传输标准和要求,从而实现网速的提高和网络环境 的优化。

同时,在对网络模块电路进行科学设计的过程中, 确保该电路能够实现对相关接口的集成和应用,并采用接口 输入的方式将各种接口与芯片进行深度融合,以促进FPGA 开发平台硬件系统向智能化、自动化、信息化方向不断发展。

1.2USB 模块电路设计对于U S B 模块电路而言,为了保证其设计水平,相关软件开发人员要重 视对 CY 7C 68013A 芯片的使用,将 传输速度设置为摘要:随着社会经济水平的不断提高和信息时代的不断发展,FPGA (可编程逻辑器件)在集成电路领域中取得了良好的应用 效果,不仅有效扩大了编程器件电路的数量,还避免了定制电路的局限性,为更好地改进多种逻辑应用功能和结构发挥了 重要作用。

FPGA最小系统分析与电路设计

FPGA最⼩系统分析与电路设计《FPGA最⼩系统分析与电路设计》部分节选⾃《FPGA应⽤开发⼊门与典型.pdf 》FPGA最⼩系统包括:FPGA芯⽚、下载电路、外部时钟、复位电路和电源。

如果使⽤NIOS II软嵌⼊式处理器还要包括SDRAM和Flash。

(1)配置管脚MSEL[1..0]:⽤于选择配置模式,FPGA有多种配置模式,如主动、被动、快速、正常、串⾏、并⾏等,以此管脚进⾏选择;DATA0:FPGA串⾏数据输⼊,连接置配置芯⽚的串⾏数据输出管脚;DCLK:FPGA串⾏时钟输出,为配置器件提供串⾏时钟;nCSO(I/O):FPGA⽚选信号输出,连接⾄配置器件的nCS管脚;ASDO(I/O):FPGA串⾏数据输出,连接⾄配置器件的ASDI管脚;nCEO:下载链器件使能输出,在⼀条下载链种,当⼀个器件配置完成后,此信号使能下⼀个器件开始进⾏配置。

下载链的最后⼀个器件的nCEO应悬空。

nCE:下载链器件使能输⼊,连接⾄上⼀个器件的nCEO,下载链的第⼀个器件的nCE接地。

nCONFIG:⽤户配置模式起始信号;nSTATUS:配置状态信号;CONF_DONE:配置结束信号。

(2)电源引脚VCCINT:内核电压,与⼯艺有关,例如130nm⼯艺为1.5V,90nm⼯艺为1.2V;VCCIO:端⼝电压,⼀般为3.3V,也可以选择为5V、1.8V、1.5V;VREF:参考电压;GND:信号地。

(4)时钟管脚VCC_PLL:锁相环管脚电压,直接连VCCIO。

VCCA_PLL:锁相环模拟电压,⼀般通过滤波器连到VCCINT上。

GNDA_PLL:锁相环模拟地。

GNDD_PLL:锁相环数字地。

CLKnum(LVDSCLKnump):锁相环时钟输⼊,⽀持LVDS时钟输⼊,p接正端,num表⽰PLL序号。

CLKnum(LVDSCLKnumn):锁相环时钟输⼊,⽀持LVDS时钟输⼊,n接负端,num表⽰PLL序号。

PLLnum_OUTp(I/O):锁相环时钟输出,⽀持LVDS时钟输⼊,p接正端,num表⽰PLL序号。

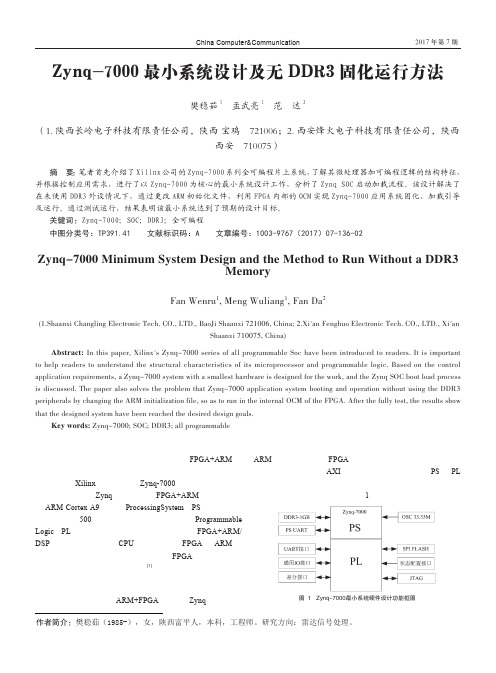

Zynq-7000最小系统设计及无DDR3固化运行方法

图1 Zynq-7000最小系统硬件设计功能框图樊稳茹(1985-),女,陕西富平人,本科,工程师。

研究方向:雷达信号处理。

2017年第7期信息与电脑China Computer&Communication软件开发与应用该最小系统PS部分结合用户应用程序用于实现控制功能,PL部分包括UART接口、时序产生、地址译码、片上存储和外设控制等逻辑功能模块。

主要的功能芯片为X7Z045、MT41K256M16HA、MAX3160E、MAX3096、MAX3045、W25Q128、ADG3308等,为了降低硬件成本,在满足使用需求的条件下,该最小系统设计时取消了图1中虚线框中的DDR3存储器。

2 基本启动配置流程分析Zynq是一个可扩展处理平台,简单地说就是有个FPGA 做外设的A9双核处理器,所以它的启动流程与FPGA完全不同,而与ARM处理器类似。

Zynq支持JTAG、NAND、Parallel NOR、QSPI以及SD卡等启动方式。

Zynq有效利用了片上的CPU来帮助配置,在没有外部JTAG的情况下,处理器系统(PS)与可编程逻辑(PL)都必须依靠PS来完成芯片的初始化配置,内部的启动存储区(BootROM)和芯片配置单元可实现Zynq从BootROM主动启动或者从JTAG被动启动[2]。

与其他XILINX 7系列的器件不同的是,Zynq并不支持从PL端直接进行启动配置,Zynq的启动配置是分多级进行的,配置过程最少需要两步,但通常是按如下三个阶段进行。

阶段0(Stage0):简称BootROM,控制着整个芯片的初始化过程。

该部分代码是不可修改的,处理器核在上电或者热启动时自动执行这部分代码,并对外部的NAND、NOR、SD等外设控制器进行初始化,同时还负责将阶段1的启动镜像(FSBL镜像)加载到OCM(Zynq片上一个256K的RAM,但在FSBL运行前只能使用其中的192K,所以FSBL要小于192K),然后运行FSBL,FSBL镜像来源由板上MIO[5:3]引脚选择的启动方式决定。

基于FPGA的设计 正文

引言随着经济和科学技术的发展,电梯在高层建筑物的作用越来越凸出。

目前电梯主要分为机械系统与控制系统两大部份,而电梯的控制系统主要有三种控制方式分别是:继电路控制系统(“早期安装的电梯多位继电器控制系统)、基于FPGA控制系统、微机控制系统。

实现继电路控制系统方法很多,可以用标准逻辑器件、可编程序控制器PLC、单片机等方案来实现。

但是这些方法的功能修改及调试都需要硬件电路的支持,在一定程度上增加了功能修改及系统调试的困难,且该系统由于故障率高、可靠性差、控制方式不灵活以及消耗功率大等缺点,已渐渐被人民淘汰。

微机控制系统虽在智能控制方面有较强的功能,但也存在抗扰性差,系统设计复杂,一般维修人员难以掌握其维修技术等缺陷,没能广泛应用电梯中。

而基于FPGA的电梯控制系统由于可靠性高,使用维修方便,抗干扰性强,设计和调试周期较短等优点,在电梯控制中得到广泛应用,从而使电梯由传统的继电器控制方式发展为计算机控制的一个重要方向,成为当前电梯控制和技术改造的热点之一。

本文给出一个基于FPGA的6层自动升降电梯控制系统的设计方案。

它的设计是采用通俗易懂的Verilog HDL硬件描述语言使用EDA技术在Quartus II软件平台上设计完成,程序设计、编译以及时序仿真通过后再下载到开发板配合外围电路(模拟电梯的电路)来验证该系统的可行性。

这个系统分主要有6个模块,分别是键盘响应寄存处理模块、上升/下降请求寄存处理模块、电梯运行和停止处理模块、开门/关门与延时处理模块、电梯运行方向判断模块和电梯运行状态显示模块。

通过模块化设计不仅提高了程序编程错误的排查能力还提高了系统的可靠性。

1 概论1.1 电梯国内外现状1.1.1国内现状电梯作为中国对外最早的行业经过多年的发展,电梯产品无论在数量和质量都有了显著的提高,和国外产品差距越来越小。

考虑到经济性,现有国内的电梯控制系统,通常采用微机或可编程逻辑控制器对变频器进行多段速控制。

FPGA现代数字系统设计

2.2 Verilog HDL 基本结构

语言本身提供了各种层次抽象的表述, 可以用详细程度有很大差别的的多层次模 块组合来描述一个电路系统。 行为级:技术指标和算法的Verilog描述 RTL级:逻辑功能的Verilog描述 门级 :逻辑结构的Verilog描述 开关级:具体的晶体管物理器件的描述

a b sl out

结构级

module muxtwo (out, a, b, sl); input a,b,sl; output out; a not u1(ns1,sl); and #1 u2(sela,a,nsl); and #1 u3 (selb,b,sl); b or #2 u4(out ,sela,selb); endmodule

低电平有效的信号经过锁存器锁存后,其命名应在_n后加r。如 CpuRamRd_n信号,经锁存后应命名为CpuRamRd_nr 多级锁存的信号,可多加r以标明。如CpuRamRd信号,经两级触 发器锁存后,应命名为CpuRamRd_rr。

3)

Verilog HDL测试模块: 用Verilog HDL描述的模块,

可以用来产生测试信号序列并可以接收被测试模块的信 号,用于验证所设计的模块是否能正常运行,往往不可 综合成具体门级电路。

4)Verilog HDL顶层(测试)模块:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.3本课题主要研究工作...............................................................1

4.6本章小结...........................................................................29

第五章测试结果与分析..................................................................30

2.3FPGA的结构特性...................................................................3

2.3.1FPGA的优点.................................................................4

2.3.2FPGA的缺点.................................................................5

2.4FPGA的分类........................................................................5

3.2.1FLEX10K系列概述...........................................................8

3.2.2FLEX10K系列器件性能.....................................................8

3.2.3FLEX10K系列器件电源设计................................................9

第一章引言................................................................................1

1.1FPGA的简述........................................................................1

2.5本章小结............................................................................7

第三章Altera可编程逻辑器件..........................................................8

4.3.1USB接口供电电路原理图设计............................................21

4.3.2JTAG模式配置电路原理图设计...........................................22

4.3.3最小系统接口电路原理图设计............................................23

3.3.3FLEX10K系列器件下载设计...............................................13

3.4本章小结...........................................................................14

5.1调试过程...........................................................................30

5.1.1八位LED显示调试.........................................................30

3.3QuartusII软件部分.............................................................10

3.3.1QuartusII软件功能说明................................................10

3.3.2QuartusII软件使用设置................................................11

5.1.2四位七段数码管显示调试.................................................31

5.1.3LCD显示调试...............................................................31

黑龙江大学本科生

毕业论文(设计)档案

编码:

学院:电子工程学院

专业:电子信息工程

年级:2007

学生姓名:王国凯

毕业论文题目:基于FPGA的电梯自动控制系统设计

指导教师:林连冬

装订日期:

备注栏

本文在介绍了在当前国内外信息技术高速发展的今天,电子系统数字化已成为有目

共睹的趋势。从传统的应用中小规模芯片构成电路系统到广泛地应用单片机,直至今天FPGA在系统设计中的应用,电子设计技术已迈人了一个全新的阶段。FPGA利用它的现场可编程特性,将原来的电路板级产品集成为芯片级产品,缩小体积,缩短系统研制周期,方便系统升级,具有容量大、逻辑功能强,提高系统的稳定性,而且兼有高速、高可靠性。越来越多的电子设计人员使用芯片进行电子系统的设计,通过基于FPGA电梯系统开发设计,说明了FAPG芯片研究的动机和研究意义。

Keyword

FPGA; Mini-System;FLEX10K;JTAG;Moduledesign

摘要.........................................................................................I

ABSTRACT..................................................................................II

4.5最小系统电路实物图..............................................................27

4.5.1最小系统总体电路实物图.................................................27

4.5.2下载线电路实物图.........................................................29

4.3.4D型并口下载线电路原理图设计..........................................23

4.3.5最小系统电路设计的总体电路原理图....................................24

4.4最小系统电路PCB板设计.........................................................25

1.4本章小结...............................................2

第二章FPGA基本知识.....................................................................3

2.1FPGA的诞生........................................................................3

2.2FPGA的发展与现状.................................................................3

关键词

FPGA;电梯系统;FLEX10K;JTAG;模块设计

Abstract

Thispaperintroducestherapiddevelopmentof informationtechnologyaroundthe worldtoday.Digitalizedelectronicsystemshavebecomethetrend.Fromthetraditional applicationofsmallandmedium-chipcircuitrytoMicrocontrollerandFPGAapplicationinsystemdesign,electronicdesigntechnology issteppingintoanewfield.Byusingitsfield programmablefeatures,FPGA changestheoriginalcircuitboard-levelproductstothe chip-levelintegrationproducts.NowFPGA hasadvantagesofreducedthesize,shorten developmentcycle,facilitatedinsystemupgrades,highlycapacity,stronglogicfunctions, stablesystemandhighspeed.MoreandmoreelectronicdesignersuseFPGA todesignelectronicsystems.ThispapershowsthemotivationandsignificanceofdesigningbyFPGA throughtheelevatorFPGAsystemdesign.

4.2.3开关电路原理图设计.......................................................17