运算放大器稳定性实验

模电实验报告五 运算放大器

模拟电子技术实验报告第(5 )次实验实验名称:_运算放大器专业班级:自动化姓名:学号:一、实验目的1、研究由集成运算放大器组成的比例、加法、减法和积分等基本运算电路的功能。

2、了解运算放大器在实际应用时应考虑的一些问题。

二、实验原理集成运算放大器是一种具有高电压放大倍数的直接耦合多级放大电路。

当外部接入不同的线性或非线性元器件组成输入和负反馈电路时,可以灵活地实现各种特定的函数关系。

在线性应用方面,可组成比例、加法、减法、积分、微分、对数等模拟运算电路。

理想运算放大器特性在大多数情况下,将运放视为理想运放,就是将运放的各项技术指标理想化,满足下列条件的运算放大器称为理想运放。

开环电压增益Aud=∞输入阻抗ri=∞输出阻抗ro=0带宽fBW=∞失调与漂移均为零等。

理想运放在线性应用时的两个重要特征:1、输出电压uo与输入电压之间满足关系式子uo=Aud(u+—u-)由于Aud=∞,而uo为有限值,因此,u+—u-≈0,。

即u+≈u-,称为“虚短”。

2、由于ri=∞,故流进运放两个输入端的电流可视为零,即IIB=0,称为“虚断”。

这说明运放对其前级吸取电流极小。

上述两个特性是分析理想运放应用电路的基本原则,可简化运放电路的计算。

基本运算电路(1)反相比例运算电路电路如图4-1所示。

对于理想运放,该电路的输出电压与输入电压之间的关系为为了减小输入级偏置电流引起的运算误差,在同相输入端应接入平衡电阻R2=R1//RF(2)反相加法电路电路如图4-2所示,输出电压与输入电压之间的关系为(3)同相比例运算电路图4-3(a)是同相比例运算电路,它的输出电压与输入电压之间的关系为(4)差动放大电路(减法器)对于图4-4所示的减法运算电路,当R1=R2,R3=RF时,有如下关系式(5)积分运算电路反相积分电路如图4-5所示。

在理想化条件下,输出电压uo等于式中uc(o) 是t=0 时刻电容C 两端的电压值,即初始值。

消除放大器输出震荡运放稳定研究

三、实验仪器

台式计算机,示波器,信号发生器, 直流稳压电源,万用表,面包板等。

四、实验内容及步骤

R2 10k

V2 15

4 V-

OP1 uA741

R1 10k

2

-

VF1

6

3 ++

7

Vin

V+

C1 1u R3 100k

+

VG1

V1 15

图1 运放接容性负载

四、实验内容及步骤

C2 220p R2 70k

实验二

运算放大器输出稳定性研究

一、实验目的

分析运算放大器输出不稳定的原因 利用TINA-TI研究如何提高运算放大器

输出稳定性的方法。

二、实验原理

在运算放大器的很多应用场合,要驱动 较大的容性负载,对于理想运放来说, 其输出阻抗为0,所以输出不会出现震 荡的现象,但是实际运放器存在输出阻 抗,该电阻与容性负载耦合,往往会在 运放的单位增益带宽内产生新的极点, 这将导致运放输出的不稳定。

按照图2,在面包板上连接电路,观察输出结 果,记录输出波形,及过冲幅度,稳定时间。 从而验证使运放输出稳定的方法。

五、思考题

减小图2中的R2,观察能使运放输出 稳定的R2最小值。

研究其他能够使运放输出稳定的方法。

R1 10k

Vin VG1

+

7

4 V-

V2 15

OP1 uA741

2

-

6

3 ++

V+

V1 15

C1 1u R3 100k

VF1

图2 提高闭环增益和加入Cf

四、实验内容及步骤

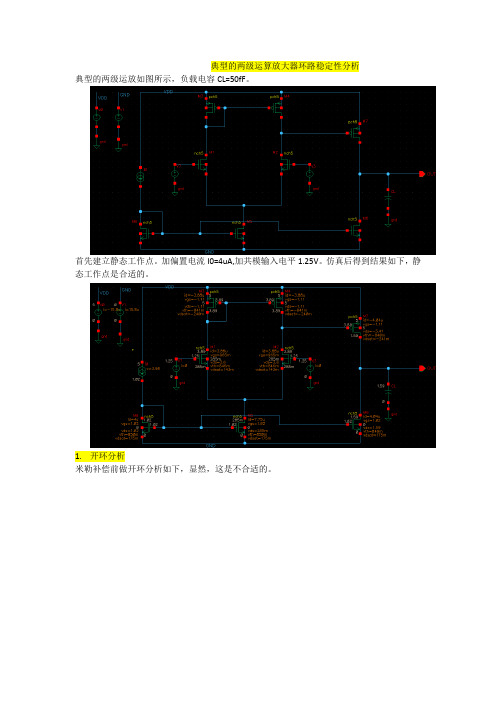

典型的两级运放环路稳定性分析

典型的两级运算放大器环路稳定性分析典型的两级运放如图所示,负载电容CL=50fF。

首先建立静态工作点。

加偏置电流I0=4uA,加共模输入电平1.25V。

仿真后得到结果如下,静态工作点是合适的。

1.开环分析米勒补偿前做开环分析如下,显然,这是不合适的。

加米勒补偿电容Cc=200fF,做开环分析如下,显然,这也是不合适的。

这是由于电路中存在零点造成的。

加入调零电阻Rz=40K,,仿真结果如下。

可以看出,,,相位裕度为40度,不够。

可通过加大补偿电容来进一步分裂p1,p2主次极点。

(已尝试过加米勒补偿电容Cc=300fF可以得到大于60度的相位裕度)。

但是本次设计的运放用在负反馈环路中,故只需要负反馈环路是稳定的就达到设计标准。

理论计算。

查看各管子的静态工作点。

,,,即。

,,,即。

,。

理论值与仿真结果非常接近。

,理论值与仿真结果非常接近。

,,理论值与仿真结果非常接近。

,,理论值与仿真结果40度偏差较大。

2.在负反馈环路中做环路稳定性分析:从上图可以看出,加入反馈电阻网络R1,R2后就打破了原有的静态工作点:主要是反馈电阻网络R1,R2中的电流由M7管提供,所以M7管的静态工作点打破了,即运放的第二级跨导GmⅡ,输出电阻R2都变了。

从波特图中可以看出相位裕度为77度,满足设计标准。

理论计算:查看各管子的静态工作点。

,,,即。

,,,即。

,。

理论值与仿真结果非常接近。

,理论值与仿真结果非常接近。

,理论值与仿真结果非常接近。

,,理论值与仿真结果77度偏差较大。

此结果可能是由于gm7变大,原来的调零电阻RZ过大造成的。

现在改变调零电阻Rz=25K,,仿真结果如下:此时,相位裕度为63度,满足设计标准。

3.改用大电感大电容仿真环路增益:仿真方法如上图所示,将环路断开,加入大电感L0=1GH通直流以建立直流工作点,并且断开交流通路,加入大电容C3=1GF通交流小信号V8。

从仿真结果图中可以看出相位裕度为70度。

不同的仿真方式所得到的结果略有误差。

运算放大器实验报告

运算放大器实验报告运算放大器实验报告引言运算放大器(Operational Amplifier,简称OP-AMP)是一种广泛应用于电子电路中的集成电路元件。

它具有高增益、高输入阻抗和低输出阻抗的特点,被广泛用于信号放大、滤波、积分、微分等各种电路中。

本实验旨在通过实际操作,深入了解运算放大器的基本原理和应用。

实验目的1. 了解运算放大器的基本原理和特性;2. 熟悉运算放大器的实际应用;3. 掌握运算放大器的参数测量方法。

实验装置和材料1. 运算放大器实验箱;2. 直流电源;3. 电阻、电容等基本元件;4. 示波器、信号发生器等测试仪器。

实验步骤1. 搭建基本的运算放大器电路,并接通电源;2. 测量运算放大器的输入和输出电压,并计算增益;3. 将运算放大器用于反相放大电路,并测量增益;4. 将运算放大器用于非反相放大电路,并测量增益;5. 将运算放大器用于比例积分放大器电路,并测量增益和相位延迟;6. 将运算放大器用于差分放大器电路,并测量增益和共模抑制比。

实验结果与分析1. 在基本的运算放大器电路中,输入电压为1V,输出电压为10V,计算得到增益为10。

这符合运算放大器的基本特性,即输出电压等于输入电压乘以增益。

2. 在反相放大电路中,输入电压为1V,输出电压为-10V,计算得到增益为-10。

反相放大电路可以将输入信号进行180度的相位翻转,并放大到一定倍数。

3. 在非反相放大电路中,输入电压为1V,输出电压为10V,计算得到增益为10。

非反相放大电路可以将输入信号放大到一定倍数,但不改变其相位。

4. 在比例积分放大器电路中,输入为正弦波信号,通过测量输出电压和输入电压的相位差,计算得到增益和相位延迟。

增益和相位延迟与输入信号频率呈正相关关系。

5. 在差分放大器电路中,输入为两个不同的信号,通过测量输出电压和输入电压的差值,计算得到增益和共模抑制比。

差分放大器电路可以将两个输入信号的差值放大到一定倍数,并抑制它们的共同模式信号。

运算放大器稳定性及频率补偿学习报告

信息科学与技术学院模拟CMOS集成电路设计——稳定性与频率补偿学习报告姓名:学号:二零一零年十二月稳定性及频率补偿2010-12-3一、自激振荡产生原因及条件1、自激振荡产生原因及条件考虑图1所示的负反馈系统,其中β为反馈网络的反馈系数,并假定β是一个与频率无关的常数,即反馈网络由纯电阻构成,不产生额外的相移(0βϕ= );H (s )为开环增益,则()H s β为环路增益。

所以,该系统输入输出之间的相移主要由基本放大电路产生。

图1 基本负反馈系统 该系统的闭环传输函数(即系统增益)可写为:()()1()Y H s s X H s β=+ 由上式可知,若系统增益分母1()H s j βω==-1,则系统增益趋近于∞,电路可以放大自身的噪声直到产生自激振荡,即:如果1()H j βω=-1,则该电路可以在频率1ω产生自激振荡现象。

则自激振荡条件可表示为:1|()|1H j βω=1()180H j βω∠=-注意到,在1ω时环绕这个环路的总相移是360 ,因为负反馈本身产生了180 的相移,这360 的相移对于振荡是必需的,因为反馈信号必须同相地加到原噪声信号上才能产生振荡。

为使振荡幅值能增大,要求环路增益等于或者大于1。

所以,负反馈系统在1ω产生自激振荡的条件为:(1)在该频率下,围绕环路的相移能大到使负反馈变为正反馈;(2)环路增益足以使信号建立。

2、重要工具波特图判断系统是否稳定的重要工具是波特图。

波特图根据零点和极点的大小表示一个复变函数的幅值和相位的渐进特性。

波特图的画法:(1)幅频曲线中,每经过一个极点P ω(零点Z ω),曲线斜率以-20dB/dec(+20dB/dec)变化;(2)相频曲线中,相位在0.1P ω(0.1Z ω)处开始变化,每经过一个极点P ω(零点Z ω),相位变化-45 (±45 ),相位在10P ω(10Z ω)处变化-90 (±90 );(3)一般来讲,极点(零点)对相位的影响比对幅频的影响要大一些。

全差分运算放大器中共模稳定性的分析

Ab ta t Deinc n ieain r rs ne rsa i zn ec mmo — d e b c ( MF sr c : sg o sd rt saep ee tdf tbl igt o o o i h n mo ef d a k e C B) lo l o pi f l nuy

的框 图。

共模反馈电路环路首先检测共模输出平均电压 ( o + 0 ) ,然后产生一个关 于 V cV m的信 Vn vP / 2 o— c

的电路关于对称轴是完美的匹配并且对称的 , 避免 了镜像极点 , 从而获得 了更高的闭环速度。

然而 ,全差 分运算 放 大器最 主要 的一 个缺 点是 需 要 共 模 反 馈 电路 (o mo oe ̄ dak cm n m d ebc ,

C B) MF 来控 制共 模输 出 电压 。 在一个 实 际 的差 分 电 路 中 , 电流源 ( 拉 电流 源 ) n型 电流 源 ( P型 上 与 下

s at t es’

.

T e cr u t mp e n e n 0 1 u CMOS mie in l r c s f MI sp e e t d b s d o l e h i i i l me t d i . 8 m c x d sg a o e so p S C i r s n e . a e n af d d o

d f r n il otg e b c MOS a l e s s d i r g a i e e t l ef d a k C f av a e mp i r e p o r mma l a n C n rl mp i e s A e o sd r t n i f u n b e g i o t o a l r . f r n ie a i si i f t c o n

典型的两级运放环路稳定性分析

典型的两级运算放大器环路稳定性分析典型的两级运算放大器环路稳定性分析典型的两级运放如图所示,负载电容CL=50fF 。

首先建立静态工作点。

首先建立静态工作点。

加偏置电流加偏置电流I0=4uA,加共模输入电平1.25V 。

仿真后得到结果如下,仿真后得到结果如下,静静态工作点是合适的。

态工作点是合适的。

1. 开环分析开环分析米勒补偿前做开环分析如下,显然,这是不合适的。

米勒补偿前做开环分析如下,显然,这是不合适的。

加米勒补偿电容Cc=200fF,做开环分析如下,显然,这也是不合适的。

这是由于电路中存在零点造成的。

存在零点造成的。

加入调零电阻Rz=40K,,仿真结果如下。

可以看出,,,相位裕度为40度,不够。

可通过加大补偿电容来进一步分裂p1,p2主次极点。

(已尝试过加米勒补偿电容Cc=300fF可以得到大于60度的相位裕度)。

但是本次设计的运放用在负反馈环路中,故只需要负反馈环路是稳定的就达到设计标准。

运放用在负反馈环路中,故只需要负反馈环路是稳定的就达到设计标准。

理论计算。

理论计算。

查看各管子的静态工作点。

查看各管子的静态工作点。

,,,即。

,,,即。

,非常接近。

理论值与仿真结果非常接近。

,理论值与仿真结果非常接近。

,非常接近。

,理论值与仿真结果非常接近。

,,理论值度偏差较大。

与仿真结果40度偏差较大。

2.在负反馈环路中做环路稳定性分析:在负反馈环路中做环路稳定性分析:从上图可以看出,加入反馈电阻网络R1,R2后就打破了原有的静态工作点:主要是反馈电阻网络R1,R2中的电流由M7管提供,所以M7管的静态工作点打破了,即运放的第二级跨导GmⅡ,输出电阻R2都变了。

从波特图中可以看出相位裕度为77度,满足设计标准。

理论计算:理论计算:查看各管子的静态工作点。

查看各管子的静态工作点。

,,,即。

,,,即。

,非常接近。

,理论值与仿真结果非常接近。

,理论值与仿真结果非常接近。

,此时,相位裕度为63度,满足设计标准。

运算放大器稳定性分析3

Several example circuits ready for open-loop simulation are shown here. They can be used for review if there is confusion regarding where to break the loop in many standard circuit configurations. Note that for proper stability analysis, any output loading must remain directly on the output of the op amp and should not be placed on the other side of the inductor. Doing so would remove the effects the output loads have on the op amp output. 很多电路可以运用开环 SPICE 电路仿真,在实际电路中不知在何处断开 环路而感到困惑时可以用这些例子作为参考。 注意为了得到正确的稳定性分析结论,运放输出端所接的负载必须直接 体现在电路中,且不应该放置在电感的另外一端,否则就体现不同的负 载效应。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

●Hello,and welcome to the TI Precision Lab supplement for op amp stability.●This lab will walk through detailed calculations,SPICE simulations,and real-worldmeasurements that greatly help to reinforce the concepts established in the stability video series.●你好,欢迎来到TI Precision Labs(德州仪器高精度实验室)的运放稳定性环节。

●这个实验会包括计算,SPICE仿真和实际测试。

这些环节帮助大家对视频中的概念加深理解。

●The detailed calculation portion of this lab can be done by hand,but calculationtools such as MathCAD or Excel can help greatly.●The simulation exercises can be performed in any SPICE simulator,since TexasInstruments provides generic SPICE models of the op amps used in this lab.However,the simulations are most conveniently done in TINA-TI,which is a free SPICE simulator available from the Texas Instruments website.TINA simulation schematics are embedded in the presentation.●Finally,the real-world measurements are made using a printed circuit board,orPCB,provided by Texas Instruments.If you have access to standard lab equipment,you can make the necessary measurements with any oscilloscope, function generator,Bode plotter,and±15V power supply.However,we highly recommend the VirtualBench from National Instruments.The VirtualBench is an all-in-one test equipment solution which connects to a computer over USB or Wi-Fi and provides power supply rails,analog signal generator and oscilloscope channels,and a5½digit multimeter for convenient and accurate measurements.This lab is optimized for use with the VirtualBench.●本实验的计算可以通过實際計算,如果使用Mathcad或者Excel这样工具会更好。

●仿真环节可以使用任何SPICE仿真器,因为在本实验中提供的是德州仪器提供通用的运放的SPICE的模型。

用TINA-TI实施这些仿真是最方便的。

TINA 是免费的SPICE仿真器,可以从TI的网站上下载。

TINA仿真原理图会附在PPT中。

●最后,真实的测试会使用TI提供的印刷电路板。

如果你有标准的实验设备,可以用示波器,波形发生器,波特仪和±15V电源来进行测试。

我们推荐使用国家仪器的虚拟仪器。

这套虚拟仪器是一套多功能集成设备,可以通过USB或者WIFI与电脑连接。

这台仪器提供电源,信号发生器,示波器和5位半的万用表,方便进行精确测试。

本实验因搭配使用虛擬儀器而優化電路量測。

●In experiment1,we’ll determine the phase margin,and therefore the stability,ofa buffer circuit which is being used to drive a large capacitive load.We’lldetermine the phase margin by observing the transient overshoot as well as the AC transfer characteristic.●在实验1,我们会决定带大电容负载的缓冲电路的相位裕度和稳定性。

我们也会通过观察瞬态的过冲和AC传输特性来确定稳定性。

●First,calculate the phase margin and percentage overshoot for the circuit shownhere,using the techniques and equations given in the stability e the plots given on the next slide.●首先,使用稳定性章节中的公式和方法来计算这里所示电路的相位裕度和过冲量。

图形会在下一页给出。

●This circuit uses the OPA277.In order to perform the calculations,you need toknow the percent overshoot versus load capacitance for that device,shown on the top left.Then,use the plot on the right to determine the phase margin from that percentage overshoot.●Enter your answers in the table at the bottom of the slide.The solutions arealready provided to allow you to check your work.●这个电路使用OPA277,为了计算过冲及相位裕度,你必须知道这颗元件过冲程度和容性负载的关系,如左上图所示。

再使用右图来确定相位裕度和过冲的关系。

●你可以在ppt下面的表格中输入你的答案。

这个可以用来检验你的结果。

●The next step is to run a SPICE simulation analysis for the transientovershoot.The necessary TINA-TI simulation schematic is embedded in this slide set–simply double-click the icon to open it.To run the analysis,click Analysis Transient,and run the analysis from100us to250us.The input is a20mVpk, 10kHz square wave.●下一步是进行SPICE的暂态过冲仿真。

TINA的仿真电路图附在ppt中,双击图标即可打开。

仿真步骤如下:点Analysis Transient。

仿真时间从100us 到250us。

输入信号为20mVpk,10kHz方波●You should see a result similar to e the simulated percentage overshootof40%to calculate the phase margin,which comes out to31degrees.●你可以通过仿真得到和上图相似的结果。

仿真得到的40%的过冲可以换算成31度的相位裕度。

●Next,run a SPICE simulation analysis for the AC transfer characteristic.This willallow us to see the op amp’s AC peaking,which is another indicator of phase margin.●Use the same TINA-TI simulation schematic as before.To run the analysis,clickAnalysis AC Analysis AC Transfer Characteristic.Run the analysis from10kHz to10MHz.●接下来,进行AC传递函数的SPICE仿真分析。

这可以让我观察运放的AC起翘(peaking),这是表征相位裕度的另一个指标。

●使用和之前一樣的TINA的原理图。

点击click Analysis AC AnalysisAC Transfer Characteristic进行仿真。

仿真频率从10kHz到10MHz●You should see a result similar to this.The6.7dB of simulated AC peaking resultsin a phase margin of approximately27degrees.●你可以看到一个相似的仿真结果。

仿真得到的6.7dB AC起翘得到27度的相位裕度。

●Make sure to disable the DC power supply before setting up the test PCB!In theVirtualBench software,click the power button in the DC Power Supply area to turn off the power.Check the front panel of the VirtualBench unit to make sure the LEDs are OFF!Also ensure that the function generator is OFF.●測試電路之前,請先確定直流電源是關閉的.在虛擬儀器軟體中,點擊電源按鈕關閉電源,觀察前面板的發光二極體是關閉的已確定電源關閉.訊號產生器也必須是關閉的.●To prepare the test board for the measurement,install the jumpers and deviceson circuit5as shown here.Install JMP17,JMP18,JMP19,JMP20,JMP48,and JMP50,as well as the OPA277in socket U7.●为了准备测试用的测试板,按图所示安装电路5的跳针和器件。