阻抗设计指引

阻抗制作规范操作指引

1、目的:为规范制作阻抗PCB的阻抗计算和阻抗图形设计方法,确保成品的阻抗符合规定,使阻抗制作标准化,简单化。

2、范围:适用于本厂客户要求阻抗控制的PCB阻抗设计及CAM制作的阻抗图形设计。

3、参考文件无4、定义4.1特性阻抗(Characteristic Impedance)当一条导线与大地绝缘后,导线与大地彼此之间的阻抗。

4.2 差分阻抗(Differential Impedance)二条平行导线与大地绝缘后的阻抗,两条导线与大地彼此之间的阻抗。

5、职责5.1 PE工程部:负责客户阻抗资料的确认和设计制作;5.2 PROD生产部:按照操作指示和制作指示进行生产;5.3 QA品保部:阻抗板在制作过程中的品质监控及确认;5.4 ME工艺部:为阻抗板在制作中提供技术支持。

6、作业内容6.1 客户资料确认6.1.1确认客户压合结构可否满足阻抗控制要求。

6.1.2确认阻抗控制范围是否合理,一般情况下公差标准为±10%。

6.1.3阻抗层控制阻抗线粗设计是否合理,无阻抗线层尽量不做阻抗控制,以降低制作难度。

6.1.4评估客户阻抗控制有否特殊要求,厂内能力能否满足客户要求。

6.2阻抗设计基本原则6.2.1抗设计计算采阻抗计算软件进行计算,根据客户阻抗要求,分别输入介电常数、铜厚、线宽、线距、介电层厚度等相关参数,然后根据我司生产能力制作我司生产工作指示(MI),以指导现场生产。

6.2.2压合结构的确认根据客户要求设计压合结构,除客户指定的压合结构外,压合结构设计的一般原则如下: 6.2.1优先选用厚度较大的基板(尺寸稳定性较好);6.2.2优先选用低成本(或低成本组合)PP;备注:对于同种玻璃布型prepreg,树脂含量高低基本不影响价格,pp厚度与价格无必然联系,特殊PP(如2113,2112,3113,1506,106)价格一般较普通PP(7628, 7630,1080,2116)贵30%以上,为节约成本,在保证压合品质的前提下,PP张数尽量少用,尽量避免使用特殊PP。

Buck设计经验注意事项

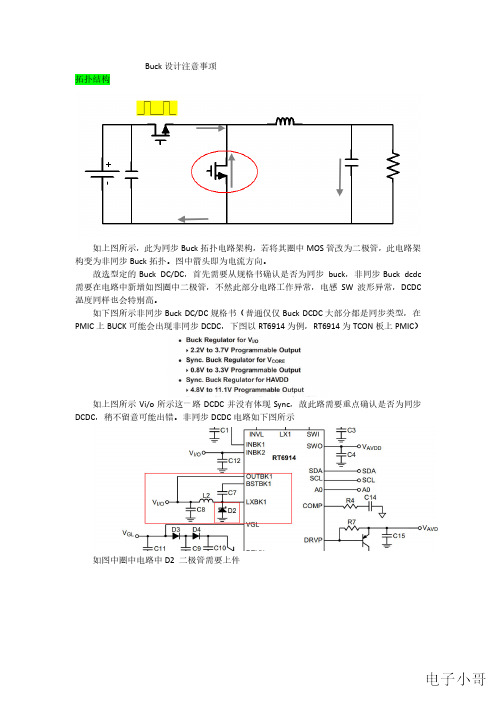

Buck设计注意事项拓扑结构如上图所示,此为同步Buck拓扑电路架构,若将其圈中MOS管改为二极管,此电路架构变为非同步Buck拓扑。

图中箭头即为电流方向。

故选型定的Buck DC/DC,首先需要从规格书确认是否为同步buck,非同步Buck dcdc 需要在电路中新增如图圈中二极管,不然此部分电路工作异常,电感SW波形异常,DCDC 温度同样也会特别高。

如下图所示非同步Buck DC/DC规格书(普通仅仅Buck DCDC大部分都是同步类型,在PMIC上BUCK可能会出现非同步DCDC,下图以RT6914为例,RT6914为TCON板上PMIC)如上图所示Vi/o所示这一路DCDC并没有体现Sync,故此路需要重点确认是否为同步DCDC,稍不留意可能出错。

非同步DCDC电路如下图所示如图中圈中电路中D2 二极管需要上件本文下部分将Buck电路的设计经验如下分享:1.怎么算最大输出电压(输入输出最少压差)Buck输入电压与输出电压公式Vout=Vin*D (D为占空比)有部分DCDC最大支持100%占空比,那此类DCDC输入与输出压差很少。

如SC8102另外部分DCDC并不支持此类最大100%占空比,如MP2329,需要从规格书给出datasheet 中推导出最大压差由图中可知道Fs典型值为700K 周期约等于1429ns最小输出电压为Vin*50/1429=3.5%Vin最大输出电压为Vin*(1429-200)/1429=86%Vin输入输出最少保持压差为14%Vin以上计算为理论值,实际情况会考虑偏差及其效率,可能会更低一些。

除以上公式还需要详细参考其规格书,如MPS2491C规格书中有部分额外说明在输入输出电压临近的时候,可以通过降低开关频率,把占空比提升上去,如上图可以将占空比提升到98%2.怎么设置EN电压EN为dcdc使能引脚,通过控制该引脚电平开关,可以达到控制DCDC输出电压时序,但如果正常工作时候ENpin电压设置不对,可能会导致关机掉电波形异常。

Tooling设计制作指示(华改)

文件名称Tooling 设计制作工作指示页次版本号修订号文件编号JV-WI-ME-1-104 1/40 B B-0 制定部门工艺部初定日期2009/3/31 生效日期2010/12/22修订履历版本/修订号修订内容简述A-0A-0→B-0 新制定。

全面修订。

发行和修订签署签署部门会签签名生产部品质部√工程部√工艺部√研发部√计划部管理部采购部维修部编制人蔡绪开批准备注:在需“会签”栏内打“√”(无需会签则栏空)文件名称Tooling 设计制作工作指示页次版本号修订号文件编号JV-WI-ME-1-104 2/40 B B-0 制定部门工艺部初定日期2009/3/31 生效日期2010/12/22 1.0目的:本文的目的是为公司的Tooling设计制作(包括板边设计、干菲林Tooling制作、白字&绿油Tooling制作及钻孔Tooling制作)建立一个标准指引。

2.0适用范围:本文件内容适用深圳中富电路有限公司。

3.0参考文件:3.1制作技术标准。

3.2工艺标准。

3.3工程更改通知。

4.0定义:无5.0责任:5.1工程部负责Tooling制作。

5.2品质部负责Tooling检测确认。

5.3工艺部负责Tooling技术能力提升。

6.0作业内容:板边工艺孔设计:6.1内层6.1.1内层板边工艺孔设计:文件名称Tooling 设计制作工作指示页次版本号修订号文件编号JV-WI-ME-1-104 3/40 B B-0 制定部门工艺部初定日期2009/3/31 生效日期2010/12/22 6.1.1.1对于正常的内层板,板边设计一般包括以下项目:名称符号数量(个) 用途TARGET HOLE 长边和短边各3个管位孔:钻孔定位,伸缩、偏移参考孔TEST HOLE N/A 8 测背光与铜厚AOI管位孔N/A 2 AOI机检查定位孔靶标,与熔合定位孔共用铆钉管位孔6、8 铆钉机铆钉靶标同心圆 4 内层菲林对位检查及层偏检测内层E-T定位孔N/A N/A 内层电测试定位孔靶标内层菲林对位PAD 4 内层菲林拍板BOOK对位孔阻流块N/A N/A 控制内层介电层型号标志Coupon N/A 1 标志生产型号、日期、层数等信息热熔Coupon N/A N/A 热熔点图形层偏短路检测靶标N/A 4 检测偏移蚀刻测试线N/A 4 检测显影、蚀刻用(工艺边四角)文件名称 Tooling 设计制作工作指示页次 版本号 修订号 文件编号 JV-WI-ME-1-104 4/40 BB-0制定部门工艺部初定日期2009/3/31生效日期2010/12/226.1.1.2工艺靶标设计示例图:夹边板条RR4.775MM多层板板边设计图示(以上各指示位置仅供参考)RR86.00MM62.00MM 90.00MM90.00MM文件名称Tooling 设计制作工作指示页次版本号修订号文件编号JV-WI-ME-1-104 5/40 B B-0 制定部门工艺部初定日期2009/3/31 生效日期2010/12/22a.内层-菲林拍板对位PAD设计:如下图所示(蝴蝶PAD),共4个。

生产制作指示编写指引培训资料

1.0 目的确定编制MI的内容、要求与方法,规范MI的编制; 保证客户的各项要求已经全部得到落实,生产过程所需要的指引已经清晰; 确保编制出的MI格式规范、内容全面同时准确无误,满足客户与生产的要求。

2.0 范围适用于《生产制作指示》的编写与审核2.1 定义:MI是英文Manufacturing Instruction的缩写,即生产制作指示;是工程设计人员根据客户的要求与行业通用标准,结合本公司的具体情况策划出产品的制作流程,与各加工过程的要求与指引。

2.2 名词定义:2.2.1 过孔(via hole):仅起导通作用的孔,连结过孔的一定是两条或者两条以上且在不一致层面的线,过孔通常都盖阻焊油墨。

其孔径大小通常在:0.10-0.80mm之间,在推断≥ 0.50MM且阻焊开窗的孔是否为过孔时,要结合字符层及其线路连接属性慎重推断。

2.2.2 孔环(RING):指焊盘边缘到孔边缘的距离。

2.2.3 导线(走线): 设定点连成的折线或者直线称之导线,导线要紧起电气连接与信号传输作用。

2.2.4 焊盘(PAD):印制导线的终点,用于器件焊接或者线路与孔的连接;分为内层焊盘与外层焊盘,形状有圆形、方形、椭圆形、圆矩形、泪滴形等;阻焊涂覆时能够开窗,也能够覆盖油墨。

2.2.5 线隙即线距。

相邻导线间的空间距离。

2.2.6 补偿与预大:为补偿后续加工中蚀刻造成线路或者焊盘宽度的减小,在工程处理时根据铜箔的厚度对客户提供的线路图形进行相应的预先放大,包含线路、焊盘、IC焊盘、大铜面与蚀刻字等所有内容。

2.2.7 铜皮(大铜面):都指较大面积的铜面(含网格),大铜通常起大地与区域性电源或者散热作用。

2.2.8 成型线:指外型线、V-CUT线、印制板内的槽或者孔的边缘轮廓线。

2.2.9 露线:指阻焊开窗时由于放大尺寸过大,或者对位偏差造成与焊盘相邻的导线或者大铜面不能被阻焊覆盖的现象。

2.3 MI的构成:MI由制作流程指示、钻孔表、开料,拼板及层压图、分孔图、各层菲林修改指示图、外型图、V-CUT图、工程更换通知单构成。

PCB天线走线,PCB天线阻抗计算,射频LAYOUT,CITS25

Polar_Si9000(PCB…).zip 16.17MB

文件是下图的计算数据

嘉立创PCB参数数据 技术/拼版服务 - 深圳市嘉立创科技发展有限公司 09:11:06

沉金厚度:0.02-0.03UM(微米)左右,喷锡:平均厚度大于15UM(微米), 铜箔平均厚度大于30UM(微米)孔铜平均厚度 大于18UM(微米), 阻焊油厚度在10-15UM(微米)左右,字符油厚度在5-8UM(微米)左右。FR4 PCB介电常数Er=4.5,CEr=3.8

2:Quectel_射频LAYOUT_应用指导_V2.2.pdf 移远天线LAYOUT规则

Quectel_射频LAYO…2.pdf 1001.42KB

3:以下文档讲得多,但不够通俗

阻抗板制作设计指引.doc 410.5KB

阻抗设计制作培训3.doc 804KB

SI9000计算

JLC7628层压结构… 算.Si9 380.24KB

电阻式触摸屏设计指南

一. 电阻式触摸屏概述

假设触摸屏为 Flim-Glass 结构(如下图三所示), X 在 Glass 层检测,Y 在 Film 层检测.如下图四所示,在上面板 Film 上加一电压则从下面板的 Glass 上 可检出 X 轴电压,经 A/D 转换后即可得 X 轴坐标.同理在下面板 Glass 上加一电 压则可从上面板 Film 上检出 Y 轴电压,经 A/D 转换后即可得 Y 轴坐标.如此动 作交替读取 X、Y 轴的 DATA 构成一个位置点的 DATA.这就是电阻式触摸屏的基 本工作原理.注意的是在上下电极没有接触好时会产 生接触电阻,有时接触和非 接触反复会导致输入信号混乱,不能形成正常的 DATA 而出现飞线等异常情况. 在电阻 式触摸屏起导通作用的 ITO(氧化铟)为弱导电体,特性是当厚度降到 1800 个埃(埃=10-10 米)以下时会突 然变得透明,透光率为 80%以上.ITO 膜比较薄且容易脆断,涂得太厚又会降低透光且形成内反射降低清晰度,ITO 膜 外虽多加了一层薄塑料保护层,但依然容易被锐利物件所破坏;且由于经常被触 动,ITO 使用一定时间后会出 现细小裂纹,甚至变形,如其中一点的外层 ITO 受 破坏而断裂,便失去作为导电体的作用.

图五 低反射技术示意图

二. 电阻式触摸屏主要技术参数

(4).防污迹(Anti-Glare/AG) 因为使用中触摸屏表面易产生手指印等污迹且难擦除,而 AG 技术可以降低 TP 表面的手指印的附着和更容易 擦除所存在的污迹,从而可提供触摸屏的显示效果.综合 ANR,AR,AG 技术的 FF 设计其结构组成可见下图 六,FG,FP 结构 的设计原理一样.

三.电阻式触摸屏设计注意事项

2.结构设计注意事项

因触摸屏使用不当时会造成线性度变差甚至失效等,故设计时要将触摸屏做为消耗品进行结构设计,结构上要方 便拆装. 手写笔头的材料可采用 POM 或 PC,两者对触摸屏的磨损影响不大,但采用POM 材料,笔尖本身较不易磨损. 手写笔的笔尖 R 对触摸的磨损影响很大,建议要大于大于或等于 0.8mm. 为避免触摸屏受力时压到 LCD 显示屏,在触摸屏玻璃与 LCD 玻璃之间应留有 0.3mm 的间隙.同时要注意这一 间隙的密封防尘,以避免灰尘的进入. 触摸屏的尺寸设计主要是根据 LCD的外形尺寸、显示区域、手写笔的直径进行综合考虑确定.

动态设计阻抗coupon提高拼板利用率

报告人:撰写时间:目录一小组介绍 (3)二选择课题 (3)三目标设定 (3)四对策实施 (4)1.MI制作模块的优化和利用率提升 (4)2.PT阻抗描述的简化 (6)3.CAM阻抗coupon的简化 (10)4.阻抗资料的优化 (12)五测量数据分析 (13)六效果分析 (13)1.有形效果 (13)2.无形效果 (14)3.纳入标准 (14)七总结及展望 (14)一、小组介绍1.不断降低成本,追求利润的最大化,永远是一个企业长期的目标。

随着日益激烈的市场竞争,生产物料价格的不断上涨,人力资源成本的不断增加,大规模集中生产的利润空间越来越狭窄,其中提高板料的利用率更是重中之重。

为此我们产品工程部系统自动化小组专门成立了拼版利用率最大化研究团队,分析当前拼版情况下是否存在利用率的提高空间,为公司的节省成本做出应有的贡献;2.为了更好的迎合市场需要,GME对产品类型做出了相应的调整,现在高层板的阻抗数量越来越多,而旧的阻抗Coupon设计规则是固定尺寸为0.3x4Inch,每个Coupon中一个线路层只能设计有一根单线阻抗或一组双线阻抗,相邻层不能设计有阻抗线,阻抗参考层不能设计有阻抗线,同时每个阻抗coupon最多加8根单线阻抗或加4组双线阻抗;由于设计规则中太多的局限性导致阻抗Coupon数量显著增加,为了能在生产拼版中放置全部阻抗Coupon而不得不减少成品在生产拼版中的数量,降低成品的利用率;3.为了改善因旧阻抗Coupon设计的局限性导致成品利用率降低的问题,同时更有效更灵活的进行拼版设计,我们设计了一套新的阻抗Coupon设计规则,动态设计阻抗Coupon的数量和尺寸以达到最大化提高板料的拼版利用率,同时,编写更智能的阻抗Coupon自动设计程序,简化MI和CAM的设计和制作,避免人为失误,同时节约了人工,从而达到降低成本的根本目的;三、目标设定本次活动计划由PE提出,经过全体组员商议通过,形成如下计划目标:A.在板料拼版时,动态设计阻抗Coupon的数量和尺寸以达到最大化利用板料,提高拼版利用率2%。

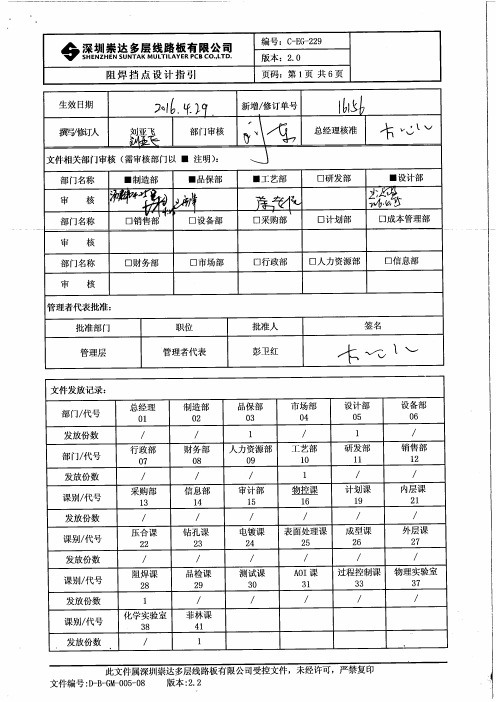

阻焊挡点网设计规范

文件撰写及修订履历1.0 目的制定阻焊挡点菲林制作规范,指导设计部CAM课制作阻焊挡油点菲林(DDD菲林),方便各部门配合生产及产生问题的追溯。

2.0 范围阻焊挡点菲林的制作。

3.0 定义无4.0 职责工艺部:负责制定阻焊挡点菲林设计规范及界定;设计部:负责按照新规范制作阻焊挡点菲林;品保部:负责对阻焊挡点菲林设计规范监控;制造部:负责按新的规范使用阻焊挡点菲林;5.0 作业内容 /程序5.1 作业流程图客户提供原稿设计资料→设计部根据厂内规范进行优化原稿设计资料→菲林组按要求出生产工具→阻焊课使用对应的生产工具进行生产→品保部进行检查产品是否符合要求→不符合品质要求时通知工艺跟进解决(符合要求时直接出至下工序)5.3 NPTH 孔制作标准5.3.1 阻焊NPTH 孔挡点一律按比钻嘴单边大0.2mm 制作;5.3.2 当NPTH 孔挡点距盖油铜皮或盖油线路间距<0.2mm 时,需削挡点处理(当周围为大铜皮时,需削铜皮处理);5.4 沉孔制作标准(先沉孔后阻焊)5.4.1 以比沉孔直径之最大值单边大0.12mm 制作;5.4.2 当沉孔挡点距盖油铜皮或盖油线路间距<0.2mm 时,需削挡点处理(当周围为大铜皮时,需削铜皮处理);5.5 内锣槽、外凹槽或切口等情况时,阻焊挡油点开窗大小按比内锣槽或外凹槽单边小0.2mm ;5.6 V-CUT 以后的板及单元板返工之挡油点菲林制作方法5.6.1 V-CUT 线按单边加大0.15mm 制作挡油点;5.6.2 外型线外按单边缩小0.15mm 制作挡油点5.7 杂色油墨金手指板丝印挡油点菲林设计5.7.1 挡油点菲林上将金手指区加挡油块(比该位置绿油开窗单边小0.1mm 制作)5.8 阻焊靶标位加阻焊挡油点5.8.1 非电金板挡油点制作:在挡油点菲林之靶标位加比靶标点边缘单边大6mm 的正方形挡油点(如下图),挡油点需距成型线1mm ,空间不足处削靶标位挡油点PAD5.8.2 电金板挡油点制作:5.8.2.1 黑油、哑黑油、蓝油之电金板按5.9.1点要求加靶标位挡油点5.8.2.25.9 加印阻焊桥挡油点菲林与曝光桥位菲林制作5.9.1 加印阻焊桥之印油菲林:将所有≤0.2mm 的阻焊桥位印油,印油区比外层IC 线路单边大0.15mm5.9.2 加印桥之曝光桥位菲林:加印桥曝光桥位菲林比原正常阻焊桥单边小0.01mm 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

阻抗设计指引1.0、目的确定阻抗控制的要求,规范阻抗计算方法,拟定阻抗测试Coupon设计之准则,确保产品能够满足生产的需要及客户要求。

2.0、范围所有需要阻抗控制产品的设计、制作及审核。

2.1、定义特性阻抗的定义:在某一频率下,电子器件传输信号线中,相对某一参考层,其高频信号或电磁波在传播过程中所受的阻力称之为特性阻抗,它是电阻抗,电感抗,电容抗……的一个矢量总和。

2.2、特性阻抗的分类:目前我司常见的特性阻抗分为:单端(线)阻抗、差分(动)阻抗、共面阻抗此三种情况。

2.2.1、单端(线)阻抗:英文Single Ended Impedance ,指单根信号线测得的阻抗。

2.2.2、差分(动)阻抗:英文Differential Impedance,指差分驱动时在两条等宽等间距的传输线中测试到的阻抗。

2.2.3、共面阻抗:英文Coplanar Impedance ,指信号线在其周围GND/VCC(信号线到其两侧GND/VCC间距相等)之间传输时所测试到的阻抗。

3.0、职责3.1、工程部负责本文件的编制及修订。

3.2、MI设计人员负责对客户资料中阻抗要求的理解及转换,负责编写阻抗控制的流程指示、菲林修改指示及阻抗测试Coupon的设计。

MI在生产使用过程中负责解释相关条款内容。

3.3、品保部QAE负责对工程资料的检查及认可。

4.0、内容4.1、阻抗设计流程:测量阻抗是否符合客户要求4.2、阻抗控制需求的决定条件:当信号在PCB导线中传输时,若导线的长度接近信号波长的1/7,此时的导线便成为信号传输线,一般信号传输线均需做阻抗控制。

PCB制作时,依客户要求决定是否需管控阻抗,若客户要求某一线宽需做阻抗控制,生产时则需管控该线宽的阻抗。

4.3、阻抗匹配的三个要素:4.3.1、输出阻抗(原始主动零件) 特性阻抗(信号线) 输入阻抗(被动零件)(PCB板)阻抗匹配4.3.2、当信号在PCB上传输时,PCB板的特性阻抗必须与头尾元件的电子阻抗相延误等现象,从而导致信号不完整,信号失真。

4.4、阻抗影响因素:4.4.1、Er:介质介电常数,与阻抗值成反比,介电常数按新提供的《板材介电常数表》计算。

4.4.2、H1,H2,H3...线路层与接地层间介质厚度,与阻抗值成正比。

4.4.3、W1:阻抗线线底宽度;W2:阻抗线线面宽度,与阻抗成反比。

A:当内层底铜Hoz时,W1=W2+0.3mil;当内层底铜为1oz时W1=W2+0.5mil;当内层底铜为2oz时,W1=W2+1.2mil 。

B:当外层底铜为Hoz,W1=W2+0.8mil;外层底铜为1oz,W1=W2+1.2mil;当 外层底铜为2oz时,W1=W2+1.6mil。

C:W1为原稿阻抗线宽。

4.4.4、T:铜厚,与阻抗值成反比。

A:內层为基板铜厚,Hoz按15um计算;1oz按30um计算;2oz按65um计算.B:外层为铜箔厚度+镀铜厚度,依据孔铜規格而定,当底铜为Hoz,孔铜(平均20um,最小18um )时,表铜按45um计算;孔铜(平均25um,最小20um)时,表铜按50um计算;孔铜单点最小25um时,表铜按55um计算。

C:当底铜为1oz,孔銅(平均20um,最小18um )时,表铜按55um计算;孔 铜(平均25um,最小20um)时,表铜按60um计算;孔铜单点最小25um时,表铜按65um计算。

4.4.5、S:相邻线路与线路之间的间距,与阻抗值成正比(差动阻抗)。

4.4.6、C1:基材阻焊厚度,与阻抗值成反比;C2:线面阻焊厚度,与阻抗值成反比;C3:线间阻焊厚度,与阻抗值成反比;CEr:阻焊介电常数,与阻抗值成反比。

A:印一次阻焊油墨,C1值为30um ,C2值为12um ,C3值为30um。

B:印两次阻焊油墨,C1值为60um ,C2值为25um ,C3值为60um。

C:Cer(阻焊介电常数):按3.4计算。

4.5、阻抗的计算:(POLAR SI8000计算模式) 4.5.1、常见的单端(线)阻抗计算模式:4.5.1.1、Surface Microstrip4.5.1.2、Coated Microstrip 4.5.1.3、Embedded Microstrip Surface Microstrip 1B适用范围:外层阻焊前阻抗计算: 参数说明:H1:外层到VCC/GND间的介质厚度 W2:阻抗线线面宽度W1: 阻抗线线底宽度Er1:介质层介电常数T1:线路铜厚,包括基板铜厚+电镀铜厚。

Coated Micrstrip适用范围:外层阻焊后阻抗计算:参数说明:H1:外层到VCC/GND间的介质厚度W2:阻抗线线面宽度W1: 阻抗线线底宽度Er1:介质层介电常数T1:线路铜厚,包括基板铜厚+电镀铜厚。

CEr:阻焊介电常数C1: 基材阻焊厚度 C2:线面阻焊厚度Embedded Microstrip 1B1A适用范围:与外层相邻的第二个线路层阻抗计算,例如一个6层板,L1、L2均为线路层,L3 为GND或VCC层,则L2层的阻抗用此方式计算.参数说明:H1:线路层到相邻VCC/GND间介质厚度H2:外层到第二个线路层间的介质厚度+第二 个线路层铜厚W2:阻抗线线面宽度W1:阻抗线线底宽度T1:阻抗线铜厚=基板铜厚Er1:介质层介电常数(线路层到相邻VCC/GND间介质)Er2:介质层介电常数(外层到第二个线路层间介质)4.5.1.4、Offset stripline4.5.1.5、Offset stripline4.5.1.6、Coated microstrip2B&Offset Stripline2B2A阻抗计算模式同4.5.1.2,仅多一介质层 阻抗计算模式同4.5.1.4,仅多两个介质层 (比如一个4层板,L1层需做阻抗控制,L2层 (比如一个8层板,L4层需做阻抗控制,L2,L6 为线路层,L3层为GND/VCC 参考层)。

层为GND/VCC 参考层,L2,L5为线路层)。

Offset Stripline 1B1A适用范围:两个VCC/GND 夹一个线路层之阻抗计算 参数说明:H1:线路层到较近之VCC/GND 间距离H2:线路层到较远之VCC/GND 间距离+线路层铜厚 Er1:介质层介电常数(线路层到相邻VCC/GND 间质) Er2:介质层介电常数(线路层到较远VCC/GND 间质) W2:阻抗线线面宽度 W1: 阻抗线线底宽度T1: 阻抗线铜厚=基板铜厚Offset Stripline 1B2A适用范围:两个VCC/GND 夹两个线路层之阻抗 计算;例如一个6层板,L2,L5层为GND/VCC,L3, L4层为线路层需控制阻抗. 参数说明:H1:线路层1到较近之VCC/GND 间距离 H2:线路层1到线路层2间距离+线路层1 和线路层2铜厚。

H3:线路层2到较远之VCC/GND 间距离 Er1:介质层介电常数(线路层1到相邻VCC/GND 间介质)Er2:介质层介电常数(线路层1到线路层2间介质)Er3:介质层介电常数(线路层2到较远VCC/GND 间介质)T1: 阻抗线铜厚=基板铜厚W2:阻抗线线面宽度 ; W1: 阻抗线线底宽度4.5.2、常见的差分(动)阻抗计算模式:4.5.2.1、Edge-coupled Surface Microstrip4.5.2.2、Edge-coupled Coated Microstrip4.5.2.3、Edge-coupled Embedded MicrostripEdge-Coupled Surface Microstrip 1B 适用范围:外层阻焊前差动阻抗计算 参数说明:H1:外层到VCC/GND 间的介质厚度 W2:阻抗线线面宽度 W1: 阻抗线线底宽度 S1:差动阻抗线间隙 Er1:介质层介电常数T1:线路铜厚,包括基板铜厚+电镀铜厚Edge-Coupled Coated Microstrip 1B 适用范围:外层阻焊后差动阻抗计算 参数说明:H1:外层到VCC/GND 间的介质厚度 W2:阻抗线线面宽度 W1:阻抗线线底宽度 S1:差动阻抗线间隙 Er1:介质层介电常数T1:线路铜厚,包括基板铜厚+电镀铜厚 CEr:阻焊介电常数 C1:基材阻焊厚度 C2:线面阻焊厚度C3:差动阻抗线间阻焊厚度Edge-Coupled Embedded Microstrip 1B1A适用范围:与外层相邻的第二个线路层差动阻抗计算 参数说明:H1:线路层到相邻VCC/GND 间介质厚度H2:外层到第二个线路层间的介质厚度+第二个线路层铜厚W2:阻抗线线面宽度 W1:阻抗线线底宽度T1:阻抗线铜厚=基板铜厚 Er1:介质层介电常数(线路层到相邻VCC/GND 间介质)Er2:介质层介电常数(外层到第二个线路层间介质) S1:差动阻抗线间隙4.5.2.4、Edge-coupled Offset stripline4.5.2.5、Edge-coupled Offset stripline4.5.2.6、Edge-coupled Offset striplineEdgd-Coupled Offset Stripline 1B1A适用范围:两个VCC/GND 夹一个线路层之阻抗计算; 参数说明:H1:线路层到较近之VCC/GND 间距离H2:线路层到较远之VCC/GND 间距离+阻抗线路层铜厚 Er1:介质层介电常数(线路层到相邻VCC/GND 间介质)Er2:介质层介电常数(线路层到较远VCC/GND 间介质)W2:阻抗线线面宽度 W1: 阻抗线线底宽度T1: 阻抗线铜厚=基板铜厚 S1:差动阻抗线间隙Edge-Coupled Offset Stripline 1B2A适用范围:两个VCC/GND 夹两个线路层之阻抗计算:例如一个6层板,L2、L5层为GND/VCC,L3、L4层为线路层需控制阻抗 参数说明:H1:线路层1到较近之VCC/GND 间距离H2:线路层1到线路层2间距离+线路层1,线路层2铜厚H3:线路层2到较远之VCC/GND 间距离Er1:介质层介电常数(线路层1到相邻VCC/GND 间介质) Er2:介质层介电常数(线路层1到线路层2间介质) Er3: 介质层介电常数(线路层2到较远VCC/GND 间介质)W2:阻抗线线面宽度 W1: 阻抗线线底宽度 T1: 阻抗线铜厚=基板铜厚 S1:差动阻抗线间隙Edge-Coupled Offset Stripline 1B2A1R适用范围:两个VCC/GND 夹两个线路层之阻抗计算: 例如一个6层板,L2、L5层为GND/VCC,L3、L4层为 线路层需控制阻抗 参数说明:H1:线路层1到较近之VCC/GND 间距离H2:线路层1到线路层2间距离+线路层1、线路层2铜厚H3:线路层2到较远之VCC/GND 间距离Er1:介质层介电常数(线路层1到相邻VCC/GND 间介质) Er2:介质层介电常数(线路层1到线路层2间介质) Er3:介质层介电常数(线路层2到较远VCC/GND 间介质)W2:阻抗线线面宽度 W1: 阻抗线线底宽度备注:当REr=Er2时,4.5.2.5计算的阻抗值则会等于4.5.2.6计算的阻抗值,因此一般情况下不用类似于4.5.2.6模式(含线间填充树脂)计算阻抗值。