实验一伪随机码发生器实验

伪随机码发生器研究与设计

伪随机码发生器的研究与设计Pseudo-random code generator Research and Design摘要伪随机序列产生技术是集数学、计算机科学、电子与通信等诸多学科于一身的技术,其产生技术自上世纪末至今一直是国内外的研究热点并取得了不少的成果。

伪随机码越来越受到人们的重视,被广泛应用于导弹、卫星、飞船轨道测量和跟踪、雷达、导航、移动通信、保密通信和通信系统性能的测量以及数字信息处理系统中。

目前国内外均有项目研究提高伪随机序列发生器可靠性、状态利用率等问题。

本课题介绍了伪随机码的应用和研究概况,研究了伪随机码的产生方式和产生原理,并以此为基础阐述了一种基于移位寄存器的m序列伪随机码发生器的设计与实现的方法。

最终在使用集成电路的前提下,先分析由移位寄存器电路构成的伪随机序列发生器的设计方法,分步设计了移位寄存器电路和同步复位信号发生电路;再通过一系列的误差和可靠性调整设计,最终用小规模集成电路和外加时钟信号设计实现了线性反馈移位寄存器产生周期P=15的m序列,并且给出了完整的实现电路和时序分析结果。

关键词:伪随机码,绕码,m序列,移位寄存器ABSTRACTPseudo-random sequence generation technique is a mathematics, computer science, electronics and communication, and many other subjects in one of the technology, its production technology since the end of the century has been the research focus at home and abroad and made a lot of results.Pseudo-random code more and more attention, is widely used in missiles, satellites, spacecraft orbit measurement and tracking, radar, navigation, mobile communications, secure communications and communication system performance measurement and digital information processing system. Research projects at home and abroad are pseudo-random sequence generator to improve reliability, availability status and other issues.This topic describes the application of pseudo-random code and research overview of the pseudo-random code generation means and generating principle, and described as the basis for an m-sequence shift register based pseudo-random code generator of the design and implementation Approach. Final premise in the use of integrated circuits, the first shift register circuits of the pseudo-random sequence generator design, step by step design of the shift register circuit and the synchronous reset signal circuit; then through a series of errors and reliable Adjustment design, end-users and small-scale integrated circuit design of the clock signal applied to achieve a linear feedback shift register generating cycle P = 15 m-sequence and provides a complete implementation of the circuit and timing analysis. Key words:Pseudo-random code,Around the code, m sequence,Shift register目录摘要 (Ⅰ)ABSTRACT (Ⅱ)目录 (Ⅲ)1 绪论 (1)1.1 伪随机序列的研究概况 (1)1.2 伪随机序列的应用领域及其意义 (1)1.3 课题研究内容与难点 (2)2 伪随机序列发生器 (3)2.1 伪随机序列的定义及其特点 (3)2.2 伪随机序列的产生 (3)2.3 伪随机序列反馈函数 (4)3伪随机码发生器电路设计 (7)3.1 移位寄存器电路设计 (7)3.2置数功能电路设计 (7)3.3可靠性附加电路设计 (8)3.4元器件选型 (10)3.5整体电路图 (10)4电路时序分析 (12)4.1移位寄存器电路时序分析 (12)4.2完整电路时序分析 (12)结束语 (14)参考文献 (15)附录芯片逻辑引脚图及各型号性能对比 (16)致谢 (17)1 绪论1.1 伪随机码的研究概况伪随机码又称伪随机序列或伪噪声序列。

伪随机码生成器

M序列发生器M序列是最常用的一种伪随机序列,是一种线性反馈移位寄存器序列的简称。

带线性反馈逻辑的移位寄存器设定各级寄存器的初试状态后,在时钟的触发下,每次移位后各级寄存器状态都会发生变化。

其中一级寄存器(通常为末级)的输出,随着移位寄存器时钟节拍的推移会产生下一个序列,称为移位寄存器序列。

他是一种周期序列,周期与移位寄存器的级数和反馈逻辑有关。

以4级移位寄存器为例,线性反馈结构如下图:4级以为寄存器反馈图其中a4=a1+a0信号a4:a0禁止出现全0,否则将会出现全0,序列不变化。

实验仿真Code:library IEEE;use IEEE.STD_LOGIC_1164.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--use IEEE.NUMERIC_STD.ALL;-- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity random_4 isPort ( clk : in STD_LOGIC;reset : in STD_LOGIC;din : in STD_LOGIC_VECTOR (3 downto 0);dout : out STD_LOGIC_VECTOR (3 downto 0);load : in STD_LOGIC);end random_4;architecture Behavioral of random_4 issignal rfsr :std_logic_vector(3 downto 0);--signal temp:std_logic;beginprocess(clk,reset,load,din)beginif (reset ='1') thenrfsr <=(others =>'0');elsif (clk' event and clk='1') thenif(load ='1') then ----load =1rfsr<= din;elserfsr(3) <= rfsr(0) xor rfsr(1);rfsr(2 downto 0) <= rfsr(3 downto 1);end if;end if;end process;------signal rename----dout <= rfsr;end Behavioral;testbench:LIBRARY ieee;USE ieee.std_logic_1164.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--USE ieee.numeric_std.ALL;ENTITY random_testbench ISEND random_testbench;ARCHITECTURE behavior OF random_testbench IS-- Component Declaration for the Unit Under Test (UUT)COMPONENT random_4PORT(clk : IN std_logic;reset : IN std_logic;din : IN std_logic_vector(3 downto 0);dout : OUT std_logic_vector(3 downto 0);load : IN std_logic);END COMPONENT;--Inputssignal clk : std_logic := '0';signal reset : std_logic := '0';signal din : std_logic_vector(3 downto 0) := (others => '0'); signal load : std_logic := '0';--Outputssignal dout : std_logic_vector(3 downto 0);-- Clock period definitionsconstant clk_period : time := 10 ns;---variablesignal cnt: integer :=0;BEGIN-- Instantiate the Unit Under Test (UUT)uut: random_4 PORT MAP (clk => clk,reset => reset,din => din,dout => dout,load => load);-- Clock process definitionsclk_process :processbeginclk <= '0';wait for clk_period/2;clk <= '1';wait for clk_period/2;end process;-- Stimulus processstim_proc: process(clk)begin-- hold reset state for 100 ns. if(cnt = 0) then--initializationreset <= '1' after 100 ps;load <= '1' after 100 ps;din <="0001";cnt <= cnt +1;---elsif(cnt =1) thenreset <= '0' after 100 ps;load <= '1' after 100 ps;din <="0001";cnt <= cnt +1;elsif(clk' event and clk ='1') then reset <= '0' after 100 ps;load <= '0' after 100 ps;din <="0001";---executuecnt <= cnt +1;if(cnt = 100) thencnt <= 2;end if;end if;end process;END;。

通信原理实验一

实验一:信号源实验第一部分 CPLD可编程逻辑器件实验一、实验目的1.了解ALTERA公司的CPLD可编程器件EPM240;2.了解本模块在实验系统中的作用及使用方法;3.掌握本模块中数字信号的产生方法。

二、实验仪器1.时钟与基带数据发生模块,位号:G2.示波器1台三、实验原理CPLD可编程模块(时钟与基带数据发生模块,芯片位号:4U01)用来产生实验系统所需要的各种时钟信号和数字信号。

它由CPLD可编程器件ALTERA公司的EPM240、下载接口电路(4J03)和一块晶振(4JZ01)组成。

晶振用来产生16.384MHz系统内的主时钟,送给CPLD芯片生成各种时钟和数字信号。

本实验要求实验者了解这些信号的产生方法、工作原理以及测量方法,理论联系实践,提高实际操作能力。

m序列是最被广泛采用伪随机序列之一,除此之外,还用到其它伪随机码,如Gold序列等,本模块采用m序列码作为系统的数字基带信号源使用,在示波器上可形成稳定的波形,方便学生观测分析。

下面介绍的m序列原理示意图和仿真波形图都是在MAX+PLUS II软件环境下完成。

其中,RD输入低电平脉冲,防止伪随机码发生器出现连0死锁,其对应仿真波形的低电平脉冲。

CLK为时钟脉冲输入端。

OUT为m序列伪随机码输出。

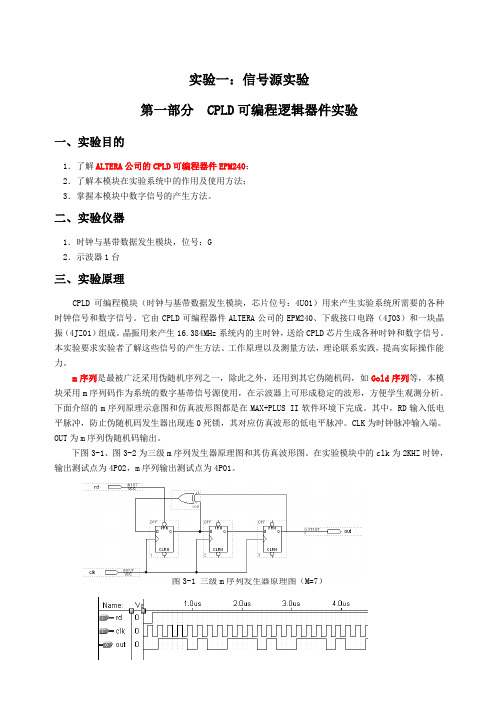

下图3-1、图3-2为三级m序列发生器原理图和其仿真波形图。

在实验模块中的clk为2KHZ时钟,输出测试点为4P02,m序列输出测试点为4P01。

图3-1 三级m序列发生器原理图(M=7)图3-2 三级m序列仿真波形图下图3-3、图3-4为四级m序列发生器原理图和其仿真波形图。

图3-3 四级m序列发生器原理图(M=15)下图3-5、图3-6为五级m序列发生器原理图和其仿真波形图。

图3-5 五级伪随机码发生器原理图图3-6 五级伪随机码仿真波形图图3-7中介绍是异步四级2分频电路,其特点是电路简单,但由于其后级触发器的触发脉冲要待前级触发器的状态翻转之后才能产生,因此其工作速率较低。

伪随机码产生器实验

实验八伪随机码产生器实验一、实验实训目的1.了解扩频通信的原理2.掌握伪随机序列——m序列产生器的结构二、实验原理与说明信号的频带宽度与其脉冲宽度近似成反比。

很窄的脉冲序列的带宽很宽,因此如果用很窄的脉冲序列对所传信息进行调制,则可产生很宽频带的信号。

CDMA 蜂窝网移动通信系统就是采用这种方式获得扩频信号的。

所用的这种很窄的脉冲码序列称为扩频码序列。

用很窄的脉冲序列对所传信息进行调制的一种方式就是直接序列扩频。

直接序列扩频系统采用的很窄的脉冲序列——伪随机码在发端对要发送的信息码进行频谱展宽——扩频,在收端用相同的伪随机码序列进行解扩,然后将展宽的扩频信号还原成原始信息。

作为扩频码的伪随机码具有类似白噪声的特性,可以用一种周期性的脉冲信号来近似随机噪声的性能,称之为伪随机码或PN码。

用于扩频码的伪随机码常用的m序列。

m序列容易产生、规律性强等优良特性,目前的CDMA系统就是采用这种PN 序列---m序列来进行扩频通信的。

m序列是最长线性移位寄存器的简称,m序列具有与伪随机噪声类似的尖锐自相关特性,但它不是真正随机的,而是按照一定规律周期性变化,它的周期P=2n-1。

n称之为m序列的阶数,也是构成m序列产程器所用移位寄存器的级数。

可以用硬件电路来实现一个m序列。

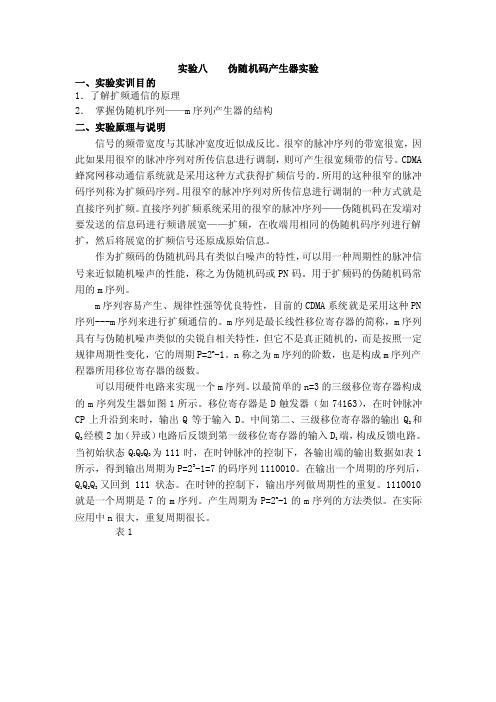

以最简单的n=3的三级移位寄存器构成的m序列发生器如图1所示。

移位寄存器是D触发器(如74163),在时钟脉冲CP上升沿到来时,输出Q等于输入D。

中间第二、三级移位寄存器的输出Q2和Q3经模2加(异或)电路后反馈到第一级移位寄存器的输入D1端,构成反馈电路。

当初始状态Q1Q2Q3为111时,在时钟脉冲的控制下,各输出端的输出数据如表1所示,得到输出周期为P=23-1=7的码序列1110010。

在输出一个周期的序列后,Q1Q2Q3又回到111状态。

在时钟的控制下,输出序列做周期性的重复。

1110010就是一个周期是7的m序列。

产生周期为P=2n-1的m序列的方法类似。

通信原理试验一 李马元

电子信息工程系实验报告课程名称:现代通信原理成绩:实验项目名称:实验一 HDB3码型变换实验实验时间:2012.5.14指导教师(签名):班级:电信092 姓名:李马元学号:910706203一、实验目的:1、理解二进制单极性码变换为AMI码的编码规则,掌握它的工作原理和实现方法;2、理解二进制单极性码变换为HDB3码的编码规则,掌握它的工作原理和实现方法。

二、实验环境:HDB3码型变换实验模块;伪随机码发生器及误码仪;直流稳压电源 JWY-30-4;双踪同步示波器SR8;高频Q表;频谱分析仪;三、实验原理:1、传输码型在传输线路上通常采用AMI码和HDB3码。

1)、AMI码我们用“0”和“1”代表传号和空号。

AMI码的编码规则是“0”码不变,“1”码则交替地转换为+1和-1。

当码序列是1 0 0 1 0 0 0 1 1 1 0 1时,AMI码就变为:+1 0 0 -1 0 0 0 +1 -1 +1 0 -1。

这种码型交替出现正、负极脉冲,所以没直流分量,低频分量也很少。

这种码的反变换也很容易,在再生信码时,只要将信号整流,即可将“-1”翻转为“+1”,恢复成单极性码。

这种码未能解决信码中经常出现的长连“0”的问题。

2)、HDB3码这是一种4连0取代码。

当没有4个以上连“0”码时,按AMI规则编码,当出现4个连“0”码时,以码型取代节“0 0 0 V”或“B 0 0 V”代替4连“0”码。

选用取代节的原则是:用B脉冲来保证任意两个相邻取代节的V脉冲间隔“1”的个数为奇数。

当相邻V 脉冲间“1”码数为奇数时,则用“0 0 0 V”取代,为偶数个数时就用“B 0 0 V”取代。

在V脉冲后面的“1”码和“B”码都依V脉冲的极性而正负交替改变。

为了讨论方便,我们不管“0”码,而把相邻的“1”码和取代节中的B码用B1 B2……Bn表示,Bn后面为V,选取“0 0 0 V”或“B 0 0 V”来满足Bn的n 为奇数。

专业实验类:伪随机信号发生器

H a r b i n I n s t i t u t e o f T e c h n o l o g yEDA技术高级应用实验报告姓名:禾小鬼同组人:学号:16S班级:信息2班指导教师:xxx院系:电信学院实验二伪随机信号发生器一、实验原理实验要求设计一个伪随机信号发生器,什么是伪随机信号发生器?如果一个序列,一方面它是可以预先确定的,并且是可以重复地生产和复制的;一方面它又具有某种随机序列的随机特性(即统计特性),我们便称这种序列为伪随机序列。

因此可以说,伪随机序列是具有某种随机特性的确定的序列。

它们是由移位寄存器产生确定序列,然而他们却具有某种随机序列的随机特性。

因为同样具有随机特性,无法从一个已经产生的序列的特性中判断是真随机序列还是伪随机序列,只能根据序列的产生办法来判断。

伪随机序列系列具有良好的随机性和接近于白噪声的相关函数,并且有预先的可确定性和可重复性。

这些特性使得伪随机序列得到了广泛的应用,特别是在CDMA系统中作为扩频码已成为CDMA技术中的关键问题。

特性为序列中两种元素出现的个数大致相等;如果把n个元素连续出现叫做一个长度为n的元素游程,则序列中长度为n的元素游程比长度为n+1的元素游程多一倍;序列有类似白噪声的自相关函数。

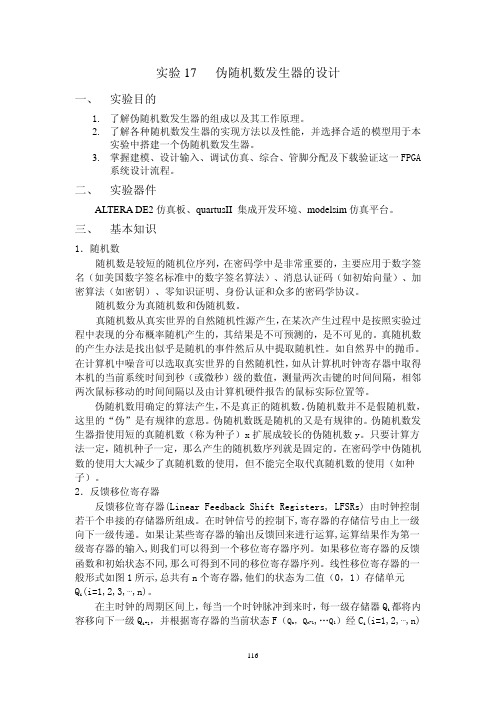

实验指导书上已经给出一个4位伪随机信号发生器的原理图,如图1所示,一个4位的移位寄存器,第1级和第4级的输出信号通过一个异或门反馈到第1级的输入。

随着连续的时钟周期信号,可以生成15个不同的测试向量。

图1 伪随机二进制序列产生器在开始之前,首先要明确设计目的,我们的想要用电路图方法实现设计一个“伪随机信号发生器”。

首先设计一个4位伪随机信号发生器,按照图1所示连接电路即可。

然后,扩展到多位。

二实验过程和结果1.第一步:建立一个新的工程新建工程的过程中,最重要的是设置器件,不同的器件的,设计之间并不兼容。

会有一个综合的信息框,注明了我所做的设置,看看没问题就可以了。

伪随机序列发生器

伪随机序列发生器一、实验目的:理解伪随机序列发生器的工作原理以及实现方法,掌握MATLAB\DSP BUILDER设计的基本步骤和方法。

二、实验条件:1. 安装WindowsXP系统的PC机;2. 安装QuartusII6.0 EDA软件;的序列发生器,并通⒈ ⒉ ⒊⒋⒌⒍⒎⒏⒐ ⒑ ⒒⒓⒔⒕⒖⒗四、实验原理:对于数字信号传输系统,传送的数字基带信号(一般是一个数字序列),由于载有信息,在时间上往往是不平均的(比如数字化的语音信号),对应的数字序列编码的特性,不利于数字信号的传输。

对此,可以通过对数字基带信号预先进行“随机化”(加扰)处理,使得信号频谱在通带内平均化,改善数字信号的传输;然后在接受端进行解扰操作,恢复到原来的信号。

伪随机序列广泛应用与这类加扰与解扰操作中。

我们下面用DSP BUILDER来构建一中伪随机序列发生器——m序列发生器,这是一种很常见的伪随机序列发生器,可以由线性反馈器件来产生,如下图:其特征多项式为:()∑==ni i i x C x F 0注:其中的乘法和加法运算都是模二运算,即逻辑与和逻辑或。

可以证明,对于一个n 次多项式,与其对应的随机序列的周期为。

12−n 接下来我们以为例,利用DSP BUILDER 构建这样一个伪随机序列发生器。

125++x x开Simulink 浏览器。

Simulink我们可以看到在Simulink 工作库中所安装的Altera DSP Builder 库。

2. 点击Simulink 的菜单File\New\Model 菜单项,新建一个空的模型文件。

3. 按照下图在Model编辑器的工作区中放置如下的模型:其中Logical Bit Operator模块在Gate & Control库中,把它拖到工作区中后双击打开参数设置对话框,设置成2输入异或门。

为了能够在Matlab中获得仿真结果,可以给输出再添加一个示波器Scope,这个模型在Simulink标准库的Sources库中。

17伪随机数发生器的设计

119

原胞自动机伪随机数发生器同样是通过寄存器的延时来实现。每当一个时钟 脉冲到来时,每一级存储器 Qi 的值根据 CA 规则来决定,CA90 和 CA150(即 CA01011010B 和 CA10010110B)算法规则的规则查找表分别如表 1,2 所示,其中相 邻单元的值为η,输出值为 Q=f(η)。CA90 算法规则等价的逻辑函数是由当前单 元的相邻左右单元的状态值相异或,而 CA150 算法规则等价的逻辑函数是由相邻 当前单元和左右单元的状态值相异或。下面分别给出它们的逻辑函数表达式。

3.原胞自动机 一个原胞自动机(Cellular Automata,CA)是一种有限状态机,有 n 个离散

的单元,每个单元以离散的节拍进化,其中每个单元的下一个状态值由该单元的 当前状态值和其相邻的当前状态值通过查找表(Look-UpTable,LUT)(或等价的逻 辑函数)来决定,而相邻单元的状态值是独立的。

Cn

Cn-1

Cn-2

C1

C0=1

图 1 传统多级线性移位寄存器结构

3.m 序列 m 序列(maximum-length)是一类最大长度线性移位寄存器序列的简称。 m

序列是目前广泛应用的一种伪随机序列,其在通信领域有着广泛的应用,如扩频 通信,卫星通信的码分多址,数字数据中的加密、加扰、同步、误码率测量等领 域。

表 1 CA90 规则查找表

η 111 110 101 100 011 010 001 000

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一 伪随机码发生器实验

一、实验目的

1、 掌握伪随机码的特性。

2、 掌握不同周期伪随机码设计。

3、 用基本元件库和74LS系列元件库设计伪随机码。

4、 了解ALTERA公司大规模可编程逻辑器件EPM7128SLC84内部结构和应用。

5、 学习FPGA开发软件MAXPLUSⅡ,学习开发系统软件中的各种元件库应用。

6、 熟悉通信原理实验板的结构。

二、实验仪器

1、 计算机 一台

2、 通信基础实验箱 一台

3、 100MHz 示波器 一台

三、实验原理

伪随机码是数字通信中重要信码之一,常作为数字通信中的基带信号源;扰码;误码测试;扩频通信;保密通信等领域。

伪随机码的特性包括四个方面:

1、 由n 级移位寄存器产生的伪随机序列,其周期为-1; n 2

2、 信码中“0”、“1” 出现次数大致相等,“1”码只比“0”码多一个;

3、 在周期内共有-1游程,长度为 i 的游程出现次数比长度为 i+1的 游程出现

次数多一倍;

n 24、 具有类似白噪声的自相关函数,其自相关函数为:

()()

⎩⎨

⎧

−≤≤=−−=2

210

12/11n n

τττρ

其中n 是伪随机序列的寄存器级数。

例如:四级伪码产生的本原多项式为X 4+X 3+1。

利用这个本原多项式构成的4级伪随机序列发生器产生的序列为:

1 1 1 1 0 0 0 1 0 0 1 1 0 1 0

相应的波形图如图1-1所示:

图1-1 四级伪随机序列波形图

用4个D 触发器和一个异或门构成的伪码发生器具有以下特性: 1、 周期为24-1=15;

2、 在周期内“0”出现24 -1-1=7次,“1”出现24 -1=8次;

3、 周期内共有24 -1 =8个游程;

4、 具有双值自相关特性,其自相关系数为:

⎩⎨⎧−≤≤−−==2

21)12(10

14

4τ / τ ρ(τ)

四、实验内容及步骤

1、在MAXPLUSⅡ设计平台下进行电路设计 1.1 四级伪随机码发生器电路设计

电路原理图如图1-2所示。

图1-2 四级伪随机码电路原理图

在MAXPLUS II 环境下输入上述电路,其中: dff ------ 单D触发器 xor ------ 二输入异或门 nor4 ------ 四输入或非门 not ------ 反相器

clk ------ 时钟输入引脚(16M时钟输入) 8M ------ 二分频输出测试点引脚 nrz ------ 伪随机码输出引脚 1.2 实验电路编译及FPGA 引脚定义

完成原理图输入后按以下步骤进行编译:

(1) 在Assign Device 菜单选择器件MAX7128SLC84。

(2)在Assign/Globl project device option菜单中选择 Enable JTAG

Support。

(3)第一次编译时一般采用让MaxplusII自动进行引脚分配。

注意,编译前

一定要确保所编译的文件是一个工程。

具体做法是:在菜单

File/Project下点击Set Project to Current File。

(4)编译后进行引脚回注,在Assign/Back-Annotate Projetc菜单中选择

Chip,Pin&Device,经过引脚回注后电路图上会显示自动分配的引脚

号。

(5)按照实验板所要求的输入时钟引脚和输出测试引脚号,进行引脚修

改,修改后必须编译,所做的修改才会生效。

引脚修改方法如下:双

击clk时钟输入引脚元件中的回注引脚号,MAXPLUS II会弹出一对话

框,可方便进行修改。

如图1-3所示。

图1-3 引脚修改界面

将电路图中所有引脚修改成实验板要求的引脚,然后再次进行编译。

要求的引脚配置如下:

CLK 83 脚 (CLK输入频率为16.9M,或经过2分频率后为8.46M)

8M 37 脚 (8M时钟输出)

NRZ 39 脚 (NRZ称不归零码,这时码率为8.46Mb/s)

NNRZ 40 脚 (反相输出)

1.3 在MAXPLUSⅡ环境下完成电路的仿真

(1)在MAX+plu sⅡ菜单下选择Waveform Editor,出现一波形编辑窗口。

波形编辑窗

口

(2)在Node菜单下选择Enter nodes from SNF,点击List,加入要仿真的所

有节点。

加入仿真节点

(3)加入时钟激励:在Option菜单下选Grid Size,出现对话框后键入相应

的纳秒(ns)数,例如10ns(对应周期为20ns,即50M)。

在File菜单下选End Time,键入仿真时间,例如10us。

选择输入时

钟信号clk 选择此图标

给时钟赋值

(4)在MUXPLU SⅡ菜单下选Simulator,出现仿真对话框后,点击

Start,开始仿真。

注意:进行仿真前一定要先保存。

得到的仿真波形和理论结果是一致的。

2、实验板设置

在进行不同实验时,首先要对实验板上硬件进行简单设置,以符合各种信号输入和各种实验结果测试要求。

(见跳线和开关设置表)

硬件实验步骤为:接通晶体振荡器电源----》将16.9M时钟连接到FPGA全局时钟脚----》将实验电路配置到FPGA芯片中----》进行实验测量。

实验原理图如图1-4所示:

FPGA内部T16 T17 T15

T8

FPGA83脚

图1-4 实验原理图

(1)接通SW_6(用短路块),晶体振荡器X1产生16.9344M时钟信号,T8为

该时钟频率的测试点。

(2)将拨动开关“K2”的“1”脚置“ON”,将16.9344Mc时钟信号送到了

FPGA第83脚(全局时钟脚)。

(3)将8.5V直流电源插入实验板PJ1接口,打开总开关K1,检查指示灯P1、

P2、P3是否亮,即电源工作正常。

实验板跳线和开关设置表:

3、将实验电路nrz.pof文件配置到FPGA芯片

(1) 将BYTBLASTER一端连接到计算机并行口,另一端连接到实验板BYTBLASTER口。

(2) 打开电源开关K1,注意SW_13为FPGA电源跳线,应接通。

(3) 在MAXPLUSⅡ菜单下选Programmer然后按Program开始下载。

4、实验测试

下载成功后,可用示波器测试各点波形(见照片)。

NRZ码实验测试点表

测试点名称测试点波形说 明

T8 16.9MC 晶体振荡器输出

T5 16.9MC 时钟选择开关输出

T15 8.45MC 二分频输出时钟信号

T16 NRZ码

T17 反相NRZ码

(1)先用示波器测T8(或T5)为 16.9M晶体振荡器输出时钟。

用20M示波器测试T8波形

(2)用示波器测T15为 8.4M输出时钟信号。

8M 时钟波形(用20M示波器测试T15)

(3)用示波器测T16为 NRZ输出信号

8Mb/S NRZ 码输出波形

注意:一般示波器只能观察到4级或5级伪随机码,对于更多级伪随机码由于普通示波器较难同步,很难看到完整信码序列,这时可以用MAXPLUSⅡ仿真器观察仿真波形 ,或用数字示波器观察伪随机码波形。

当伪码长度很长时示波器不能完全同步

五、实验报告内容要求

1、实验原理叙述

2、画出实验电路图

3、电路仿真结果记录和分析

4、实际测量数据记录,并结合理论进行分析

附录:

1、各级伪随机码(M序列)发生器反馈逻辑表

表1-1各种伪随机码发生器的反馈逻辑表

2、各级伪随机码发生器实验电路图

4级伪随机码电路

5级伪随机码电路

6级伪随机码电路

15级伪随机码电路

23级伪随机码电路。