跨导运算放大器及其Spice电路模型的构建

spice和spectre软件使用和运放的仿真方法

斜坡上升 阶跃信号

激励

3.脉冲信号源 V1 N1 N2 PULSE(v1 v2 td tr tf pw per)

V1 N1 N2 PULSE(0 5 1p 1p 1p 5u 10u) 注:v1:值1

v2:值2 td:延迟时间 tr:上升时间 tf:下降时间 pw:脉冲宽度 per:周期

方波

激励

4.正弦信号源 V1 N1 N2 SIN(v0 va freq td θ Φ) V1 N1 N2 SIN(0 1 1) 注:v0:偏置值

基本语法

1. 不区分大小写(case insensitive) 2. 注释:* or $ 3. 数量级表示符号:

T

E12

G

E9

MEG

E6

K

E3

M

E-3

U

E-6

N

E-9

p

E-12

F

E-15

(关键不要搞错M和MEG) 4.赋值单位可以省略

仿真网表的五个主要组成部分

1.电路网表 2.激励 3.仿真分析语句 4.输出命令 5.模型库文件

添加模型时,添加此库文件,section选项只填上tt就可以了!

Hspice模型文件的结构(.lib)

**说明** .lib tt ……参数 .lib “路径/模型名.lib” mos .lib “路径/模型名.lib” bjt .lib “路径/模型名.lib” diode .endl tt ……(包括.lib ss,.lib sf,.lib fs,.lib ff等)

电路网表

包含的内容有器件连接关系、模型名、参 数值、(赋值)、并联个数、(初始值) 例: R1 N1 N2 R W=10u L=1u R2 N1 N2 10K C1 N1 N2 C W=10u L=1u C2 N1 N2 10p C3 N1 N2 10p IC=1

跨导运算放大器设计实例

李福乐 lifule@

1

Specifications

• CSMC 0.6um DPDM CMOS Process • GBW > 100MHz, PM > 60 when CL=2pF • DC Gain > 80dB • Output swing > 4V (differential) • Full differential architecture • Low Power (Large FOM)

所设计的OTA要应用于课程设计10bit cyclic ADC中。 在开关电容ADC中,ADC的速度取决于级电路的建立速度,而级电路的建立过程 可视为由大信号压摆区和小信号线性建立区构成,其中,小信号建立区的时间通 常要占到总建立时间的80%~90%,因此,OTA的大信号压摆率对ADC的速度影响 较小; 从另一个方面来说,压摆率只取决于偏置电Байду номын сангаас,当偏置电流和电容确定后,无论 输入管的VGS-VT是大是小,压摆率都不变。对于连续信号处理电路,我们希望 OTA在整个设计带宽内工作时,输出信号不会因为摆率跟不上而幅度受限,这个 时候需要SR/GBW大一些,即输入管的VGS-VT大一些;但是,对于采样信号处理 电路,比如我们所要设计的ADC,当我们确定好偏置电流,然后降低输入管的 VGS-VT,这个时候,SR不变,GBW变大,即SR/GBW变小了,而最终的建立时 间反而缩小了,ADC的速度加快了。 因此,SPEC中没有提出对SR的具体要求。 注意:不同应用对SR/GBW的不同要求!

3

MOST parameters

• u? Cox?

– Find out un, up, toxn and toxp from model library

(完整word版)跨导运算放大器的设计

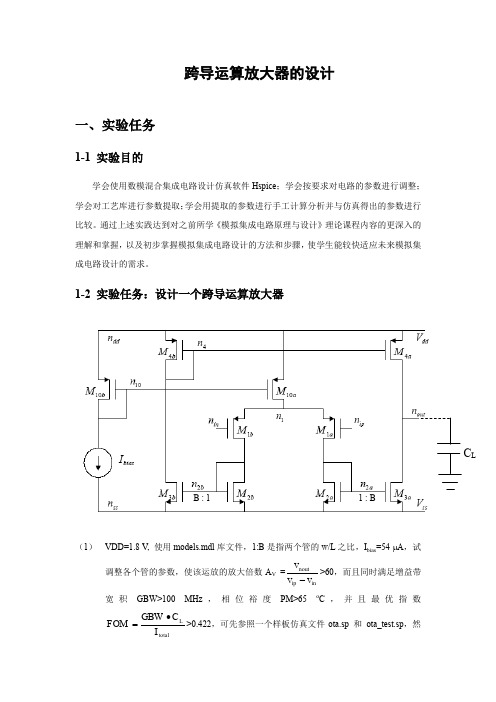

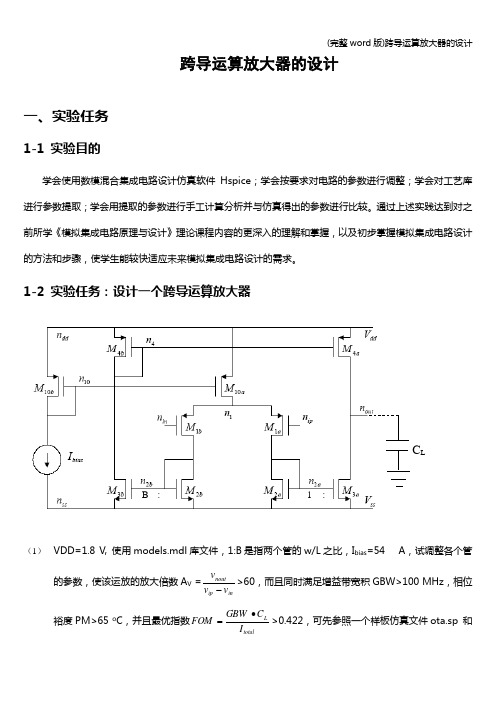

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 oC ,并且最优指数totalLI C GBW FOM ∙=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

(完整word版)跨导运算放大器的设计

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V, 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54A ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 o C ,并且最优指数totalLI C GBW FOM •=>0.422,可先参照一个样板仿真文件ota.sp 和C LB : 1 1 : Bota_test.sp ,然后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较;(3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少?最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

SiC MOSFET SPICE模型的建立与仿真分析

SiC MOSFET SPICE模型的建立与仿真分析叶雪荣;张开新;翟国富;丁新【摘要】SiC MOSFET与Si MOSFET相比,具有耐高压、耐高温、频率快等诸多优点,得到了越来越广泛的应用。

SPICE模型作为含SiC MOSFET电路仿真分析的基础,对其进行研究十分必要。

以SPICE 1模型为例,介绍了基于LTspice的SiC MOSFET建模流程,通过MOS、体二极管、PCB寄生参数等建模过程,完成了SiC MOSFET SPICE 1模型的建立,并通过仿真分析验证了所建立模型的正确性。

【期刊名称】《电器与能效管理技术》【年(卷),期】2019(000)003【总页数】6页(P25-29)【关键词】SiC MOSFET;SPICE 1模型;仿真;LTspice【作者】叶雪荣;张开新;翟国富;丁新【作者单位】[1]哈尔滨工业大学电器与电子可靠性研究所,黑龙江哈尔滨150001;[1]哈尔滨工业大学电器与电子可靠性研究所,黑龙江哈尔滨150001;[1]哈尔滨工业大学电器与电子可靠性研究所,黑龙江哈尔滨150001;[2]航天安通电子科技有限公司,天津300384;【正文语种】中文【中图分类】TM460 引言作为电力电子变换装置系统的核心组件、电力电子变换技术的基础,半导体技术的发展一直是推动电力电子技术发展的关键[1]。

随着SiC材料的发展,其在高压[2-3]、高温[4-5]、大功率[6]、高频[7-8]等应用场合下具有明显的优势,越来越受到研究者的青睐。

国内外学者对于SiC MOSFET建模的方法做了大量研究。

国外学者对于模型的研究主要分为物理建模和等效电路建模,如文献[9]基于SiC器件的物理特性、物理结构提出一种模型,但其不适用于工程中的应用和分析。

部分文献通过改进传统的Si MOSFET模型进行建模,文献[10]提出了一种变温度参数建模方法,非常适用于高压SiC MOSFET。

此方法对SiC MOSFET的建模具有一定的指导意义,已得到业界普遍的认可。

第5章集成电路元器件及其SPICE模型ppt课件

金属叉指结构电容

优点:不需要额 外的工艺。

特征尺寸急剧降 低,金属线条的 宽度和厚度之比 大大减小,叉指 的侧面电容占主 导地位。

PN结电容

❖ 利用PN结电容的优点也是不需要额外的工艺,但所 实现的电容有一个极性问题。

❖耗尽区

❖反型区

G

Co 沟道 Cdep

Vss

G ++++++

沟道 耗尽层 P型衬底

Vss

(a)物理结构

tox d

Cgb Co 积累区

耗尽区

1.0

反型区

(b)电容与Vgs的函数关系 0.2

0

Vgs

三、集成电感

在集成电路开始出现以后很长一段时间内, 人们一直认为电感是不能集成在芯片上的。因 为那时集成电路工作的最高频率在兆赫量级, 芯片上金属线的电感效应非常小。现在的情况 就不同了,首先,近二十年来集成电路的速度 越来越高,射频集成电路(RFIC)已经有了很 大的发展,芯片上金属结构的电感效应变得越 来越明显。芯片电感的实现成为可能。

在设计电路的时候需要非常准确地 预测出电路的性能。为了做到这一点, 需要对电路尽可能地进行精确的性能分 析(Analysis)。因为集成电路元器件 无法用实物构建,必须首先建立器件模 型,然后对用这些元器件模型所设计的 集成电路进行以分析计算为基础的电路 仿真(Simulation)。

在集成电路的晶体管级仿真方面, SPICE是主要的电路仿真程序,并已成为 工业标准。因此,集成电路设计工程师, 特别是模拟和数字混合信号集成电路设计 工程师必须掌握SPICE的应用。

恒跨导高摆率轨对轨运算放大器的设计

恒跨导高摆率轨对轨运算放大器的设计张伟娟;邹伟;徐坤玉【摘要】本文在分析MOS管恒跨导输入级和AB类输出级运算放大器的基础上设计了一个高摆率、恒跨导的轨对轨运算放大器。

在输入级中采用了齐纳二极管的稳压原理,保证Rail-to-Rail运算放大器的输入跨导恒定。

为了实现高转换率,本文采用了一种新型的压摆率提高电路。

另外,为了提高系统的稳定性,采用了控制零点的米勒补偿进行频率补偿。

采用CSMC 0.5 μm CMOS工艺,用H-Spice对整个运算放大器电路进行仿真验证,结果表明运算放大器输入输出范围基本达到满摆幅,最大跨导变化率仅为3.9%和具有较高的增益和摆率。

%Based on analyzing MOS transistor constant-gm input stage and class AB output of operational amplifier, a high-slew-rate and constant-gm, rail-to-rail operational amplifier was designed. A Zener-diode structure was inserted in the input stage to keep the gm of the input stage constant. A novel slew rate enhancement circuit was implemented to achieve a high slew rate. In addition, the miller compensation was adopted to improve the stability of the system. The circuit was realized in CSMC 0.5 μm CMOS process and is simulated by H-Spice for whole of operational amplifier. The simulated results showed that the operational amplifier has rail-to-rail input and output and the maximum gm fluctuation is only 3.9%. It has quality of high gain and rate.【期刊名称】《电子测试》【年(卷),期】2011(000)011【总页数】4页(P58-61)【关键词】恒跨导;轨对轨运算放大器;摆率【作者】张伟娟;邹伟;徐坤玉【作者单位】兰州交通大学电子与信息工程学院,甘肃兰州730070;兰州交通大学电子与信息工程学院,甘肃兰州730070;兰州交通大学电子与信息工程学院,甘肃兰州730070【正文语种】中文【中图分类】TN4320 引言运算放大器是集成电路中应用最广泛的电路单元之一,它是模拟及数模混合电路中的一个重要模块。

第八讲 跨导运放的分析与设计讲解

由于零点的作用,相位裕度 从60多度减小至39度!

交流扫描

Ota simulation

.prot

.lib ‘LIB_PATH\csmc.lib’ tt

.unprot

.option post probe

分析miller补偿效应

.probe ac v(vo1) v(vo) vp(vo)

.op

*.dc v_vdc 2.48 2.495 0.0001

失调分析

在MOS晶体管的参数中考虑失配 例:原有的 W=12u, M=2 修改为 W=‘12u+12u*0.04u*alfa/sqrt(2*12um*5um)’ M=2 delvto=‘12.5n*alfa/sqrt(2*12um*5um)’ 这里alfa为(0,1)高斯分布变量 依次将网表的内容按照上面的方法修改

.lib ‘LIB_PATH\csmc.lib’ tt

.unprot

.option post probe

.probe dc v(vo1) v(vo)

.op .dc v_vdc 2.48 2.495 0.0001

精扫

*.trans 10ns 200ns 20ns 0.1ns

*.ac dec 10 1k 100meg $sweep rzv 0 2k 0.2k

耗,因此可查得电路功耗为2.47mW • 对于MOS管,注意各参量的含义:region、id、vgs、

vds、vth、vdsat、gm、gmb、gds……可查得流过 M_U3的偏置电流为149.8uA,并注意到M_M3的 region为Linear

直流扫描

Ota simulation

.prot

.lib ‘LIB_PATH\csmc.lib’ tt

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2.1 CMOS模拟集成电路基本单元2.1.1 MOS场效应管的基本结构绝缘栅场效应管又叫作MOS场效应管,意为金属-氧化物-半导体场效应管。

图2.1为MOS场效应管的结构和电路符号。

图中的N型硅衬底是杂质浓度低的N型硅薄片。

在它上面再制作两个相距很近的P区,分别引为漏极和源极,而由金属铝构成的栅极则是通过二氧化硅绝缘层与N型衬底及P型区隔离。

这也是绝缘栅MOS场效应管名称的由来。

因为栅极与其它电极隔离,所以栅极是利用感应电荷的多少来改变导电沟道去控制漏源电流的。

MOS场效应管的导电沟道由半导体表面场效应形成。

栅极加有负电压,而N型衬底加有正电压。

由于铝栅极和N型衬底间电场的作用,使绝缘层下面的N型衬底表面的电子被排斥,而带正电的空穴被吸引到表面上来。

于是在N型衬底的表面薄层形成空穴型号的P型层,称为反型层,它把漏源两极的P区连接起来,构成漏源间的导电沟道。

沟道的宽窄由电场强弱控制。

MOS场效应管的栅极与源极绝缘,基本不存在栅极电流,输入电阻非常高。

[20,21]图2.1MOS场效应管的结构和电路符号Fig.2.1 Structure and circuit symbol that MOS Field-Effect Transistor 场效应管有P型和N型之分。

这里的P型或N型,指的是导电沟道是P型还是N 型,即导电沟道中是空穴导电还是电子导电。

因为场效应管中只有一种载流子参加导电,所以又常称为“单极型晶体管”。

P型沟道和N型沟道的MOS场效应管又各分为“耗尽型”和“增强型”两种。

耗尽型指栅极电压为零时,就存在导电沟道,漏源中间有一定电流。

增强型MOS场效应管,则只有在栅极电压大于零的情况下,才存在导电沟道。

2.1.2 MOS场效应管的模型化MOS管的大信号(直流)特性可以用它的电流方程来描述。

以N沟道增强型MOS管为例,特性曲线和电流方程如图2.2所示。

图2.2 特性曲线和电流方程Fig.2.2 Characteristic property curve and electric current equation如果栅源偏置电压GS V 大于MOS 管的阈值电压T V ,则在P 型衬底的表面由于静电感应会产生大量的电子,形成导电沟道。

当漏区相对于源区加一正电压DS V 时,在器件内部的沟道中就会产生电流D I 。

MOS 管的工作状态可分为三个区,即电阻区(线性区)、饱和区和截止区。

(1)截止区: V GS <V T 。

此时不能产生导电沟道,漏极电流I D =0。

(2)电阻区:V GS >V T 且V DS <V GS -V T 。

])(2[2'2DS DS T GS D V V V V LW K I --= (2.1) 其中,W 是沟道宽度,L 是沟道长度,V T 阈值电压,0'C K μ=称为跨导参数,μ是载流子的沟道迁移率,0C 是单位电容的栅电容。

(3)饱和区:V GS >V T 且V DS >V GS -V T 。

临界饱和条件为V DS =V GS -V T ,临界饱和时的漏极电流为:2'()2D GS T K W I V V L=- (2.2) 在饱和区,V DS 增大时,I D 几乎不变,所以上式也是饱和区的漏极电流一般公式。

当考虑到沟道长度调变效应之后,饱和区的MOS 管漏极电流为:2'()(1)2D GS T DS K W I V V V Lλ=-+ (2.3)其中,λ为沟道长度调制系数,对于长度为L 的MOS 管,其大信号特性可近似认为λ是常数,并只取决于生产工艺,而与D I 无关。

[22,23]MOS 场效应管的小信号模型输入信号的幅度与电源电压相比较一般很小,它在直流偏置工作点附近变化时,可以近似认为器件工作在线性区间。

大信号特性可以确定器件的直流工作点,小信号特性可以用来设计器件和电路的性能。

MOS 管的小信号模型可以直接由直流模型得出。

在大多数应用中,MOS 管被偏置在饱和区工作,考虑到栅源、栅漏及漏源之间的寄生电容,MOS 管的饱和区小信号模型如图2.3所示。

GSD m V I g ∂∂= (2.4) 式中, m g 为跨导,表征输入电压对输出电流的控制能力。

对于在饱和区工作的模型参数,应用式2.2和2.4得:D m I LW K g '2= (2.5) 其中,D I 是漏极的直流电流。

G图2.3 小信号模型Fig.2.3 S mall signal model当电路在低频工作时可以不考虑这些寄生电容的影响,此时的小信号等效电路如图2.4所示。

图2.4不考虑电容影响的小信号等效电路Fig.2.4 Small signal equivalent circuit that do’t consider capacitance affects2.1.3 CMOS 电流镜电流镜是模拟集成电路中普遍存在的一种标准部件,在传统的电压模式运算放大器设计中,电流镜用来产生偏置电流和作为有源负载。

基本CMOS 电流镜IR VSSIO IR(a)基本NMOS 电流镜 (b )基本PMOS 电流镜图2.5 基本CMOS 电流镜Fig.2.5 Fundamental CMOS electric current mirror基本CMOS 电流镜如图2.5所示,其中图(a)为NMOS 电流镜,图(b)为PMOS 电流镜。

在图(a)中,M 1的栅源短接,V DSI >V GS - V TI ,所以M l 总工作于饱和区。

只要V DS2>V DS1-V T2,M 2也工作于饱和区,漏极的交流输出电阻很高,这是图(a)作为电流镜的必要条件。

在这个条件下,由式2.3,有:)1()(2'22222222DS T GS O V V V L W K I λ+-= (2.6) )1()(2'11211111DS T GS R V V V L W K I λ+-= (2.7) 如果Ml 与M2完全匹配,有''21'K K =,V T1=V T2,,λ1=λ2 =λ,则:212121(1)(1)O DS R DS I W L V I W L V λλ+=+ (2.8) 对于基本CMOS 电流镜,由于沟道长度调制效应的影响,当MOS 管的漏源电压不等时,会引起电流镜电流跟随误差。

但由于λ很小,所以误差也很小。

CMOS 级联电流镜VSSIO IR(a)NMOS 级联电流镜 (b)PMOS 级联电流镜图2.6 CMOS 级联电流镜 Fig.2.6 CMOS level unites the voltaic mirror图2.6为级联电流镜电路图。

图中M 1与M 3级联,M 2与M 4级联。

图2.6(a)为NMOS 级联电流镜,图2.6(b)为PMOS 级联电流镜。

在图2.6中,有I O =I D2,I R =I D1 ,V GS1=V GS2,由式2.3得:)1(')1('1121122122DS DS R O V L W K V L W K I I λλ++= (2.9) 因为M 1与M 3级联,I D1=I D3,又V DS1=V GS1,V DS3=V GS3,那么当M1与M3的工艺参数相同时,由饱和区漏极电流表达式可知:V GS1=V GS3 。

M2与M4级联,有I D2=I D4,由饱和区漏极电流表达式可知:V GS2=V GS4。

对于V DS1、V DS2,有V DS1=V GS1,V DS2=V GS3-V GS4+V GS1 ,又V GS1=V GS2,可得:V DS1=V DS2 。

如果M 1、M 2的工艺参数相等,那么可得:2112O R I W L I W L = (2.10) 当1122L W L W =时,有: R O I I = (2.11)由于级联电流镜的漏源电压基本相等,其电流跟随特性较好,跟随精度较高。

2.1.4 基本源耦差分对电路的跨导分析源耦合差分放大器在模拟集成电路中有着广泛的应用,如集成运放的输入级均采用差分放大器的电路结构[24]。

这是因为差分放大器只对差分信号进行放大,而对共模信号可进行抑制,有很强的抗干扰能力,并具有漂移小、级与级间很容易直接耦合等优点。

如图2.7所示为一个基本的MOS 源耦合差分对管电路。

图中的M1、M2是完全对称的,其工作电流(IDI 、ID2)由电流源Iss 提供。

输出电流ID1、ID2的大小依赖于输入电压的差值(Vi1-Vi2),但ID1和ID2之和恒等于电流源Iss ,在M1和M2的漏极分别接上电阻负载或MOS 管有源负载,即构成差分放大器,由电流输出转换成电压输出,实现电压放大。

Vi1Vi2V-图2.7 基本源耦合差分放大器电路Fig.2.7 Fundamental source coupling differences amplifiers circuitMOS 管M1和M2满足理想对称条件,其体效应和沟道长度调制效应均可忽略,并且始终工作在饱和区,则根据MOS 管在饱和区的电流方程式有:211)(T G S D V V K I -⋅= (2.12)222)(T G S D V V K I -⋅= (2.13)式中,LW K K 2'= 差模输入电压为:KI K I V V V D D GS GS id 2121+=-= (2.14) 又:SS D D I I I =+21 (2.15) 则联立可得:21212221id SS SS idSS D V I K KI V I I -+= (2.16) 22212221id SS SS idSS D V I K KI V I I --= (2.17) 从而得到源耦合差分对的输出电流为:221212id SSid SS D D O V I K V I K I I I -⋅⋅⋅=-= (2.18) 跨导: SS idSS id SS id O m I V K I V K I K V I g 21)1(222⋅-⋅-⋅=∂∂= (2.19)上式表明,CMOS 源耦差分放大器的跨导与Iss 的平方根成正比,同时也与K 的平方根成正比,可通过调节偏置电流或差分对管沟道宽长比W/L 来调节跨导的数值。

2.2 MOS-OTA 基本电路模型及工作原理跨导运算放大器,简称OTA (Operational Transconductance Amplifier ),是一种电压输入、电流输出的电子放大器,可分为双极型和MOS 型两种,它们的功能在本质上是相同的,都是线性电压控制电流源。

但是,由于集成工艺和电路设计的不同,产生它们在性能上的一些不同,相对双极型跨导运算放大器而言,CMOS 跨导运算放大器的增益值较低,增益可调范围较小,但它的输入阻抗高、功耗低,易与其他电路结合实现CMOS 集成系统。