Xilinx展望7系列:FPGA给力高密度和高收发

Xilinx Kintex-7系列FPGA高速采集卡中文资料

Xilinx Kintex-7系列FPGA高速采集卡中文资料基于Xilinx Kintex-7 FPGA,XC7K160/325/410T FBV676可选,DDR3 256MB/512MB可选,NOR FLASH 256Mb,可根据开发需求自由搭配,成本可控;工业级FMC连接器,支持高速ADC和DAC等FMC标准模块;PCI Express 2.0标准,提供PCIe x2高速数据传输接口,单通道通信速率可高达5GBaud; Serial Rapid I/O,提供SRIO x2高速数据传输接口,单通道通信速率可高达5GBaud; SFP+光纤接口,传输速率可高达10Gbit/s;集成千兆网及I2C等常见接口,拓展能力强;提供板卡原理图和丰富的开发例程,入门简单。

图 1 Xilinx Kintex-7 FPGA基本参数图 2 TL-K7FMC采集卡正面图图 3 TL-K7FMC采集卡侧视图1图 4 TL-K7FMC采集卡侧视图2图 5 TL-K7FMC采集卡侧视图3图 6 TL-K7FMC采集卡侧视图4TL-K7FMC采集卡是一款由广州创龙基于Xilinx Kintex-7系列FPGA自主研发的FMC数据采集卡,可配套广州创龙TMS320C6655、TMS320C6657、TMS320C6678开发板使用。

TL-K7FMC采集卡完全支持PCI Express 2.0标准,串行高速输入输出SRIO总线通过HDMI接口提供稳定、可靠的高速传输能力,为产品的快速成型提供极大的便利。

TL-K7FMC 采集卡的FMC接口不仅简化了I/O接口模块设计,提供高速的接口通信能力,而且提高了模块的利用率,标准化设计使产品有更好的通用性。

1 典型运用领域✓ 高速数据采集系统 ✓ 音视频数据处理系统 ✓ 图像处理设备 ✓ 软件无线电设备 ✓ 通信系统 ✓ 高精度仪器仪表 ✓ 高端数控系统2 软硬件参数硬件参数Kintex-7Xilinx® 7 series28nm Technology Low Cost FPGAKintex-XADCCDCM 61002DDR3SPI FLASHEEPROM AT24C02UARTJTAGOSC 25MHzPHYASP-134488-01400PIN ArrayRESETLED710-1100-304848PIN 2.54mmPCIE GEN2 x4Serial Rapid IOx2SFP+图 7 TL-K7FMC 采集卡硬件框图图8 TL-K7FMC硬件资源图解1图9 TL-K7FMC硬件资源图解2表1CPU Xilinx Kintex-7 FPGA,XC7K160/325/410T FBV676 RAM 256MByte/512MByte DDR3ROM 256MBit NOR FLASHEEPROM 2KBit网络10/100/1000M ETHERNET光纤接口1x SFP+LED1x 供电指示灯3x 可编程指示灯按键1x 复位按键2x 用户可编程按键拓展IO 1x SRIO TX,1x SRIO RX,2通道,单通道最高速率5GBaud,HDMI座1x PCIe 4x(Gen2),2通道,单通道最高通信速率5GBaud2x 48pin欧式连接器,GPIO拓展1x I2C,HDMI座1x PMOD1x XADC1x FMC,400pin仿真器接口1x 14pin JTAG接口,间距2.00mm启动方式1x 2bit启动方式选择拨码开关串口1x UART,Micro USB接口,提供4针TTL电平测试端口电源开关1x 电源拨码开关电源接口1x 12V 2A直流输入DC005电源接口,外径5.5mm,内径2.1mm 软件参数表 2Vivado版本号2015.23开发资料●提供采集卡原理图、入门教程、丰富的Demo程序;●提供与DSP通信教程,完美解决DSP+FPGA异构平台通信开发瓶颈;●提供完整的软件开发包,以及配套的开发文档。

Xilinx 7系列GTX具体的调试步骤

Xilinx 7系列GTX具体的调试步骤随着需求的多样化,FPGA的功能也进一步的增强。

其中,高速收发器从本来是只有高端FPGA才有的模块,已经变为相对普及的甚至必备的功能模块。

而10G的线速率也从多年前的少数FPGA支持,变为目前的主流线速率。

由于FPGA的最大特点就是灵活,所以FPGA的高速收发器也拥有非常繁琐的配置选项,目的就是为了灵活地支持各种传输协议。

之所以称之为繁琐,就是灵活性带来的弊端,即想要理清楚诸多的功能,就需要非常多时间在高速收发器上。

不过对于大部分的用户来说,需要使用高速收发器的接口通常是相对固定的,这样功能也就相对固定。

这样就没有必要理解高速收发器全部的功能,只要理解需要使用的配置含义即可。

这样可以快速进行尝试/测试,在尝试/测试过程中结合文档进行深入理解。

这样比强行读完文档再动手实践,学习效果上有可能更好。

所以Xilinx的高速收发器中默认就带了一些常用接口的配置,便于用户的学习/使用。

Xilinx 7系列FPGA芯片配置四种高速收发器,按照支持的最高线速率从低到高排列分别是GTP,GTX,GTH,GTZ。

GTP由于结构问题,使用起来灵活性较差,同时支持的最高线速率也只有6.x个G。

GTZ 属于7系列中最高端的高速收发器,集成GTZ的FPGA很少,同时也是用了多die技术,物理上和FPGA主体是两个部分。

对这两种GT,本文不做更多的介绍。

与GTX相比,GTH整体结构几乎一样,只是在个别细节有更多的配置或者更强大的性能。

考虑到文档都是同一篇文档,所以本文以GTX为例。

本文所有内容,除非特别注明,都同时适用于GTX和GTH。

对于高速收发器GTX来说,虽然可以通过IP中的默认配置来进行初步的学习,而且有一定基础之后,可以手动配置GTX参数。

但是如果不充分理解GTX的各个功能,最常见的被卡住的地方,就是不能/不知道如何进行正确的问题定位。

所以文本的主题就是介绍一些常用的调试手段和步骤,便于使用者初步定位问题。

Xilinx 7系列开发板性能比较

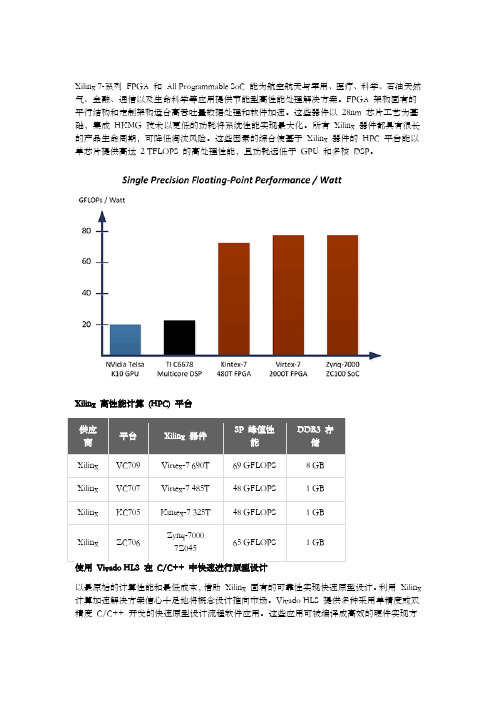

Xilinx 7-系列FPGA 和All Programmable SoC 能为航空航天与军用、医疗、科学、石油天然气、金融、通信以及生命科学等应用提供节能型高性能处理解决方案。

FPGA 架构固有的平行结构和定制架构适合高吞吐量数据处理和软件加速。

这些器件以28nm 芯片工艺为基础,集成HKMG 技术以更低的功耗将系统性能实现最大化。

所有Xilinx 器件都具有很长的产品生命周期,可降低淘汰风险。

这些因素的综合使基于Xilinx 器件的HPC 平台能以单芯片提供高达2 TFLOPS 的高处理性能,且功耗远低于GPU 和多核DSP。

Xilinx 高性能计算(HPC) 平台以最原始的计算性能和最低成本,借助Xilinx 固有的可靠性实现快速原型设计。

利用Xilinx 计算加速解决方案信心十足地将概念设计推向市场。

Vivado HLS 提供多种采用单精度或双精度C/C++ 开发的快速原型设计流程软件应用。

这些应用可被编译成高效的硬件实现方案,并可编程到Xilinx 28nm 器件中。

Vivado HLS 包含于Vivado Design Suite: System Edition。

使用C/C++ 和OpenCL 完成基于软件的系统实现Xilinx 目前正与早期的客户合作开发一个全新系统级的异构并行编程环境,在一个全面的基于Eclipse 的开发环境中利用C / C + +和开放计算语言(OpenCL®) 等抽象化计划。

该开发环境提供面向市场的库,可通过Xilinx All Programmable 器件显著提高异构系统(已验证)的生产力,并可助力需要实现并行架构的系统架构师、软件应用开发人员、和嵌入式设计人员提升系统性能、降低BOM 成本和总功率,开发时间符合ASSP、DSP、和GPU。

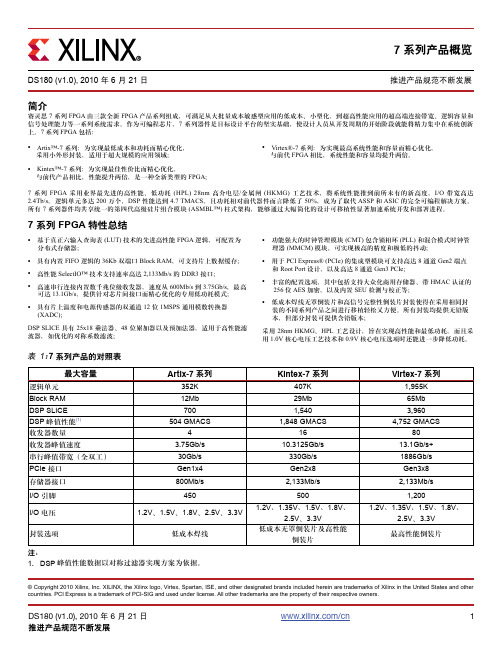

DS180 - Virtex-7 系列产品概览

Artix™-7 系列:为实现最低成本和功耗而精心优化, 采用小外形封装,适用于超大规模的应用领域; Kintex™-7 系列:为实现最佳性价比而精心优化, 与前代产品相比,性能提升两倍,是一种全新类型的 FPGA;

Virtex®-7 系列:为实现最高系统性能和容量而精心优化, 与前代 FPGA 相比,系统性能和容量均提升两倍。

表 3: Artix-7 FPGA 器件—封装组合及最大 I/O

封装(1) 尺寸 (mm) 器件 XC7A20 XC7A40 XC7A105 XC7A175T XC7A355T 注: 列示的所有封装均为无铅版本,部分封装可提供含铅版。 CPG236 10 x 10 GTP 0 0 0 I/O 100 140 140 0 0 0 200 210 210 0 4 4 285 285 285 CSG324 15 x 15 GTP I/O CSG484 19 x 19 GTP I/O FTG256 17 x 17 GTP 0 0 I/O 100 170 0 0 0 300 325 325 4 4 450 450 FGG484 23 x 23 GTP I/O FGG784 29 x 29 GTP I/O

2 /cn DS180 (v1.0), 2010 年 6 月 21 日 推进产品规范不断发展

7 系列概览

Kintex-7 FPGA 特性总结

表 4: 按器件划分的 Kintex-7 FPGA 特性总结

功能强大的时钟管理模块 (CMT) 包含锁相环 (PLL) 和混合模式时钟管 理器 (MMCM) 模块,可实现极高的精度和极低的抖动; 用于 PCI Express® (PCIe) 的集成型模块可支持高达 8 通道 Gen2 端点 和 Root Port 设计,以及高达 8 通道 Gen3 PCIe; 丰富的配置选项,其中包括支持大众化商用存储器、带 HMAC 认证的 256 位 AES 加密,以及内置 SEU 检测与校正等; 低成本焊线无罩倒装片和高信号完整性倒装片封装使得在采用相同封 装的不同系列产品之间进行移植轻松又方便。所有封装均提供无铅版 本,但部分封装可提供含铅版本;

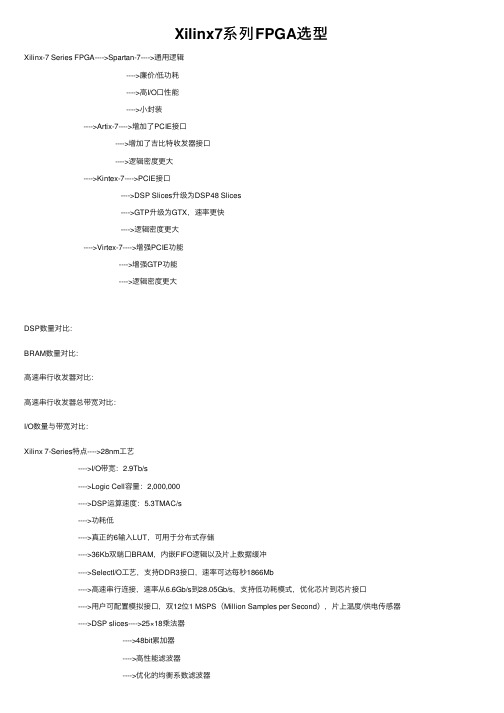

Xilinx7系列FPGA选型

Xilinx7系列FPGA选型Xilinx-7 Series FPGA---->Spartan-7---->通⽤逻辑---->廉价/低功耗---->⾼I/O⼝性能---->⼩封装---->Artix-7---->增加了PCIE接⼝---->增加了吉⽐特收发器接⼝---->逻辑密度更⼤---->Kintex-7---->PCIE接⼝---->DSP Slices升级为DSP48 Slices---->GTP升级为GTX,速率更快---->逻辑密度更⼤---->Virtex-7---->增强PCIE功能---->增强GTP功能---->逻辑密度更⼤DSP数量对⽐:BRAM数量对⽐:⾼速串⾏收发器对⽐:⾼速串⾏收发器总带宽对⽐:I/O数量与带宽对⽐:Xilinx 7-Series特点---->28nm⼯艺---->I/O带宽:2.9Tb/s---->Logic Cell容量:2,000,000---->DSP运算速度:5.3TMAC/s---->功耗低---->真正的6输⼊LUT,可⽤于分布式存储---->36Kb双端⼝BRAM,内嵌FIFO逻辑以及⽚上数据缓冲---->SelectI/O⼯艺,⽀持DDR3接⼝,速率可达每秒1866Mb---->⾼速串⾏连接,速率从6.6Gb/s到28.05Gb/s,⽀持低功耗模式,优化芯⽚到芯⽚接⼝---->⽤户可配置模拟接⼝,双12位1 MSPS(Million Samples per Second),⽚上温度/供电传感器 ---->DSP slices---->25×18乘法器---->48bit累加器---->⾼性能滤波器---->优化的均衡系数滤波器---->CMT---->PLL---->MMCM(混合模式时钟管理)---->MicroBlaze CPU---->整数计算能⼒260 DMIPs~441 DMIPs---->集成PCIe,x4 Gen2~x8 Gen3,适⽤于PCIe端点/根端⼝设计---->存储器256位AES加密,HMAC/SHA-256验证,内嵌SEU检测与错误校验---->环保⾼性能---->1.0V/0.9V内核电压下⾯这张表更直观的表明了⼏类的区别:⼀些概念:---->SSI⼯艺---->使⽤了多超级逻辑域SLR---->超级⾼带宽连接性---->低延迟---->低功耗---->两种---->逻辑加强型---->Virtex-7T---->DSP/BRAM/收发器密集型---->Virtex-7XT/HT---->⾼容量/⾼性能/短周期/低风险---->超级长布线资源/超级⾼性能时钟线 ---->CLBs---->真正6输⼊LUT---->可配制成⼀个6输⼊单输出LUT/64位ROM---->2个5输⼊LUTs/32位ROMs---->各⾃有⼀个输出---->共同的地址和逻辑输⼊---->每个LUT输出可选的连接到触发器---->4 LUTs+8 触发器+多路选择器+算术进位逻辑---->Slice---->2 Slices---->CLB---->8个触发器中的4个(每个Slice,每个LUT中的⼀个)---->锁存器latch ---->LUT可⽤作存储器---->所有slice的25%~50%使⽤它们的LUTs作为64位分布式RAM---->LUT可⽤作寄存器和移位寄存器---->所有slice的25%~50%使⽤它们的LUTs作为32位移位寄存器SRL32或2个SRL16 ---->时钟管理---->⾼速缓冲和布线---->低抖动---->频率合成和相移---->低抖动时钟⽣成器---->滤波---->⾼达24个时钟管理通道CMTs---->MMCM---->分数计数器---->固定或动态相移 ---->PLL---->频率合成器---->时钟抖动滤波---->中央有⼀个VCO---->频率⼤⼩和PFD传给VCO的电压有关---->3个可编程频率分频器---->D---->输⼊预分频---->M---->反馈分频---->O---->输出分频---->3个输⼊抖动滤波选项---->低带宽---->最好抖动衰减---->⾼带宽---->最好的相位偏移---->优化模式---->⼆者均衡---->时钟分配---->6种不同的时钟线---->BUFG/BUFR/BUFIO/BUFH/BUFMR/⾼性能时钟---->全局时钟---->32个全局时钟---->可作为所有触发器的时钟---->带使能/置位/复位---->BUGH驱动的12根时钟线,可以在任意时钟域驱动---->每个BUFH可以独⽴使能控制,所以可以在⼀个域内关掉时钟---->可由全局时钟缓冲器驱动---->⽆故障时钟分配和全局时钟使能---->由CMT驱动---->消除时钟分布延迟---->域时钟---->驱动域内所有时钟⽬标---->域定义指50 I/O和50 CLB和半芯⽚宽度的范围---->7系列可以有2~24个域---->每个域有4个域时钟通路---->域时钟缓冲器由4个时钟输⼊引脚驱动,同时可以进⾏1~8分频---->I/O时钟---->快速---->作为I/O逻辑或串⾏化/去串⾏化电路---->I/O可直接连接MMCM---->Block RAM---->双端⼝,72位,36kb BRAM---->可编程FIFO逻辑---->错误校验电路---->5到1880个---->读写同步操作---->可编程数据位宽---->DSP Slice---->25 × 18 ⼆互补乘加器48位⾼分辨率单乘加器---->单指令多数据运算单元SIMD/2操作数10个不同逻辑功能的逻辑单元 ---->省电预加器---->均衡滤波器---->流⽔线/ALU/专⽤总线级联---->up to 741MHz---->48位模式检测器---->⾼速度/⾼效率---->动态总线转换器---->内存地址发⽣器---->总线复⽤器---->I/O⼝存储器映射寄存器---->累加器可⽤作同步加减计数器---->输⼊输出---->SelectIO⼯艺---->1,866Mb/s DDR3接⼝---->⽚内⾼频去耦电容器增强信号完整性---->⽀持多种I/O标准---->HR IO---->宽电压范围(1.2V~3.3V)---->HP IO---->⾼性能操作---->以Bank组织,每Bank 50引脚---->每Bank由VCCO共同供电---->有些单端输⼊缓冲器需要外部参考电压VREF---->每Bank有2个VREF引脚(配置Bank 0除外)---->只能有⼀个VREF电压值---->多种封装---->电⽓特性---->上下拉输出结构---->可以设为⾼阻态---->可以设置压摆率和输出强度---->可以设置上拉和下拉电阻---->引脚对可以设置为差分输⼊输出---->可以设置100欧姆内部端接电阻---->多种差分接⼝标准:LVDS,RSDS,BLVDS,差分SSTL,差分HSTL---->每个IO⼝⽀持存储器接⼝标准---->T_DCI可以控制输出驱动阻抗---->串联端接/并联短接---->节省线路板空间---->输出模式或三态模式端接会⾃动关闭---->IBUF和IDELAY有低功耗模式---->8-bit IOSERDES 可完成串并与并串的转换---->可编程宽度2到8位---->⽀持相邻引脚级联---->专⽤过采样模式⽤于数据恢复---->如SGMII接⼝---->低功耗吉⽐特收发器---->集成PCIE接⼝---->配置---->模数转换。

xilinx的7系芯片选型手册

XC7A100T 101,440 15,850 126,800 1,188 135 4,860 6 300 144 240 1 1 1 8 -1, -2 -2L, -3 -1, -2, -1L

XC7A200T 215,360 33,650 269,200 2,888 365 13,140 10 500 240 740 1 1 1 16 -1, -2 -2L, -3 -1, -2, -1L

XMP086 (v4.7)

XC7A15T 16,640 2,600 20,800 200 25 900 5 250 120 45 1 1 1 4 -1, -2 -2L, -3 -1, -2, -1L

XC7A35T 33,280 5,200 41,600 400 50 1,800 5 250 120 90 1 1 1 4 -1, -2 -2L, -3 -1, -2, -1L

Notes: 1. Supports PCI Express Base 2.1 specification at Gen1 and Gen2 data rates. 2. Represents the maximum number of transceivers available. Note that the majority of devices are available without transceivers. See the Package section of this table for details. 3. Leaded package option available for all packages. See DS180, 7 Series FPGAs Overview for details. 4. Device migration is available within the Artix-7 family for like packages but is not supported between other 7 series families.

Xilinx Kintex-7系列FPGA高速采集卡中文资料

Xilinx Kintex-7系列FPGA高速采集卡中文资料基于Xilinx Kintex-7 FPGA,XC7K160/325/410T FBV676可选,DDR3 256MB/512MB可选。

NOR FLASH 256Mb,可根据开发需求自搭配,成本可控;工业级FMC连接器,支持高速ADC和DAC等FMC标准模块;PCI Express 标准,提供PCIe x2高速数据传输接口,单通道通信速率可高达5GBaud; Serial Rapid I/O,提供SRIO x2高速数据传输接口,单通道通信速率可高达5GBaud;SFP+光纤接口,传输速率可高达10Gbit/s;集成千兆网及I2C等常见接口,拓展能力强;提供板卡原理图和丰富的开发例程,入门简单。

图 1 Xilinx Kintex-7 FPGA基本参数图 2 TL-K7FMC采集卡正面图图 3 TL-K7FMC采集卡侧视图1图 4 TL-K7FMC采集卡侧视图2图 5 TL-K7FMC采集卡侧视图3图 6 TL-K7FMC采集卡侧视图4TL-K7FMC采集卡是一款广州创龙基于Xilinx Kintex-7系列FPGA自主研发的FMC数据采集卡,可配套广州创龙TMS320C6655、TMS320C6657、TMS320C6678开发板使用。

TL-K7FMC采集卡完全支持PCI Express 标准,串行高速输入输出SRIO总线通过HDMI接口提供稳定、可靠的高速传输能力,为产品的快速成型提供极大的便利。

TL-K7FMC采集卡的FMC接口不仅简化了I/O接口模块设计,提供高速的接口通信能力,而且提高了模块的利用率,标准化设计使产品有更好的通用性。

1 典型运用领域高速数据采集系统音视频数据处理系统图像处理设备软件无线电设备通信系统高精度仪器仪表高端数控系统 2 软硬件参数硬件参数ASP-134488-01400PINArrayEEPROMAT24C02SPIFLASHCDCM61002RESETDDR3Kintex-7Xilinx 7 seriesSerial Rapid IO x2PCIE GEN2 x4Kintex-XADCSFP+28nm Technology Low Cost FPGAOSC25MHzUART图 7 TL-K7FMC采集卡硬件框图JTAGPHYLED710-1100-304848PIN图 8 TL-K7FMC硬件资源图解1图 9 TL-K7FMC硬件资源图解2表1CPU RAM ROM EEPROM 网络 Xilinx Kintex-7 FPGA,XC7K160/325/410T FBV676 256MByte/512MByte DDR3 256MBit NOR FLASH 2KBit 10/100/1000M ETHERNET光纤接口 LED 3x 可编程指示灯 1x 复位按键按键 2x 用户可编程按键 1x SRIO TX,1x SRIO RX,2通道,单通道最高速率5GBaud,HDMI座 1x PCIe 4x(Gen2),2通道,单通道最高通信速率5GBaud 2x 48pin欧式连接器,GPIO拓展拓展IO 1x I2C,HDMI座 1x PMOD 1x XADC 1x FMC,400pin 仿真器接口启动方式串口电源开关电源接口 1x 14pin JTAG接口,间距 1x 2bit启动方式选择拨码开关 1x UART,Micro USB接口,提供4针TTL电平测试端口 1x 电源拨码开关 1x 12V 2A直流输入DC005电源接口,外径,内径 1x SFP+ 1x 供电指示灯软件参数表 2 Vivado版本号 3 开发资料提供采集卡原理图、入门教程、丰富的Demo程序;提供与DSP通信教程,完美解决DSP+FPGA异构平台通信开发瓶颈;提供完整的软件开发包,以及配套的开发文档。

Xilinx7系列FPGA高速收发器GTXGTH的一些基本概念

Xilinx7系列FPGA⾼速收发器GTXGTH的⼀些基本概念

本来写了⼀篇关于⾼速收发器的初步调试⽅案的介绍,给出⼀些遇到问题时初步的调试建议。

但是发现其中涉及到很多概念。

逐⼀解释会导致⽂章过于冗长。

所以单独写⼀篇基本概念的介绍,基于Xilinx 7系列的GTX。

需要说明,⽂本只是初步介绍基本概念,会尽量使⽤通俗浅显的描述⽽避免使⽤专业词汇,也只会描述⼀些基本的、常⽤的内容,不能保证全⾯型。

所以从专业⾓度看,可能部分⽤词和原⼚⽂档有出⼊,同时覆盖⾯不够,请见谅。

GTP、GTX、GTH和GTZ:

这四个是Xilinx 7系列FPGA全系所⽀持的GT,GT的意思是Gigabyte Transceiver,G⽐特收发器。

通常称呼为Serdes、⾼速收发器,GT,或者⽤具体型号(例如GTX)来称呼。

7系列中,按⽀持的最⾼线速率排序,GTP是最低的,GTZ是最⾼的。

GTP被⽤于A7系列,GTZ被⽤于少数V7系列。

从K7到V7,最常见的是GTX和GTH。

GTH的最⾼线速率⽐GTX稍微⾼⼀点点。

GTX和GTH的⽂档都是UG476。

从这⾥就能看出来,这两个GT的基本结构⼤同⼩异。

所以掌握⼀个,另⼀个基本也就熟悉了。

Xilinx Artix-7 FPGA AC701 评估套件说明书

EK-A7-AC701-G EK-A7-AC701-G.Xilinx Artix-7 FPGA AC701 EvaluationKitPart number: EK-A7-AC701-GProduct DescriptionThe Artix®-7 FPGA AC701 Evaluation Kit features the leading system performance per watt Artix-7 family to get you quickly prototyping for your cost sensitive applications. This includes all the basic components of hardware, design tools, IP, and pre-verified reference designs. This also features a targeted reference design enabling high-performance serial connectivity and advanced memory interfacing equipped with a full license for the Northwest Logic DMA engine.Key Features & Benefits∙Optimized for quickly prototyping cost sensitive applications using Artix-7 FPGAs∙Hardware, design tools, IP, and pre-verified reference designs∙Demonstrates a high performance data transfer system using a PCI Express® x4 Gen2∙Reference design implemented with Northwest Logic DMA engine attached to a AXI interface ∙Advanced memory interface with 1GB DDR3 SODIMM up to 533MHz / 1066Mbps∙Enabling high-performance serial connectivity with GTP ports on FMC, SFP, & SMA∙Supports embedded processing with MicroBlaze, soft 32bit RISC∙Develop networking applications with 10-100-1000 Mbps Ethernet (RGMII)∙Implement Video display applications with HDMI out∙Expand I/O with the FPGA Mezzanine Card (FMC) interfaceWhat's Included∙AC701 evaluation board featuring the XC7A200T-2FBG676C FPGA∙Full seat Vivado® Design Suite: Design Editiono Node locked & Device-locked to the Artix-7 XC7A200T FPGA, with 1 year of updates and support∙Full license for the Northwest Logic DMA with AXI interface∙Targeted Reference Design featuring DDR3, PCIe® and DMA∙AMS 101 evaluation card∙Printed Getting Started Guide∙Cables & Power Supply∙90-day limited warrantyKey FeaturesFPGA: Artix-7 XC7A200T-2FBG676C FPGAConfiguration∙Onboard JTAG configuration circuitry to enable configuration over USB∙JTAG header provided for use with Xilinx download cables such as the Platform Cable USB II ∙Quad SPI Flash: 32MB (256Mb)Memory∙DDR3 SODIMM 1GB up to 533MHz / 1066Mbps∙Quad SPI Flash: 32MB (256Mb)∙IIC EEPROM: 8Kb∙SD Card SlotCommunication & Networking∙10/100/1000 Mbps Ethernet (RGMII)∙SFP cage∙GTP port (TX, RX) with four SMA connectors∙UART To USB Bridge∙PCI Express 4-lane edge connectorDisplay∙HDMI video output∙LCD display (2x16)∙User LEDs (x4)Expansion Connectors∙FMC-HPC (Partially Populated) connectoro GTP Transceivers (x2) , 116 single-ended or 58 differential (34 LA & 24 HA) user defined signalso VADJ can support 1.8V, 2.5V (default), or 3.3V∙PMOD (1x6 0.1" Header)Clocking∙Fixed Oscillator with differential 200MHz outputo Used as the “system” clock for the FPGA∙User Programmable (IIC) Differential Oscillator (Range: 10MHz - 810 MHz, 156.250 MHz default) ∙Differential SMA clock input∙Differential SMA GTP reference clock input∙Jitter attenuated clocko Used to support CPRI/OBSAI applications that perform clock recovery from a user-supplied SFP/SFP+ moduleControl & I/O∙User Push Buttons (x5)∙User DIP Switch (4-position)∙SMA User I/O (Diff Pair)∙AMS FAN Header (2 I/O)∙7 I/O pins available through LCD headerPower∙AC Power adapter (12V) or ATXAnalog∙XADC headerEK-A7-AC701-G EK-A7-AC701-G.。

基于FPGA实现JESD204B高速接口设计

基于FPGA实现JESD204B高速接口设计曹鹏飞【摘要】JESD204B接口是高速ADC和DAC芯片采用的数据通信接口之一,具有传输速率高,抗干扰能力强,芯片间同步方便等优点.目前国内JESD204B接口应用多由国外集成芯片提供,缺乏自主性和灵活性.为了加强JESD204B接口自主设计,文章阐述了基于FPGA GTX高速收发器实现JESD204B接口通信的方法,详细说明了JESD204B接口的FPGA设计实现方案、同步化处理机制等内容.利用多通道JESD204B接口实现高速串行数据的传输,有效解决了传统并行数据采集存在的问题,满足实际工程的应用需求.【期刊名称】《无线互联科技》【年(卷),期】2018(015)023【总页数】3页(P19-21)【关键词】JESD204B;FPGA;高速串行传输;数据采集【作者】曹鹏飞【作者单位】天津中德应用技术大学智能制造学院,天津 300350【正文语种】中文模数转换器(Analog-to-Digital Converter,ADC)和数模转换器(Digital to Analog Converter,DAC)在众多领域中应用非常广泛,随着工艺的发展和实际应用的需要,采样速率和采样精度越来越高,采用传统的CMOS接口和LVDS接口已经无法满足设计的要求,而采用基于CML的JESD204B接口可以很好地解决这一问题,接口单通道速率可达12.5 Gb/s。

在ADC/DAC与FPGA处理芯片之间实现JESD204B接口,可以有效完成芯片间的高速数据传输,并且具有减少器件管脚和封装尺寸,减少占用布局空间,降低功耗等优点。

1 JESD204B概述JESD204B接口包括3个子类,分别为子类0、子类1和子类2。

JESD204B接口包括3个子类,分别为子类0、子类1和子类2。

3个子类的区别主要体现在同步方式各不相同。

子类0不支持确定性延迟,而子类1和子类2能够支持确定性延迟,可实现片间的数据同步。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

些 需 要 高 密 度 晶 体 管 和 逻 辑 ,以及 需 下 一 代 10 4 0 bts 用 的 Vr x7 0 . 0G i 应 / ie- t 要 极大 的 处 理 能 力 和 带 宽 性 能 的 市场 H P A.可 支 持 所 有 主 要 的 高 速 串 TF G

i m 83 8 r 莹 匝 t  ̄ 4 0 王 e 衄

荼 ,并 且 已经 开 始 宣 布 Vr x 中 期 产 带 来 了全 新 密 度 、 带 宽 和 节 能 优 势 。 ie- t 7

品 。 1月 底 ,Xl x 京 宣 布 了 2 n 相对于单片 器件 ,单位功耗 的芯片间 0 in 在 i 8m 0倍 ~3 的 3 ( 维 ) 封 装 技 术 , 预 计 2 1 带 宽提 升 了 10 .容 量提 升 2 倍 。 D 三 01 年 下 半 年 供 货 : 1 月 在 深 圳 宣 布 了 1 V -x 系 列 。预 计 2 1年供 货 。 he-HT t 7 02

自身设计之 中,获得 了专家评 审们的一致

一 年相介 程6来性 态域,等 除3实涉 队的比达 大0区校 硬大总 销支用 遥据自, 的更全 学.参 盘g本 控A裁 毁D与 参团性 “赛国 擦队郑 数与1 固&、 远共次 赛I师 广入 及参 ̄ 到,. 的年人 今亚晖 领加高 1太绍 4在所 加永 。生 报可 "0 吸围 往开 泛发 司数 名作 引多 了品

2 0 ADI 01 中国大 学 创新 设 计竞 赛 颁奖

获奖作品覆盖汽车 、导航 、航空 、人机 交互 等热点技术

日前 ,2 1 0 0ADI 中国大学创新设计竞 赛颁 奖典礼及 获奖作品在展 示华 中科技大学 举办,大赛分为高级组与专业组。其 中专业 据” ,以及浙江大学参赛队的 “ 于眼电信 基 号的无线便携 式的人机 交互 系统”获得 。 “ 远程遥控擦 除销毁固态硬盘数据”同时获

赛 灵 思 同业 界 领 先 的 代 工 厂 包 括

T MC ( S 台积 电 )等 在 内 的外 包 组 装

图2 通信设备市场规划

行 、光 学和 背板 协议 。该 备 商 可 以 开 发 更 高 P A

集 成 以及 带 宽 效 率 的 系 统 ,以 满 足 全

球有线基础设施和 数据中心对带宽的 套 件 提 供 配 套 的 软 件 支 持 。预 计 首 批 爆 炸 性 需 求 。 该 系 列 器 件 集 成 了业 内 产 品将 于 2 1 年 下 半 年 开 始供 货 。 0 1 最 高速 度 和 最低 的 收 发器 时钟 抖动 1 月 1 日 ,赛 灵 思 酋 演 中 期 产 性 能 , 同 时 还 支 持 最 严 苛 的 光 学 及 1 8 品 :内置 2 G i s 发 器  ̄ Vr x7 8 bt 收 / ie- t HT 背 板 协 议 。支 持 Vr x P A 的 IE ie- F G t 7 S

系 列 ,它 支 持 下 一代 i 0 4 0 bts 0 — 0 G i 通 /

图1 超薄的3 D封装

Dei ut 软 件 工 具 于 今 日上 市 。首 s nS i g e 信 系 统 应 用 ( 计 2 1年 下 半 年 以 后 批 Vr x7HT设 备 预 计 将 于 2 1 预 02 ie. t 0 2年 市 场 开 始 部 署 ) ,适 用 于 行 业 最 高 带 上半年上市 。

技 大学参赛 队的 “ 基于有H l a传感器的直流 广东工业大学参赛队的 “ l 激光书写LD点 阵 E 伍 将 A 最 新 发 布 的 模 数 / 模 转换 器 ,数 DI 数

无刷电机的电动车辆驱动系统”、国防科技 显示屏”等7 个作品获得。

字 信 号 处 理 器 等行 业 领 先技 术 成 功 应 用 于

责 编 王 任 辑: 莹

n ut d s ̄Spo l t l 业 聚 焦 ti 产 gh

Xin 展望7 lx i 系列:F GA P 给力高密度和高收发

D封 装 技 术 和 硅 通 孔 尽 管Xl x 8 m工 艺 的 7 列 产 品 应 用 。通 过 采 用 3 in n i 2 系 明 年 才 能 出 货 ,但 其 宣 传 攻 势如 火 如 ( S 技 术 ,赛 灵 思 2 n 7  ̄ F G T V) 8 m 系 q P A J

方 面均 实 现 了新 的 突破 ,达 到 了 赛 史 上 的

又一高峰 。此外 ,本次竞赛由A DI“ 客户技 术 支持 中心” 团队全程提供 专业技 术支持

组有1个参赛队获奖,一等奖分别由华中科 得专业组 最佳创意奖。高级组一等奖分别由 3 与指导 。值得 关注的是 ,此 次不少参 赛队

参 考 阅读 :)l xF G (i :P A立体 封 装 in 欲 超 越 摩 尔 定律 ht: w nyn 1 t / ag i . p / g

s c se pw c l n atce / ril / pa e .e .on c / ril s a tce

中集成多个 F G P A芯 片 .实 现 突 破性 宽 线 路 卡 的 全 新 F G P A,可 以 提 供 多 的 容 量 、 带 宽 和 功 耗 优 势 ,以满 足 那 达 1 6个 2 G i s 行 收 发 器 ,支 持 8 bt 串 /

1 月 2 日 ,X l x 布 推 出 堆 叠 与 测 试 合 作 伙 伴 建 立 了 强 大 可 靠 的 供 O 8 in 宣 i 硅 片 互 联 技 术 , 即 通 过 在 单 个 封 装 应 链 ,为 芯 片 工 艺 提 供 强 大 支 持 。 目 前 已 向客 户 推 出试 用 版 的 IE1.设 计 S 1 3