EMC DMX存储的物理架构与逻辑架构

EMC 信息存储与管理(要点总结)

管理 CLARiiON:命令行界面(Naviseccli)、图形用户界面(Navisphere)

Navisphere 套件:

• Navisphere Manager:配置 CLARiiOn,基于 Web 的界面

磁盘驱动器接口

磁盘驱动器的性能(寻道时间、旋转延迟、数据传输速率)

•

寻道时间:读写头在盘面上移动进行定位的时间。(全程时间、平均时间、 相邻磁道时间)

• 旋转延迟:盘片旋转以定位读写头下方的数据所用的时间 • 数据传输速率:每个单位时间磁盘能够传输到 HBA(主机总线配置器)的

平均数据量

影响磁盘性能的基本准则 将磁盘看成两部分:

• 最近最少访问算法(Least Recently Used,LRU):连续地监视数据访问, 识别出长时间没有被访问的页面。

• 最近访问算法(用的页面将被释 放或标记为可重用。

缓存写入数据时,存储系统必须将脏页面刷清以保证或标记为可重用。刷清模式 如下

带有缓存的写操作:一个 I/O 被写入缓存并得到响应比直接写入磁盘所用的时间 要少得多,还可以合并优化。

• 回写缓存:数据被存入缓存,主机立即响应。 • 直接写操作:数据被存入缓存并立即写到磁盘中,然后响应主机。

缓存实现(专用缓存,全局缓存)

缓存管理(为了能够在系统中总是保留一部分页面以及可以在需要时被释放的页 面)

嵌套 RAID(许多数据中心对 RAID 阵列的数据冗余和性能都有需求)

RAID 3(通过存储分带提供高性能,并利用奇偶校验提升容错性)RAID 4(与 RAID 3 类似,支持独立访问)

EMC DMX4-950产品介绍

产品介绍世界上最可靠的存储平台企业关键型应用程序需要企业关键型存储Array EMC 通过提供 EMC® Symmetrix® Direct Matrix™(DMX) 系列满足了这一需要,该系列高端网络存储系统性能最高、容量最大、功能最全,而且价格极具竞争力。

系统所具备的这些能力使其不同于市场上提供的任何其他存储系统。

下面是详细介绍:信息可用性• 一款技术最先进、部署范围最广泛的业务连续性平台分层存储整合• 整合应用程序层以满足范围最广的服务级别可预测的性能• 支持世界上要求最苛刻的应用程序工作负载应用程序集成和认证• 最高级别的应用程序集成可加快部署速度并减少风险电源效率• 提供最佳电源和冷却效率以满足当前数据中心需求内置的以信息为中心的安全保护• 高级安全机制和集成的 RSA 技术简化的管理和操作• 简化的存储分配、资源管理和分层EMC Symmetrix DMX 系列是高端信息存储系统的业界标准—在可用性、整合、性能、应用程序集成、电源效率和以信息为中心的安全保护方面是无可匹敌的市场领导者。

DMX系列的体系结构经得起未来时间的考验,性能无与伦比,而且还有一整套功能强大的由 EMC 以及第三方提供的软件工具,满足了您对现在的高端网络存储系统的要求和对服务级别的期许。

Symmetrix DMX 系列涵盖了大规模存储整合的关键尺寸、增量分层存储扩展能力和无中断的应用程序支持,使这些系统能够轻松满足最大、要求最苛刻而且增长最快的应用程序的需要。

使用为您的企业提供的一整套灵活的配置选择,您将能够确保以不折不扣的服务级别来支持您的信息存储和管理要求。

Symmetrix DMX — 面向今后十年的存储体系结构在设计上克服了其他传统高端存储系统固有的吞吐量、带宽、可扩展性和响应时间等障碍。

能够实现这一点,在一定程度上是由于该产品在通道控制器与全局内存之间提供了多达 128 条直接而且专用的数据路径,其间没有阻碍性能的总线或交换机。

EMC现代数据中心超融合基础架构

EMC现代数据中心超融合基础架构EMC现代数据中心超融合基础架构是EMC公司推出的一种先进的数据中心架构,它将计算、存储、网络和虚拟化技术集成在一起,形成一种高度集成的解决方案。

这种架构通过将不同的硬件和软件组合在一起,实现了数据中心的高度集中化和自动化,提高了数据中心的性能、可靠性和灵活性。

本文将详细介绍EMC现代数据中心超融合基础架构的原理、特点和优势。

EMC现代数据中心超融合基础架构的主要原理是将不同的硬件和软件集成在一起,形成一个高度集中化和自动化的解决方案。

这种集成使得数据中心可以更加灵活地配置资源,提供更高的性能和可靠性。

具体来说,EMC现代数据中心超融合基础架构包括以下几个方面的技术:首先,EMC现代数据中心超融合基础架构采用了虚拟化技术。

虚拟化是将物理资源抽象成虚拟资源的过程,可以使得不同的软件可以在相同的硬件上运行。

通过虚拟化,EMC现代数据中心超融合基础架构可以更好地利用物理资源,提高数据中心的利用率和灵活性。

其次,EMC现代数据中心超融合基础架构采用了软件定义存储(SDS)技术。

SDS是一种通过软件实现存储功能的技术,可以将不同的存储设备组合在一起,形成一个虚拟的存储资源池。

通过SDS,EMC现代数据中心超融合基础架构可以更好地管理和利用存储资源,提高数据中心的存储性能和可靠性。

再次,EMC现代数据中心超融合基础架构采用了软件定义网络(SDN)技术。

SDN是一种通过软件实现网络功能的技术,可以将不同的网络设备集中管理起来,形成一个虚拟的网络环境。

通过SDN,EMC现代数据中心超融合基础架构可以更好地管理和配置网络资源,提高数据中心的网络性能和可靠性。

最后,EMC现代数据中心超融合基础架构还采用了自动化管理技术。

通过自动化管理,EMC现代数据中心超融合基础架构可以自动监控和管理数据中心的各种资源,提高数据中心的运营效率和稳定性。

同时,自动化管理还可以提供更好的自服务功能,使得用户可以更方便地使用数据中心的资源。

emc存储原理

EMC(Electromagnetic Compatibility,电磁兼容性)存储原理是指在电子设备中,各种电子设备和系统之间能够共存并正常工作的能力。

它涉及到电磁波的辐射和抗干扰能力。

在电子设备中,各种电子元件和电路都会产生电磁辐射,这些辐射会干扰其他设备的正常工作。

为了保证设备之间的正常工作,需要进行EMC设计和测试。

EMC存储原理主要包括以下几个方面:

1. 电磁辐射控制:通过合理的电路设计和电磁屏蔽措施,减少电子设备产生的电磁辐射,以避免对其他设备的干扰。

2. 抗干扰能力:通过合理的电路设计和电磁屏蔽措施,提高电子设备的抗干扰能力,使其能够在电磁环境复杂的情况下正常工作。

3. 地线设计:合理的地线设计可以减少电磁辐射和提高抗干扰能力。

4. 电磁波吸收材料:使用电磁波吸收材料可以减少电磁辐射和抑制干扰。

5. 电磁屏蔽:通过使用金属屏蔽罩、屏蔽盒等措施,将电子设备与外界隔离,减少电磁辐射和抑制干扰。

EMC存储原理的目标是保证电子设备之间的相互兼容性,使其能够在同一电磁环境下正常工作,同时减少对其他设备的干扰。

这对于保证电子设备的可靠性和稳定性非常重要。

DMX512协议说明

DMX512协议1.协议简介DMX是Digital MultipleX的缩写,意为多路数字传输。

DMX512 控制协议是美国舞台灯光协会(USITT)于1990年发布的灯光控制器与灯具设备进行数据传输的工业标准,全称是USITT DMX512(1990) ,包括电气特性、数据协议、数据格式等方面的内容。

2.电气特性和物理层2.1.电气特性DMX512采用EIA-485标准。

发送端:逻辑“1”以两线间压差+(2~6)V表示;逻辑“0”以两线间压差为-(2~6)V表示;接收端:A比B高200mv以上即认为是逻辑“1”;A比B低200mv以上即认为是逻辑“0”。

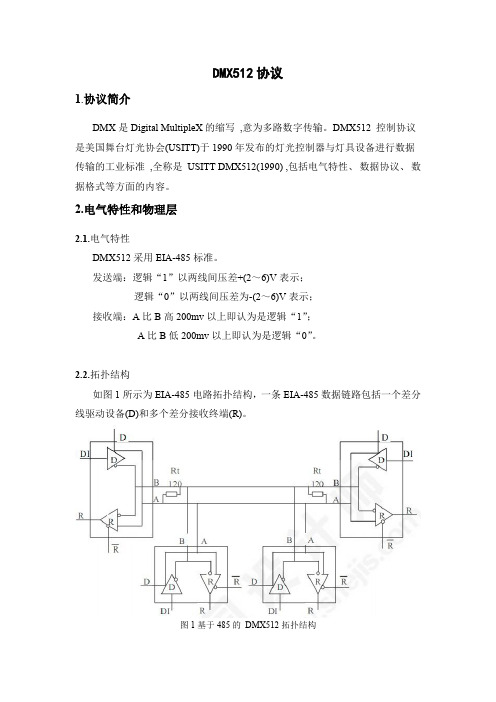

2.2.拓扑结构如图1所示为EIA-485电路拓扑结构,一条EIA-485数据链路包括一个差分线驱动设备(D)和多个差分接收终端(R)。

图1基于485的DMX512拓扑结构2.3.DMX512 端口及数据链路因为是采用485差分信号传输,因此DMX512端口一般采用3针或5针接口,相对应的导线则为1对或2对双绞线,导线同时应采用箔片或编织筛包裹。

XLR 针口分配如下表1所示,其中辅助数据链路可以不用。

表1 DMX512端口信号分配基于EIA-485传输距离理论上可以达到1200m,建议控制在800m以内,若要加长传输距离,则需考虑中继器。

DMX512数据链路的终接方式应消除信号环路和信号反射,否则可能导致正确设计的系统出现误操作。

采用结终端电阻的方式可以消除信号反射,DMX512标准要求,终端电阻应放置在数据+和数据-信号针之间,阻抗范围120Ω+5%~120Ω-10%。

3.数据协议格式及传输DMX512 协议规定数据以数据包的形式通过异步通讯的方式进行传输。

每个数据包由若干数据帧组成, 每帧数据包括1 位低电平起始位、8 位数据位和2 位高电平停止位。

DMX512协议要求数据传输的波特率为250kbps, 亦即每位的传输时间为4us, 每帧数据的传输时间为44us, 它支持多达512 帧数据传输, 每帧数据与相应的控制支路相对应。

EMC 存储技术介绍

保护在磁盘驱动器和 DAE 上的投资

CLARiiON CX3-80

CLARiiON CX3-40

CLARiiON

CX3-20

CLARiiON

CLARiiON CX3-10

CX700

CLARiiON

CLARiiON CLARiiON

8

信息生命周期管理

阶段 1: 分层基础结构

应用 应用 应用 数据 数据 数据

阶段 2: 特定于应用程序的 ILM

应用

应用

应用

数据 数据

阶段 3: 跨应用程序的信息生命周期管理

应用 应用 应用

• 基础结构分类 • 信息的存放位置 • 存储管理自动化

• 关键应用程序的策略 • 特定于应用程序的 ILM 组件

© Copyright 2008 EMC Corporation. All rights reserved.

产品

5个9

可维护性

流程

© Copyright 2008 EMC Corporation. All rights reserved.

1113

CLARiiON CX3 Series Architecture

UltraScale Storage Processor

Fibre Channel Mirrored cache CPU CPU FC FC FC FC

4GLCC

4GLCC

4GLCC

4GLCC

4GLCC

4GLCC

UltraScale Storage Processor

Fibre Channel Mirrored cache CPU CPU FC FC FC FC

EMC HDS IBM三款高端存储之结构对比

EMC/HDS/IBM三款高端存储之结构对比作者:piner (转载请注明本文出处:)永久链接:/html/y2007/m05/98-storage-contrast.html我在前面介绍了现在比较流行的三款高端存储的基本体系结构,包括IBM 的ds8000系列,hds的usp系列以及EMC的dmx3系列。

我在这里将三款高端存储再做一个简单的对比。

1、体系结构hds与emc都采用了多点冗余的复合式体系结构,有多个专用的存储控制器,如专用的前端控制器,专用的后端控制器,并且以以专用的cache 控制器为核心,CPU集成在前/后端控制器中,操作系统以微码方式集成在硬件中,并可以方便的升级维护。

在这种结构中,前端,cache,后端均可实现系统均衡,并多点冗余。

所以,失败一个点的时候,影响量比较小。

不过,还有一点差别的是,hds前后端连接到核心cache,是采用交换方式,而EMC是采用直连方式,所以也叫直连矩阵。

至于IBM,采用的是传统的对称体系结构,采用其强大的570 pserver作为存储的控制器,所以,存储的管理OS运行在控制器内,CPU与内存也都在控制器内。

这一种体系结构是应当是说与现有的中端存储的结构很相似,IBM的这种方式的体系结构在可靠性方面是比上面的体系结构要欠缺一些的。

2、后端连接与RAIDIBM采用交换方式连接磁盘与后段卡,而HDS与EMC采用环路结构,在交换结构中,每个磁盘都有自己的线路连接到后端卡(口),所以,不容易产生后端瓶颈。

至于环路设计,则是现在的流行设计,但是,一个环路上的盘不能太多,否则,容易产生性能瓶颈。

如,一个2Gb的光纤环路,一般接到50-60颗盘,已经都达到负载极限了。

而一个4Gb的环路,如果考虑翻倍的话,也就最多可以接100-120颗磁盘。

不过,上面评估磁盘个数的时候,是根据流量,也就是带宽来考虑的,如果在OLTP环境中,我们还需要考虑IO个数,因为光纤通信的规则,在同一个时间,一个环路中只能有一个通信量,也就是一个IO。

EMC DMX-3 系列存储产品技术介绍-060915

EMC DMX-3 系列产品技术介绍EMC公司广州办事处2006年9月目录1.SYMMETRIX DMX-3 存储系统特点 (3)1.1. 实现无任何损失整合 (3)1.2. 关键型应用环境 (3)1.3. 重要特性 (3)2.SYMMETRIX DMX-3先进体系结构 (5)2.1. 最先进体系结构 (5)2.2. 业界最高性能 (6)2.3. 业界最高可用性 (7)2.4. 高效C ACHE技术 (8)3.SYMMETRIX DMX-3的高可靠性 (10)3.1. 完全高度冗余 (10)3.2. 深度数据保护 (10)3.3. 智能化后台自我维护系统 (11)3.4. 无任何中断的服务及修复 (12)3.5. 不间断电源系统 (12)4.EMC 存储软件功能 (14)4.1. 概述 (14)4.2. 存储管理软件 (14)4.3. 信息管理软件 (15)4.4. 信息移动软件 (16)4.5. 基础结构软件 (17)5.EMC DMX 产品型号 (18)5.1. EMC S YMMETRIX DMX800 (18)5.2. EMC S YMMETRIX DMX1000/2000/3000 (18)5.3. EMC S YMMETRIX DMX-3 (19)1. S YMMETRIX DMX-3存储系统特点1.1. 实现无任何损失整合EMC Symmetrix® DMX-3系列是高端信息存储系统的业界标准—在性能、容量、可用行和投资保护方面是无出其右的市场领导者。

DMX-3系列的体系结构经得起未来时间的考验,性能无与伦比,而且还有一整套功能强大的由EMC 以及第三方提供的软件工具,满足您对高端网络存储系统的要求和对服务级别的期许。

Symmetrix DMX-3 系列涵盖了大规模存储整合的关键尺寸、增量分层存储扩展能力和无中断的应用程序支持,使这些系统能够轻松满足最大、要求最苛刻而且增长最快的应用程序的需要。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EMC DMX存储的物理架构与逻辑架构

一.DMX存储概述

DMX存储硬件的物理与逻辑架构能够实现最大限度的将一个lun 的io 最大限度分摊给硬盘,DAE盘阵的环路; 一个lun 的io 同时也平均分摊给后端的存储cpu . 从后面文档设备连接的介绍可以知晓.

DMX的架构做到了最大限度的打散数据以达到性能最大化;性能最大化的硬件配置是一个控制柜加两个与控制柜存储cpu端口直连的磁盘柜;

存储卷vol 以及4个vol meta(绑定) 条带化以后就避免了热点(hot block) 读写的问题.

将任何一个lun的读写io 操作做到由最多的硬件资源来支撑. 硬件资源主要是硬盘,DAE盘阵环路,存储cpu,存储缓存.

DMX存储安装配置是通过加载预先配置好的bin file 来部署的; bin file 定义了物理架构与逻辑架构的配置定义整个存储当前硬件配置如何被使用规划好,以后修改配置就得重新装载bin file 也就是重新配置整个存储.

Bin file的加载以及整个存储的管理通过console服务器上的软件symmwin来操作,console服务器通过电话线moden 与EMC 支持中心连通. EMC技术人员通过电话线的拨号拨入方式可以做到完全掌控存储设备.

本文档关注存储设备架构方面,管理方面的gk盘,ecc等不做赘述.

二.E MC DMX 存储的物理架构

1.存储外观及各个模块介绍

(1)外观

DMX由一个控制柜加磁盘柜组成, 通常带2个或者5个磁盘柜

我们公司为了性能最大化,配置满配的前端后端卡,只挂2个磁盘柜.再扩展磁盘

机柜只增加空间,性能不增长.

,

BAY

BAY

(2)物理构成模块图示: (打开机柜门前视图)

2.存储后端接线连接以及磁盘环路

DA卡cpu端口与硬盘的连线图示:

这里的图示是端口所管理的硬盘,是指硬盘的主环路(BUS loop),实际情况物理联线只连接到DAE 的LCC A & LCC B 端口.

方环路的硬盘,也就是互为standby 环路.

DA 卡cpu 与 DAE 盘柜 的对应关系

三.E MC DMX 存储的逻辑架构

●存储最小的可用单元是cylinder (每个cylinder 960k) ;

●每个cyln 由15个64k 的块组成.

●每个硬盘以cyln为单位划分成n 个hyper(也叫切片)

●以DA02 D1:05 (DA卡2,D cpu port 1口管理的DAE ID 5硬盘为例)

1.DA02 D1:05 硬盘被切成了14块,前面9块都是16570 cyln 的大小的数据

空间, 后面5块是3 cyln 的管理用的GK盘.

2.然后以16570 cyln为单位的15GB(16570*960k/1024)大小的hyper 来与其

他硬盘里面的同样是16570 cyln 的hyper 来做镜像成为一个卷(vol). 大

多数情况下某个硬盘里面的数据(vol) 与另外一个硬盘的数据一摸一样.

3.看如下图示: 镜像1 是M1, 镜像2 是M2. 互相交叉. 后面的6,7,8 ……都

是同样情况,两块硬盘数据一样,镜像1 镜像2 交叉放.

4.卷volume 分配给主机的时候都是连续地分配出去, 而如下图两个硬盘里

面的vol 都是不顺序的,是打散的,这样就打散了主机对存储读写的io.

DA02 D1:05

DA02 D1:05

如下图示:

每个卷底层都是由8个硬盘来支持,并且由八个cpu通道来支持,因为八个

硬盘都算来自不同的硬盘DAE盘阵,能达到最佳的IOPS.

dmx系统只将MetaPosition 0 的卷名(meta位置0的) 映射给主机,一个卷也

就是作为一个lun来使用. 这里举例的情况是两个hyper先镜像,然后4个Array

6.主机端查看分配的lun的volume 信息

用powerpath工具powermt 看Logical device ID

例如:

Pseudo name=emcpowerbd

Symmetrix ID=000290105785

Logical device ID=05EB

state=alive; policy=SymmOpt; priority=0; queued-IOs=0

========================================================

--- Host -- - Stor - -- I/O Path - -- Stats ---

### HW Path I/O Paths Interf. Mode State Q-IOs Errors ========================================================

2 qla2xxx sdbq FA 14dA active alive 0 0

3 qla2xxx sdev FA 13dA active alive 0 0

3 qla2xxx sdgo FA 14dA active alive 0 0

4 qla2xxx sdjt FA 3dA active alive 0 0

4 qla2xxx sdlm FA 4dA active alive 0 0

5 qla2xxx sdor FA 3dA active alive 0 0

5 qla2xxx sdqk FA 4dA active alive 0 0

2 qla2xxx sdx FA 13dA active alive 0 0

主机能看到05EB 卷的有: 172.23.106.2, 172.24.67.2 ……。