实验11 位同步提取实验

通信原理实验

上海工程技术大学通信原理综合实验报告学院电子电气工程学院专业电子信息工程班级学号022211117学生沈文杰指导教师赵晓丽一.验证性实验1.模拟信号源实验一、实验目的1、熟悉各种模拟信号的产生方法及其用途2、观察分析各种模拟信号波形的特点。

二、实验内容1、测量并分析各测量点波形及数据。

2、熟悉几种模拟信号的产生方法、来源及去处,了解信号流程。

三、设计思想利用信号源模块和20M 双踪示波器进行模拟信号源实验。

主要测试点和可调器件说明如下:1、测试点2K同步正弦波:2K的正弦波信号输出端口,幅度由W1调节。

64K同步正弦波:64K的正弦波信号输出端口,幅度由W2调节。

128K同步正弦波:64K的正弦波信号输出端口,幅度由W3调节。

非同步信号源:输出频率范围100Hz~16KHz的正弦波、三角波、方波信号,通过JP2选择波形,可调电阻W4改变输出频率,W5改变输出幅度。

音乐输出:音乐片输出信号。

音频信号输入:音频功放输入点(调节W6改变功放输出信号幅度)。

2、可调器件K1:音频输出控制端。

K2:扬声器控制端。

W1:调节2K同步正弦波幅度。

W2:调节64K同步正弦波幅度。

W3:调节128K同步正弦波幅度。

W4:调节非同步正弦波频率。

W5:调节非同步正弦波幅度。

W6:调节扬声器音量大小。

四、实验方法1、用示波器测量“2K同步正弦波”、“64K同步正弦波”、“128K同步正弦波”各点输出的正弦波波形,对应的电位器W1,W2,W3可分别改变各正弦波的幅度。

参考波形如下:2、用示波器测量“非同步信号源”输出波形。

1)将跳线开关JP2选择为“正弦波”,改变W5,调节信号幅度(调节范围为0~4V),用示波器观察输出波形。

2)保持信号幅度为3V,改变W4,调节信号频率(调节范围为0~16KHz),用示波器观察输出波形。

3)将波形分别选择为三角波,方波,重复上面两个步骤。

3、将控制开关K1设为“ON”,令音乐片加上控制信号,产生音乐信号输出,用示波器在“音乐输出”端口观察音乐信号输出波形。

数字同步技术

实验十一 数字同步技术实验内容1.位定时、位同步提取实验2.信码再生实验3.眼图观察及分析实验4.CPU仿真眼图观察测量实验一. 实验目的1.掌握数字基带信号的传输过程。

2.熟悉位定时产生与提取位同步信号的方法。

3.学会观察眼图及其分析方法。

二. 实验电路工作原理所有数字通信系统能否有效地工作,在相当大的程度上依赖于发端和收端正确地同步。

同步的不良将会导致通信质量的下降,甚至完全不能工作。

通常有三种同步方式:即载波同步、位同步和群同步。

在本实验中主要分析位同步,载波同步和群同步不分析。

实现位同步的方法有多种,但可分为两大类型:一类是外同步法。

另一类是自同步法。

所谓外同步法,就是在发端除了要发送有用的数字信息外,还要专门传送位同步信号,到了接收端得用窄带滤波器或锁相环进行滤波提取出该信号作为位同步之用。

所谓自同步法,就是在发端不专门向收端发送位同步信号,而收端所需要的位同步信号是设法从接收信号中或从解调后的数字基带信号中提取出来。

本实验中,位同步提取的方法是从二相PSK(DPSK)信号中,对解调出的数字基带信息再直接提取恢复出位同步信号。

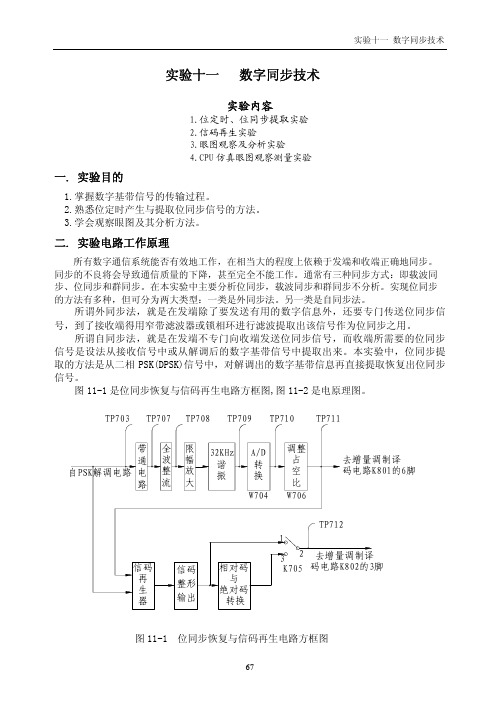

图11-1是位同步恢复与信码再生电路方框图,图11-2是电原理图。

图11-1 位同步恢复与信码再生电路方框图1.带通滤波与全波整流电路电路如图11-3所示。

设计该电路时,以数字基带码元速率为32KHz/s为例,数字基带信号由测量点TP703输入,经过电解电容E701与电阻R717进入该电路,带通滤波器由U711组成,测量点TP707为眼图测量点,利用二踪示波器的YB通道测量TP304或TP703,YA通道测量TP707时,调节示波器相应的开关与旋钮,就可以测量出眼图信号来。

关于眼图的具体测量在后面再作进一步的介绍。

由运算放大器U711∶C组成全波整流电路。

从图中可知,运算放大器U712(LM311)组成限幅放大电路。

32KHz谐振电路由电阻R731、R732、R722、电容C716、CA701(在电路板上这里为一可插入不同容量的电容作为实验调试,实验值为4700pf)、谐振线圈L701组成。

试验11DPSK调制解调

实验11 DPSK调制解调一、实验目的1.掌握差分编码与差分译码的原理及实现方法。

2.掌握DPSK调制与解调的原理及实现方法。

3.由“倒n”现象分析DPSK调制方式。

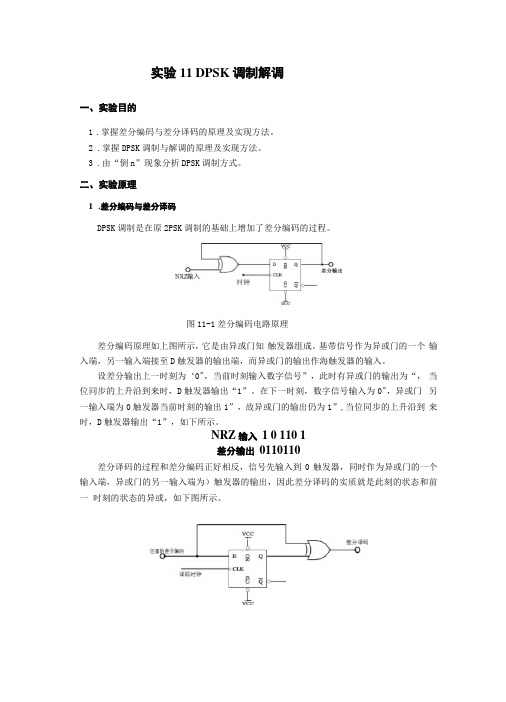

二、实验原理1.差分编码与差分译码DPSK调制是在原2PSK调制的基础上增加了差分编码的过程。

图11-1差分编码电路原理差分编码原理如上图所示,它是由异或门知触发器组成。

基带信号作为异或门的一个输入端,另一输入端接至D触发器的输出端,而异或门的输出作海触发器的输入。

设差分输出上一时刻为‘0",当前时刻输入数字信号”,此时有异或门的输出为“,当位同步的上升沿到来时,D触发器输出“1”。

在下一时刻,数字信号输入为0",异或门另一输入端为0触发器当前时刻的输出1”,故异或门的输出仍为1”,当位同步的上升沿到来时,D触发器输出“1”,如下所示。

NRZ输入1 0 110 1差分输出0110110差分译码的过程和差分编码正好相反,信号先输入到0触发器,同时作为异或门的一个输入端,异或门的另一输入端为)触发器的输出,因此差分译码的实质就是此刻的状态和前一时刻的状态的异或,如下图所示。

2 . DPSK 调制解调在2PSK 解调中,如解调用的相干载波与调制端的载波相位反相时,则解调出的基带信号 恰与原始基带信号反相,这就是2PSK 解调中的“倒n”现象。

在PSK 的实验中,我们观察 到相位模糊(“倒n”)的现象,但是如何解决相位模糊的问题呢,在实际系统中一般通过 DPSK 的方法解决该问题。

即在调制前,先对输入的基带信号进行差分编码(绝对硼对码转 换),然后对解调后的信号进行差分译码(相对码-绝对码转换),还原出基带信号,通过这 个方法,即使出现相位模糊的情况,也不会影响最终的解调输出。

通俗来讲,DPSK 调制解 调是在PSK 的基础上增加了差分编码和差分译码。

DPSK 调制信号如下图所示。

在DPSK 解调中,无论解调用的相干载波是否与调制端的载波相位同相或反相,解调出的 基带信号与原始基带信号同相。

通信原理实验指导书(学生)

通信原理实验指导书西南大学电子信息工程学院实验教学中心目录前言 .............................................. 错误!未定义书签。

目录 (1)拨码器开关设置一览表 (2)第一部分通信原理预备性实验 (5)实验1 平台介绍及实验注意事项 (5)实验2 DDS信号源实验 (8)第二部分通信原理重要部件实验 (11)实验1 抽样定理及其应用实验 (11)实验2 PCM编译码系统实验 (16)实验3 FSK(ASK)调制解调实验 (20)实验4 PSK DPSK调制解调实验 (25)实验5 位同步提取实验 (33)实验6 眼图观察测量实验 (38)实验7 基带信号的常见码型变换实验 (43)实验8 AMI/HDB3编译码实验 (50)实验9 幅度调制(AM)实验* (54)实验10 幅度解调(AM)实验* (61)实验11 频率调制(PM)实验* (64)实验12 频率解调(PM)实验* (68)第三部分信道复用技术和均衡技术实验 (72)实验1 频分复用/解复用实验 (72)实验2 时分复用/解复用(TDM)实验 (76)拨码器开关设置一览表在本实验平台上,我们采用了红色的拨码器,设置各种实验的项目、信号类型、功能和参数。

拨码器的白色开关上位为1;下位为0。

现将各主要拨码开关功能列表说明如下:注:1. 时钟与基带数据产生模块中各铆孔与测量点说明:4P01为原始基带数据输出铆孔; 4P02为码元时钟输出铆孔;4P03为相对码输出铆孔。

4TP01为码型变换后输出数据测量点;4TP02为编码时钟测量点。

2.以上实验设置的功能和各种参数也可根据学校要求定制。

表0-2“信道编码与ASK。

FSK。

PSK。

QPSK调制”拨码开关SW03状态设置与功能一览表表0-3“基带同步与信道译码模块”拨码开关25SW01状态设置与功能一览表注:译码模块25SW01第一位X为空位待用。

AMI码型变换实验

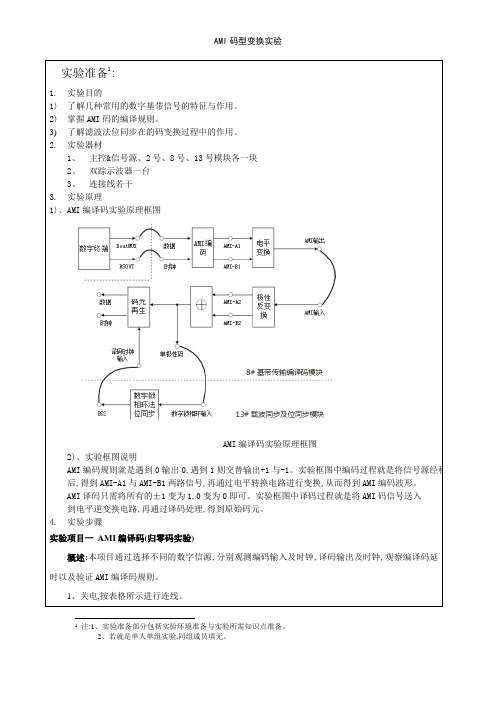

实验准备1:1.实验目的1)了解几种常用的数字基带信号的特征与作用。

2)掌握AMI码的编译规则。

3)了解滤波法位同步在的码变换过程中的作用。

2.实验器材1、主控&信号源、2号、8号、13号模块各一块2、双踪示波器一台3、连接线若干3.实验原理1)、AMI编译码实验原理框图AMI编译码实验原理框图2)、实验框图说明AMI编码规则就是遇到0输出0,遇到1则交替输出+1与-1。

实验框图中编码过程就是将信号源经程序后,得到AMI-A1与AMI-B1两路信号,再通过电平转换电路进行变换,从而得到AMI编码波形。

AMI译码只需将所有的±1变为1,0变为0即可。

实验框图中译码过程就是将AMI码信号送入到电平逆变换电路,再通过译码处理,得到原始码元。

4.实验步骤实验项目一AMI编译码(归零码实验)概述:本项目通过选择不同的数字信源,分别观测编码输入及时钟,译码输出及时钟,观察编译码延时以及验证AMI编译码规则。

1、关电,按表格所示进行连线。

1注:1、实验准备部分包括实验环境准备与实验所需知识点准备。

2、若就是单人单组实验,同组成员填无。

码,就是否能观察到恢复的位时钟信号,为什么?实验项目二AMI编译码(非归零码实验)概述:本项目通过观测AMI非归零码编译码相关测试点,了解AMI编译码规则。

1、保持实验项目一的连线不变。

2、开电,设置主控菜单,选择【主菜单】→【通信原理】→【AMI编译码】→【非归零码实验】。

将模块13的开关S3分频设置拨为0100,即提取256K同步时钟。

3、此时系统初始状态为:编码输入信号为256KHz的PN序列。

4、实验操作及波形观测。

参照项目一的256KHz归零码实验项目的步骤,进行相关测试。

一、实验过程记录2:非归零码实验基带信号+AMI输出基带信号+AMI_A12注:实验过程记录要包含实验目的、实验原理、实验步骤,页码不够可自行添加。

基带信号+AMI_B1基带信号+译码输出译码输出坏了基带信号+TH5编码输入时钟+译码输出时钟译码输出坏了归零码实验基带信号+AMI输出基带信号+AMI_A1基带信号+AMI_B1基带信号+译码输出译码输出坏了基带信号+TH5编码输入时钟+译码输出时钟译码输出坏了三、实验小结:实验报告成绩(百分制)__________ 实验指导教师签字:__________。

通信原理实验报告

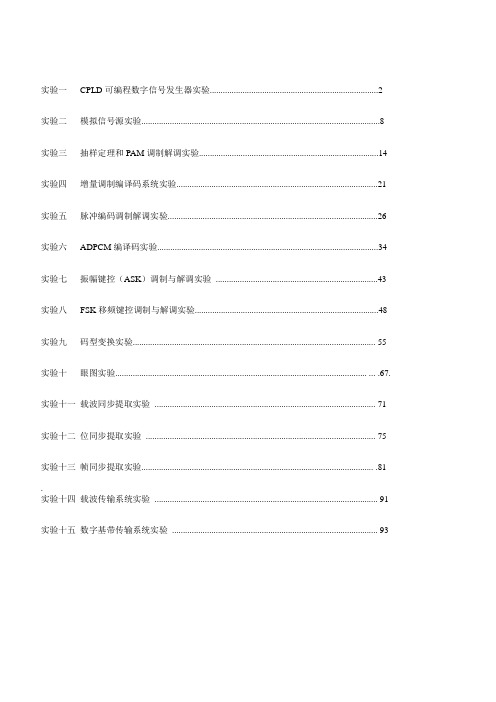

实验一CPLD可编程数字信号发生器实验 (2)实验二模拟信号源实验 (8)实验三抽样定理和PAM调制解调实验 (14)实验四增量调制编译码系统实验 (21)实验五脉冲编码调制解调实验 (26)实验六ADPCM编译码实验 (34)实验七振幅键控(ASK)调制与解调实验 (43)实验八FSK移频键控调制与解调实验 (48)实验九码型变换实验 (55)实验十眼图实验................................................................................................................... (67)实验十一载波同步提取实验 (71)实验十二位同步提取实验 (75)实验十三帧同步提取实验.......................................................................................................... .81 .实验十四载波传输系统实验 (91)实验十五数字基带传输系统实验 (93)实验一CPLD 可编程数字信号发生器实验一、实验目的1、熟悉各种时钟信号的特点及波形。

2、熟悉各种数字信号的特点及波形。

二、实验内容1、熟悉CPLD 可编程信号发生器各测量点波形。

2、测量并分析各测量点波形及数据。

3、学习CPLD 可编程器件的编程操作。

三、实验器材1、信号源模块一块2、连接线若干3、20M 双踪示波器一台四、实验原理CPLD 可编程模块用来产生实验系统所需要的各种时钟信号和各种数字信号。

它由CPLD可编程器件ALTERA 公司的EPM240T100C5、下载接口电路和一块晶振组成。

晶振JZ1 用来产生系统内的32.768MHz 主时钟。

1、CPLD 数字信号发生器包含以下五部分:1) 时钟信号产生电路将晶振产生的32.768MHZ 时钟送入CPLD 内计数器进行分频,生成实验所需的时钟信号。

位同步信号提取实验

实验五位同步信号提取实验一、实验目的1.掌握用数字环提取位同步信号的原理及对信息代码的要求。

2.掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念。

二、实验内容1.观察数字环的失锁状态、锁定状态。

2.观察数字环锁定状态下位同步信号的相位抖动现象及相位抖动大小与固有频差的关系。

3.观察数字环位同步器的同步保持时间与固有频差之间的关系。

三、实验器材1.信号源模块2.同步信号提取模块3.20M双踪示波器一台4.频率计(选用)一台四、实验步骤1.将信号源模块、同步信号提取模块小心地固定在主机箱中,确保电源接触良好。

2.插上电源线,打开主机箱右侧的交流开关,再分别按下两个模块中的开关POWER1、POWER2,对应的发光二极管LED001、LED002、D500、D501发光,按一下信号源模块的复位键,两个模块均开始工作。

3.将信号源模块的位同步信号的频率设置为15.625KHz(通过拨码开关SW101、SW102进行设置),将信号源模块输出的NRZ码设置为1、0交替码(通过拨码开关SW103、SW104、SW105进行设置)。

4.将同步信号提取模块的拨码开关SW501的第一位拨上,即将数字锁相环的本振频率设置为15.625KHz,然后将信号源模块输出的NRZ码从信号输入点“NRZ-IN”输入,按一下同步信号模块上的“复位”键,使单片机开始工作,以信号源产生的位同步信号“BS”为内触发源,用示波器双踪同时观察信号输出点“位同步输出”的信号与信号源中的“BS”信号。

5.特别注意的是,本模块只能提取NRZ码的位同步信号,而且当信号源模块中的位同步信号的频率偏离同步信号提取模块设置的数字锁相环的本振频率过远时,将无法正确提取输入信号的位同步信号。

本实验中数字锁相环共有15.625KHz、10KHz、8KHz、4KHz四种本振频率可供选择,分别对应拨码开关SW501的1、2、3、4位,实验时请注意正确选择。

编码器和译码器11shifter and counter271

11位移位寄存器和271位计数器——实验报告11位移位寄存器:一、实验步骤1)打开Modelsim SF 6.2b2)点击File→New→Source→Verilog进入程序编辑状态3)编辑11位移位寄存器的源代码4)按建进入保存键面,将程序命名为shifter.v(程序名应与代码中的编辑名一致),在D盘新建文件夹并命名为11shifter,选中该文件夹点击保存5)选择主菜单File→New→Source→Verilog进入程序编辑状态6)编辑11位移位寄存器的测试代码7)按建进入保存键面,将程序命名为shifter_tp.v(程序名应与代码中的编辑名一致),选中新建的11shifter点击保存8)选择主菜单File→New→Project,在弹出的建立新项目的对话框中,填入新项目的名称(shifter名称应与代码中的编辑名一致),及所在文件夹D:/11shifter,点击OK9)在新出现的对话框中点击Add Existing File将shifter与shifter_tp添加到新建的项目中,关闭对话框10)按进行编译,代码无误后,在Library界面选中work→shifter_tp,点击11)选中要检验的波形代码,点击右键,选择Add to Waves→Selected Signals加入被检验波形,选择中一个检验波形12)打开Quartus Ⅱ8.113)点击File→New Project Wizard在出现的界面完成新项目decoder_38的创建14)点击左上方出现的shifter,点击编译,成功后选中shifter点击右键选中Locate→Locatein RTL View,完成电路仿真二、源代码测试代码三、时序仿真结果四、综合结果五、结果分析仿真结果分析:11位移位寄存器设计了当clr=0时,执行清零功能;当load=0时,执行置数功能;位宽为11,由$random每20ns产生一个随机数使数字开始移位,每来一个上升沿移一位,执行语句为实验结果分析:产生的结果与理论一致,电路由一个D触发器和两个二选一数据选择器组成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验11 位同步提取实验

通信1301

王少丹

201308030104 一、实验目的

1.掌握数字基带信号的传输过程;

2.熟悉位定时产生与提取位同步信号的方法。

二、实验仪器

1.复接/解复接、同步技术模块,位号I

2.时钟与基带数据发生模块,位号:G

3.信道编码与ASK、FSK、PSK、QPSK调制,位号:A、B位

4.PSK QPSK解调模块,位号C

5.100M双踪示波器1台

三、实验原理

数字通信系统能否有效地工作,在相当大的程度上依赖于发端和收端正确地同步。

同步的不良将会导致通信质量的下降,甚至完全不能工作。

通常有三种同步方式:即载波同步、位同步和群同步。

在本实验中主要分析位同步。

实现位同步的方法有多种,但可分为两大类型:一类是外同步法;另一类是自同步法。

所谓外同步法,就是在发端除了要发送有用的数字信息外,还要专门传送位同步信号,到了接收端得用窄带滤波器或锁相环进行滤波提取出该信号作为位同步之用。

所谓自同步法,就是在发端不专门向收端发送位同步信号,而收端所需要的码元同步信号是设法从接收信号中或从解调后的数字基带信号中提取出来。

这种方法大致可分为滤波法和锁相法。

滤波法是利用窄带滤波器对含定时信息的归零二进制序列(通常占空比为50%)进行滤波,从中滤出所要的位同步分量,并整形、移相等处理,即可得到规则的位同步脉冲信号,但对于无定时信息的非归零

二进制序列,则先要进行微分和整流等变换,使之含有定时信息后,才能用窄带滤波器实施滤波。

锁相法是指利用锁相环来提取位同步信号的方法,本实验平台选用锁相法进行位同步提取的。

锁相法的基本原理是,在接收端采用鉴相器比较接收码元和本地产生的位同步信号的相位,如两者相位不一致,则鉴相器输出误差信号去控制本地位同步信号的相位,直至本地的位同步信号的相位与接收信号的相位一致为止。

数字锁相环是一个相位反馈控制系统,在数字锁相环中,由于误差控制信号是离散的数字信号不是模拟信号,因而受控的输出相位的改变是离散的而不是连续的;常用的数字锁相环的原理方框图如图11-1所示。

框图说明:

1.设要提取的同步时钟频率为f,则要求晶体振荡器的振荡频率为mf赫兹,其中m为分频器的分频系数。

2.窄脉冲形成器的作用是将振荡波形变成窄脉冲。

图中两个窄脉冲形成电路的输出信号要求刚好相差180°。

3.添门为常闭门,在没有滞后脉冲控制时,此门始终关闭,输出低电平;扣门为常开门,若无超前脉冲控制时,则来自晶体振荡器的脉冲信号顺利通过扣门。

晶振信号(频率为mf赫兹)经过或门到达m分频器,输出频率为f赫兹的脉冲信号。

该信号再经过脉冲形成电路,输出规则的位同步脉冲信号。

4.比相器的功能是比较接收码元与m分频器输出信号(即本地时钟信号)之间的相位关系,若本地时钟信号超前于接收码元的相位,则比相器输出一个超前脉冲,加到扣门,

扣除一个晶振脉冲,这样分频器的输出脉冲的相位滞后了1/m周期。

若本地时钟信号的相位滞后于接收码元的相位,比相器输出一个滞后脉冲,加到添门,控制添门打开,加入一个晶振脉冲到或门。

由于加到添门的晶振信号与加到扣门的晶振信号的相位相差Л,即这两路晶振信号脉冲在时间上是错开的,因此当从添门加入一个晶振脉冲到或门时,相当于在扣门输出的晶振信号中间插入了一个窄脉冲,也就使分频器输入端添加了一个脉冲,这样分频器输出相位就提前了1/m周期。

整个数字锁相环路按上述方式,反复调整本地时钟相位,以实现位同步。

从图11-2中,可清楚地理解添扣脉冲的原理。

至于数字锁相环的种类,目前比较统一的做法是按数字鉴相器的实现方法来对数字锁相环进行分类,通常分为下面四类:触发器型数字锁相环(FF-DPLL)、奈奎斯特型数字锁

相环(NR、DPLL)、过零检测式数字锁相环(ZC-DPLL)、超前滞后型数字锁相环(LL、DPLL)。

若从取样或者等效取样观点看,在第一、三、四类中输入信号相位是以受控的本地时钟相位为基准而确定的,本地时钟在受控过程中是变化的,因而属于非均匀取样的形式。

而在第二类中则不同,鉴相器输入信号相位是以固定速率的时钟信号为基准来确定的,属于均匀取样的形式。

位同步系统的性能通常是用相位误差、建立时间、保持时间等指标来衡量。

具体内容这里不详细解释,请查看有关资料。

本实验中运用CPLD芯片EPM240编程实现数字锁相环功能,待提取同步时钟的基带信号由39P01铆孔输入。

图11-3和图11-4为位同步时钟提取结构框图和电路原理图。

如图11-3所示,上述基带信号由39P01输入后,至位同步恢复与信码再生电路,进行位同步提取、信码再生功能。

测量点有39P06.39P07,其中39P06是同步时钟提取输出铆孔,39P07是信码再生基带信号输出铆孔。

四、各测量点和可调元件作用

复接/解复接、同步技术模块

39SW01:功能设置开关。

设置“0001”,为2K基带数据的同步时钟提取、再生功能。

设置“0011”,为32K基带数据的同步时钟提取、再生功能

39P01:外加基带信号输入铆孔。

39P06:提取同步时钟输出铆孔。

39P07:再生基带数据输出铆孔。

五、实验内容及步骤

1.插入有关实验模块

在关闭系统电源的情况下,按照下表放置实验模块:

对应位号可见底板右上角的“实验模块位置分布表”,注意模块插头与底板插座的防呆口一致。

2.信号线连接

使用专用导线按照下表进行信号线连接

3.加电

打开系统电源开关,底板的电源指示灯正常显示。

若电源指示灯显示不正常,请立即关闭电源,查找异常原因。

4.实验内容设置

拨码器“4SW02”(G)设置为“00001”,4P01产生32K的15位m序列输出;拨码器“39SW01”(I)设置为“0011”,“复接/解复接、同步技术模块”工作在32K码元同步功能;按动SW01(AB)按钮,使“L01”指示灯亮,“PSK DPSK”输出为PSK调制;将“PSK QPSK解调模块”两个跳线(38K01和38K02)开关插到左侧,选择PSK解调模式。

数字同步各测量点信号波形观察

按前面PSK实验,调整好电路状态,特别注意使“4P01”(G)与“38P02”(C)两点波形一致(可以反相),若不一致应调整38W01电位器。

调节38w01之后,波形基本一致,为后面的实验奠定了基础。

用示波器观测“39P06”(I)和“39P07”(I),记录提取的同步时钟和同步后的信号;

同步后的信号很稳定:

(3)用示波器观测“38P02”(C)和39P07”(I),对比同步前和同步后的数据(可以减小示波器的扫描时间,观察波形细节),分析其差别。

同步前码元相对时钟会有抖动,同步后的码元和时钟完全同步。

抖动在照片中不太明显,在示波器上观察可以明显看出绿色的非同步信号在超前的一小段距离中,信号抖动明显。

6.关机拆线

实验结束,关闭电源,拆除信号连线,并按要求放置好实验模块。

六、实验总结

位同步信号:

位同步的目的是使每个码元得到最佳的解调和判决。

位同步可以分为外同步法和自同步法两大类。

一般而言,自同步法应用较多。

外同步法需要另外专门传输位同步信息。

自同步法则是从信号码元中提取其包含的位同步信息。

自同步法又可以分为两种,即开环同步法和闭环同步法。

开环法采用对输入码元做某种变换的方法提取位同步信息。

闭环法则用比较本地时钟和输入信号的方法,将本地时钟锁定在输入信号上。

闭环法更为准确,但是也更为复杂。

位同步不准确将引

起误码率增大。

同步是数字通信中必须解决的一种重要的问题。

所谓同步,就是要求通信的收发双方在时间基准上保持一致,包括在开始时间、位边界、重复频率等上的一致。

数据通信中的位同步:

数据通信双方的计算机在时钟频率上存在差异,而这种差异将导致不同的计算机的时钟周期的微小误差。

尽管这种差异是微小的,但在大量的数据传输过程中,这种微小误差的积累足以造成传输的错误。

因此,在数据通信中,首先要解决的是收发双方计算机的时钟频率的一致性问题。

一般方法是,要求接收端根据发送端发送数据的起止时间和时钟频率,来校正自己的时间基准和时钟频率,这个过程叫位同步。

可见,位同步的目的是使接收端接收的每一位信息都与发送端保持同步。

目前实现位同步的方法主要有外同步法和自同步法两种:

1、外同步法。

外同步的方法是,发送端发送数据之前先发送同步时钟信号,接收方用这一同步信号来锁定自己的时钟脉冲频率,以此来达到收发双方位同步的目的;

2、自同步法。

接收方利用包含有同步信号的特殊编码(如曼彻斯特编码)从信号自身提取同步信号来锁定自己的时钟脉冲频率,达到同步目的。