DDR杂谈-training

DDR4电路及眼图分析讲解

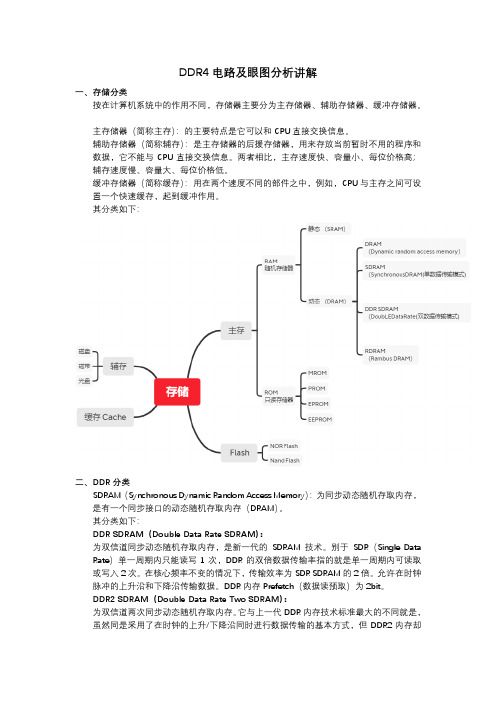

DDR4电路及眼图分析讲解一、存储分类按在计算机系统中的作用不同,存储器主要分为主存储器、辅助存储器、缓冲存储器。

主存储器(简称主存):的主要特点是它可以和CPU直接交换信息。

辅助存储器(简称辅存):是主存储器的后援存储器,用来存放当前暂时不用的程序和数据,它不能与CPU直接交换信息。

两者相比,主存速度快、容量小、每位价格高;辅存速度慢、容量大、每位价格低。

缓冲存储器(简称缓存):用在两个速度不同的部件之中,例如,CPU与主存之间可设置一个快速缓存,起到缓冲作用。

其分类如下:二、DDR分类SDRAM(Synchronous Dynamic Random Access Memory):为同步动态随机存取内存,是有一个同步接口的动态随机存取内存(DRAM)。

其分类如下:DDR SDRAM(Double Data Rate SDRAM):为双信道同步动态随机存取内存,是新一代的SDRAM技术。

别于SDR(Single Data Rate)单一周期内只能读写1次,DDR的双倍数据传输率指的就是单一周期内可读取或写入2次。

在核心频率不变的情况下,传输效率为SDR SDRAM的2倍。

允许在时钟脉冲的上升沿和下降沿传输数据。

DDR内存Prefetch(数据读预取)为2bit。

DDR2 SDRAM(Double Data Rate Two SDRAM):为双信道两次同步动态随机存取内存。

它与上一代DDR内存技术标准最大的不同就是,虽然同是采用了在时钟的上升/下降沿同时进行数据传输的基本方式,但DDR2内存却拥有两倍以上一代DDR内存预读取能力(即:4bit数据读预取)。

换句话说,DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以内部控制总线4倍的速度运行。

在同等核心频率下,DDR2的实际工作频率是DDR的两倍。

这得益于DDR2内存拥有两倍于标准DDR内存的4BIT预读取能力。

DDR3 SDRAM(Double Data Rate Three SDRAM):为双信道三次同步动态随机存取内存。

DDR简介专题培训课件

平面的矩阵纸,内存颗粒是由多片这样的 纸叠起来的。目前DDR3内存芯片基本上都 是8个L-Bank设计,也就是说一共有8个这 样的“表格”。

P-Bank & L-Bank

4個L-Bank要用BA[0:1] 8個L-Bank要用BA[0:2]

DDR3简介

什麽是DDR

• DDR即DDR SDRAM的簡稱

– Double Data Rate Synchronous Dynamic Random Access Memory即雙倍速率 同步动态随机存取存储器。

– SDR SDRAM采用单端(Single-Ended)时钟信号, 在一个时钟周期内只传输 一次数据;而 DDR由于工作频率比较快,采用可降低干扰的差分时钟信 号作为同步时钟。在一个时钟周期内可以传输两次数据,它能够在的DQS 上升沿和和下降沿各传输一次数据。

DDR2有4/8个L-bank DDR3有8个L-bank

• 模组的容量=芯片的容量×芯片个数 • 芯片的容量=存储单元数量×芯片位宽 • 存储单元数量=行数×列数(得到一个L-Bank的存储单元数量)×L-Bank的数量

P-Bank &芯片位宽

每颗芯片 位宽

传输速率

4GB 2R* 8 PC3L-12800S

1B = 1Byte=1字節 =8bit 1b = 1bit=1 比特

Logical Bank

寻址的流程是先确定目标地址所在的 Rank和L-Bank,接着要确定行(Row),然 后再确定列(Colum)。找到了存储单元后, 被选中的芯片就进行统一的数据传输。

DDR3芯片的内部是8个如同表格一样的 存储阵列,通过BA[0:2]来选择哪一个“表

DDR杂谈-training

优势:1. 降低主板成本,简易PCB设计;

2. 与颗粒“特性”相符,使DRAM处于最佳状态

Termination OFF

DRAM at

Active

Termination ON

DRAM at

Standby VTT

Controller DQ BUS

Reflection

25

DDRII 的新技术[3]:

Post CAS:

12

4、运行3D Mark。

测试波形[4]:

13

BUG – 8375X

During 8375X DDR test, clock signal of CLK_DDR4 & CLK_DDR4# act abnormally, it’s frequency float between 161.8MHz to 562.3MHz and voltage of this CLK signal only is half of normal one.

19

DDR vs DDRII (2):

封装:

DDR – TSOP (Thin Small Outline Package) 优点:芯片周围做出引脚,采用SMT

技术直接附着在PCB板表面,易焊接。适合高频应用, 操作较方便,可靠性较高,价格便宜。

缺点:焊点和PCB板的接触面积较小,使得芯片PCB

板传热相对困难;且由于TSOP的封装方式,使内存 在超过200MHz后过长的管脚会产生很高的阻抗和寄 生参数。严重影响了内存的稳定性和频率的提升。

Data Strobe CAS Latency Write Latency

封装 发热量 针脚模组

Single DQS 1.5 , 2 , 2.5

DDR的基础知识

DDR的基础知识1.电源DDR的电源可以分为三类:主电源VDD和VDDQ,主电源的要求是VDDQ=VDD,VDDQ是给IObuffer供电的电源,VDD是给但是一般的使用中都是把VDDQ和VDD合成一个电源使用。

有的芯片还有VDDL,是给DLL供电的,也和VDD使用同一电源即可。

电源设计时,需要考虑电压,电流是否满足要求,电源的上电顺序和电源的上电时间,单调性等。

电源电压的要求一般在±5%以内。

电流需要根据使用的不同芯片,及芯片个数等进行计算。

由于DDR的电流一般都比较大,所以PCB设计时,如果有一个完整的电源平面铺到管脚上,是最理想的状态,并且在电源入口加大电容储能,每个管脚上加一个100nF~10nF的小电容滤波.参考电源Vref,参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。

由于Vref一般电流较小,在几个mA~几十mA的数量级,所以用电阻分压的方式,即节约成本,又能在布局上比较灵活,放置的离Vref管脚比较近,紧密的跟随VDDQ 电压,所以建议使用此种方式。

需要注意分压用的电阻在100~10K均可,需要使用1%精度的电阻。

Vref参考电压的每个管脚上需要加10nF的点容滤波,并且每个分压电阻上也并联一个电容较好。

用于匹配的电压VTT(TrackingTermination Voltage)VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。

DDR的设计中,根据拓扑结构的不同,有的设计使用不到VTT,如控制器带的DDR器件比较少的情况下。

如果使用VTT,则VTT的电流要求是比较大的,所以需要走线使用铜皮铺过去.并且VTT要求电源即可以吸电流,又可以灌电流才可以。

一般情况下可以使用专门为DDR设计的产生VTT的电源芯片来满足要求.而且,每个拉到VTT的电阻旁一般放一个10Nf~100nF的电容,整个VTT电路上需要有uF 级大电容进行储能。

DELL服务器系统提示错误解决的若干办法

确保内存模块连接器干净并且在有效配置中安装支持的内存模块。请参阅内存模块一般安装原则。

DIMMs <x> disabled - MemBIST timeout

DIMMs <x> disabled - Rank not found

DIMMs <x> disabled - DIMM communication error

请确保引导模式设置正确,并且具有正确的可引导介质。请参阅"使用系统设置程序和UEFI引导管理器"。

Embedded NICxand NICy:

OS NIC=<ENABLED |DISABLED>, Management Shared NIC=<ENABLED |DISABLED>

操作系统NIC接口在BIOS中设置。在管理工具中设置了管理共享NIC接口。

请等待系统重新引导。

Alert! iDRAC6 not responding.

Power required may exceed PSU wattage.

Alert! Continuing system boot accepts the risk that system may power down without warning.

不支持的内存模块。

请确保内存模块安装在有效的配置中。请参阅内存模块一般安装原则。

DIMM mismatch: DIMM <x> Lockstep pair DIMM<y&z> disabled. Please replace the lockstep pair with matching DIMM(s).

ESMT DRAM_Training

ESMT

AC Specification I

ESMT

Page 8 ESMT Confidential

AC Specification II

ESMT

Page 9 ESMT Confidential

請參考附件(SD.ppt)_量測說明 請參考附件(SD.ppt)_量測說明 )_

ESMT

Page 21 ESMT Confidential

ESMT

Page 22 ESMT Confidential

Example:

ESMT

Page 23 ESMT Confidential

ESMT

Page 24 ESMT Confidential

ESMT DDR2 SDRAM:

ESMT

Page 25 ESMT Confidential

Pixelworks PW118 LSI 8602 DVR/DVB ST STM 5105 Genesis FLI8668 Marvell 88F5180N Router Broadcom BCM4712

8Mx16 8Mx16 8Mx16 16Mx16 8Mx16 8Mx16

ESMT

Page 11 ESMT Confidential

CS RAS CAS WE CLK CKE

Registers & Control Clocks

DC Generators

(VPP, VBB, IVC, VREF, etc.)

Vcc Vss

DQM

Row Decoder

Hale Waihona Puke Bank select Ai Refresh Control Circuits Row Address Buffer Col. Address Buffer Latency& burst length

DDR

3.常温测试比低温测试结果类似,wrcdc FAIL范围稍小

DQ Training相当于校准,测试完会计算一个平均值的值作为推荐值,可以把这阻值写进软件中。

因为只有左边wrcdc在100~45范围的窗口较大,计算出来的结果如下图,而高通推荐的范围是259~679,所以该项测试FAIL。

jedec_lpddr3_single_channel_CDC_Values_through_CDT中的最后CBD2部分。

3.我们总过做了四次测试,采用不同的测试工具和方法,得到的4个结果还是比较吻合的。

4.分析结论:

该芯片wrcdc时序余量较小,需要参考压力测试的结果,如果PASS,时序可以不该,如果FAIL,可以修改wrcdc的值。

5.第三项测试FIX_RD_CDC_Scan_WR_BYTE是我们需要的结果,我们目前的测试结果

稍有FAIL,高通认为是可以接受的。我们以后QDUTT部分只需要在常温下测试这一项就行。

四个测试的简单对比:

测试结果分析:

第一次测试:许鹏强1月5日结果

测试工具:QDUTT1.5.8

测试项目:DQ Training

P1项目佰维512M分离DDRBWMD3X32L7B-04GbQDUTT测试结果分析:

1.DDR测试包括压力测试和QDUTT眼图测试。

我们以压力测试结果为主,QDUTT测试结果为辅。这里撇开压力测试,单独分析下最近做的几次QDUTT的测试结果。

2.QDUTT是一个DDR眼图测试

用来判断代码中rdcdc,wrcdc这2个时序值和Rout数据线驱动电阻值的设置是否满足性能需求。具体的代码参考:

ddr3 学习分享

读/写

激活命令(active)

每次开始读写任务之前,Bank中的目标行必须进行激活命令,进入激活状态。 最多4个Bank可同时进入激活状态。 同一个Bank中不同行激活命令之前都需要进行Precharge命令。

读/写

当Bank中目标行激活后,就可以发出读/写命令。

过程:

首先确定行(包括片选及L-bank的确定),行有效命令,并使其处于激活状态; 然后确定列,列寻址信息与读/写命令同时发出。

DDR3 学习总结

Xieyu 2017.12.04

INDEX

MEMORY DDR3基本概念 DDR3工作机制

MEMORY

RAM

SRAM

DRAM

静态随机存储器 由触发器存储数据

动态随机存储器 MOS管栅极电容存储电荷

DRAM

SDRAM

DDR RRAM

单倍数据速率随机存储器 在时钟脉冲的上升沿读取数据速率动态存储器

而SR又分为:

1. 2.

局部自刷新

MR17来设置局部自刷新

Refresh&Precharge

Precharge(预充电):

DRAM工作时,L-BANK中只有一个行激活,当进行完读写操作后,在同一个LBANK操作时,关闭一行,打开另一行的过程称为预充电。 关闭行的过程,需要S-AMP对行内所有数据进行重写,地址进行复位。其过程 与REFRESH一样。

LPDDR3 pin脚定义

CK_t,CK_c CKE CS_n 差分时钟信号(Input) 时钟使能(Input) 片选(Input)

CA0-CA9

DQ0-15/31 DQS_t,DQS_c DM ODT ZQ Vdd/Vss

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

…… No Pain , No Gain!

Gain ?

15

DDR

&

DDRII 大 比 拼

16

内存的性能公式:

速度=宽度x频率

速度:表示内存的性能(MB/S) 宽度:表示内存接口的宽度(Bits) 频率:表示数据传输的频率(MHz)

提高内存传输数据的频率? 增加内存接口的宽度? 同时提升?

TBD

-1.2V

TBD

4.5V-ns Overshoot与VDD组成面积必须要≤

TBD

2.4V-ns

TBD

4.5V-ns Undershoot与GND组成面积必须要≤ TBD

2.4V-ns

8

测试波形[1]:

9

测试波形[2]:

10

SI 测试项目[2]:

AC Character:

Input slew rate (0.94V ~ 1.56V) VREF(ac)±0.31

缺点:成本高,

操作相对较难。

21

DDR vs DDRII (3):

电压:

DDR : +2.5V±0.2V for DDR200,266,333

+2.6V±0.1V for DDR400

DDRII : +1.8V± 0.1V

提供了明显的更小的功耗与更小的发热量

信号变化:

DQS – Data Strobe DDR : 单端信号传输 DDR II : 差分信号传输

SI Training :让每个人都有收获

DDR 雜談

Author: Summer ^-^

1

名词解释:

RAM – Random Access Memory SDRAM – Synchronous Dynamic RAM DDR SDRAM – Double Data Rate SDRAM DDRII SDRAM – Double Data Rate II Synchronous Dynamic Random Access Memory

12

4、运行3D Mark。

测试波形[4]:

13

BUG – 8375X

During 8375X DDR test, clock signal of CLK_DDR4 & CLK_DDR4# act abnormally, it’s frequency float between 161.8MHz to 562.3MHz and voltage of this CLK signal only is half of normal one.

原因:内存控制总线的控制状态是有限的,内存

即使在可存取状态时,有时无法同时对不同 的颗粒进行存取,CAS与RAS有时会产生冲突。

目的:提高内存的利用效率 方法:附加延迟技术(Additive Latency) – 在可能产生冲突

的地方,将CAS放在RAS后面的一个时钟周期, 因此ACT和CAS信号永远不会发生碰撞冲突。

一个电子管与一个 电容器组成一个位存储 单元,DRAM将每个内存 位作为一个电荷保存在 位存储单元中,用电容 的充放电来做储存动作

存储数据块较快, 且能与CPU外频保持 同步运行 ,可以取

消等待周期,减少 数据传输的延迟, 提升计算机的性能 和效率

需持续电力提供, 一旦系统断电,存 放的所有数据和程 序都会自动清空, 且无法恢复

DDR vs DDRII (1):

性能 -- 带宽 操作延迟 --

SDRAM组成:存储单元阵列 、输入/输出缓存器、 电源电路 、刷新电路

整个操作过程存在两种时间延迟: 建立行/列地址所需要的时间延迟; 建立两种行地址和列地址之间的最小时间间隔

(越低的内存延迟,能带来越高的性能)

o 保证4路传输的稳定流畅性,避开电气干扰与数 据冲突,采用了稍大于DDR的延迟设定。

Maybe this phenomenon is cause of DDR fail

(Only can detect half of DDR memory, that’s mean it only detect 256M)

14

Question:

Sleepy ?

…… No Pay , No Gain !

19

DDR vs DDRII (2):

封装:

DDR – TSOP (Thin Small Outline Package) 优点:芯片周围做出引脚,采用SMT

技术直接附着在PCB板表面,易焊接。适合高频应用, 操作较方便,可靠性较高,价格便宜。

缺点:焊点和PCB板的接触面积较小,使得芯片PCB

板传热相对困难;且由于TSOP的封装方式,使内存 在超过200MHz后过长的管脚会产生很高的阻抗和寄 生参数。严重影响了内存的稳定性和频率的提升。

+2.5V±0.2V for DDR200,266,333 +2.6V±0.1V for DDR400

6

DDR 工作步骤:

❖ 内存控制电路:

❖ (一般在北桥芯片组中)发出行地址选择信号(RAS)和列地址 选择信号(CAS)来指定哪一块存储体将被访问,这种两坐标寻

址方式决定了在访问一个单元的时候,与其相同行地址的其他 单元同样会被充电激活

22

DDRII 的新技术[1]:

OCD (Off-Chip Driver) –

离线驱动调整

DDRII通过调整上拉 (pull-up) /下拉 (pull-down)的电阻值使 两者电压相等。

V pull-up = V pull-down 通过减少DQ-DQS的倾斜来 提高信号的完整性,且通 过控制电压来提高信号品 质。

17

DDRII 工作原理:

DDR

DDRII

Memory Cell Array

r r

I/O r

Buffers

Memory Cell Array

r

I/O 2r

Buffers

DDRII完全实现了在不降低总频率 的情况下,将核心频率降低到100MHz, 从而很轻松实现更小的发热量,及更低 的电压的要求。

18

优势:1. 降低主板成本,简易PCB设计;

2. 与颗粒“特性”相符,使DRAM处于最佳状态

Termination OFF

DRAM at

Active

Termination ON

DRAM at

Standby VTT

Controller DQ BUS

Reflection

25

DDRII 的新技术[3]:

Post CAS:

0.75ns 0.80ns 0.85ns 0.90ns

Min. Hold time for command/address

0.75ns 0.80ns 0.80ns 0.80ns

11

测试波形[3]:

注:1、测量信号的set up time

分别取上升和下降延;

2、采样周期要大于300 Acps;

3、记录最小值;

(Strobe – 当总线的数据正确时,使之工作的一种选择信 号;允许电路在其输入端接收数据或在其输出端发送数据)

5

Pin 脚定义:

CK– Clock 差分;地址、控制信号、输出(读)数据信号 CKE – Clock Enable 高电平有效;为低时… DM – Data Mask 单向、为高时输入(写)数据掩盖 DQS – Data Strobe 输出端发送(读),输入端接收(写) BA0/1 – Bank Address 选中颗粒状态 RAS#/CAS#/WE# – Row Address / Column Address / Write CS# – Chip Select 认为是命令代码的一部分 VDD/VDDQ – Power Supply / DQ Power Supply

Address&Control Signal

Data Signal

定义 (Add&Con)

DDR333/400 DDR200/266

参数

定义(Data)

DDR333/400 DDR200/266

TBD

VDD+1.5V

允许的最大振幅– Overshoot

TBD

VDD+1.2V

TBD

-1.5V

允许的最大振幅– Undershoot

23

DDRII 的新技术[2]:

ODT (On-Die Termination) – 内建核心的终结电阻器

DDR – 终结电阻:

作用:为了防止数据线终端的反射信号,需要一定阻

值的终结电阻,终结电阻的大小决定了数据线的

的信噪比

信噪比和反射率;阻值过大 =〉线路

较高,但信号反射严重;阻值小 =〉减小信号

>= 1.0 V/ns (fast) >= 0.5 V/ns and < 1.0V/ns (slow) >= 0.4V/ns and < 0.5V/ns (derating) >= 0.5 V/ns and < 1.0V/ns (derating)

Min. Setup time for command/address

Data Strobe CAS Latency Write Latency

封装 发热量 针脚模组

Single DQS 1.5 , 2 , 2.5

1T TSOP

大 184 Pin / 200 Pin

Differential Strobe DQS 3+ , 4 , 5

Read Latency – 1 FBGA 小

优点:消除命令总线的冲突,提高命令总线和数据

总线的效率,从而实际提高了内存的带宽。