同步二十进制计数器1共30页文档

同步计数器及应用

同步计数器及应用为了提高计数器的工作频率、缩短传输延迟时间,希望计数器状态转换时所有需要翻转的触发器同时翻转,于是同步计数器便应运而生。

在同步计数器内部,各个触发器都受同一时钟脉冲——输入计数脉冲的控制,因此,它们状态更新是同时进行的,故被称为“同步计数器”。

同步计数器既可以用T'触发器组成,也可以用T触发器组成。

在使用T'触发器时,由时钟信号的有无控制触发器是否应翻转。

而在使用T触发器时,是否应当翻转由输入端T的状态决定。

因为T触发器只有一个输入端T,当T-l时,为计数状态;当丁-0时,保持状态不变,通常使用JK触发器构成T触发器。

1.同步二进制减法计数器根据二进制减法计数转换规律,最低位触发器FFo与加法计数器中FFo相同,每来一个计数脉冲翻转一次,应有Jo=Ko =1。

其他触发器的翻转条件是所有低位触发器的Q端全为O,应有Ji一Ki一Qo、J2一Kz一Qi Qo。

由三个JK触发器构成的T触发器构成的三位二进制同步减法计数器如图5. 16电路所示。

图中各触发器均由同一个CP时钟脉冲拉制,因此三个触发器的翻转就由其输入信号的状态决定。

从状态图可知随CP脉冲的递增,触发器的输出Q2 QiQo是递减的,且经过八个CP脉冲完成一个循环过程。

从图5.17(b)所示时序图可知:Qo端输出矩形信号的周期是输入CP信号的周期的两倍,所以Qo端输出信号的频率是输入CP信号频率的1/2,对应Q.端输出信号的频率是输入CP信号频率的114,因此N进制计数器同时也是一个N分频器,所谓分频就是降低频率,N分频器输出信号频率是其输入信号频率的N分之一。

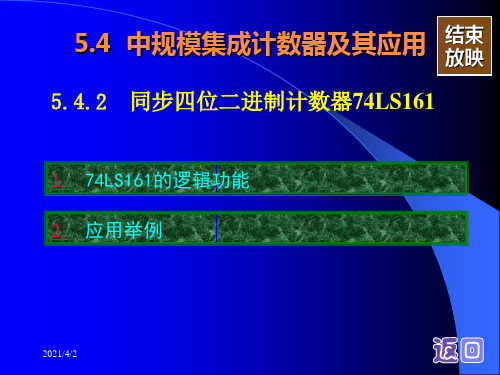

2.集成同步计数器74LS161 74LS161是同步四位二进制加法集成计数器,管脚排列如图5.18所示,逻辑功能如表5.7所示。

集成同步四位二进制加法计数器74LS161具有以下功能:复位端CR =o时,输出Q3 Q2 QiQo全为零,与CP无关,实现异步清零功能(又称复位功能)。

同步二进制计数器 计数规律

同步二进制计数器计数规律

哎呀呀,我是个小学生,这“同步二进制计数器计数规律”对我来说可太难懂啦!

老师在课堂上讲这个的时候,我感觉自己就像掉进了一个数字的大迷宫里。

什么是同步二进制计数器呀?它的计数规律又是啥?我瞪大眼睛,竖起耳朵,努力想要搞清楚。

我就想呀,这同步二进制计数器是不是就像我们排队跑步,一个接一个,有自己的顺序,不能乱?可这数字的队伍可比我们跑步复杂多啦!

老师说,同步二进制计数器的计数规律是按照二进制的规则来的。

二进制?那不是只有0 和1 嘛。

这就好像我们的开关,开就是1,关就是0 。

可在计数器里,它们可不是简单的开关,而是有着神奇的规律。

我看了看同桌,他也是一脸迷茫。

我忍不住问他:“你懂了吗?”他摇摇头说:“我感觉自己的脑袋都要变成浆糊啦!”可不是嘛,这也太难了!

再看看前面的学霸,人家好像听得津津有味。

我心里那个羡慕呀,我啥时候能像他一样厉害呢?

老师举了个例子,说就像上楼梯,每一步都有特定的数字变化。

我在心里想:这上楼梯谁不会呀,可这数字的楼梯怎么就这么难爬呢?

后来老师又详细地讲了讲,我好像有点明白了。

原来同步二进制计数器的计数规律就是从0 开始,一个一个地往上加,每次加1 ,数字的变化就按照二进制的规则来。

哎呀,我算是搞懂了一些,可还是觉得有点晕乎。

这知识就像一座大山,我才刚刚开始往上爬呢!不过我可不会轻易放弃,我一定要把它弄明白!

我觉得呀,学习这些难的知识就像一场冒险,虽然有时候会迷路,会遇到困难,但是只要坚持,总会找到出路,看到美丽的风景!。

二十进制加法计数器电路的设计

新疆大学课程设计报告所属院系:电气工程学院专业:电气工程课程名称:电子技术B课程设计设计题目:20进制加法计数器电路的设计班级:电气10-4班学生姓名:克依斯尔.卡合曼学生学号:20102101454指导老师: 王红琳努尔买买提完成日期:2014.01.13 —2014.01.2020进制加法计数器电路的设计1.设计目的(1)了解EDA技术的概念、发展及应用。

(2)掌握VHDL语言的基础知识,熟悉在数字电路系统设计中VHDL程序设计。

(3)学习MAX+PLUSⅡ软件的应用方法。

(4)应用EDA技术的设计方法完成(采用原理图和文本法两种方法实现),并在MAX+PLUSⅡ软件上仿真。

(5)需在实验室搭建电路验证并请认真按格式完成课程设计报告。

2.设计内容maxplus2MAX+PLUSII把这些设计转自动换成最终所需的格式。

其设计速度非常快。

对于一般几千门的电路设计,使用MAX+PLUSII,从设计输入到器件编程完毕,用户拿到设计好的逻辑电路,大约只需几小时。

设计处理一般在数分钟内完成。

特别是在原理图输入等方面,Maxplus2被公认为是最易使用,人机界面最友善的PLD开发软件,特别适合初学者使用。

EDA (Electronic Design Automation)EDA技术就是依靠功能强大的电子计算机,在EDA 工具软件平台上,对以硬件描述语言HDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、分割、综合、优化、仿真,直至下载到可编程逻辑器件CPLD/FPGA或专用集成电路ASIC芯片中,实现既定的电子电路设计功能。

2.2 电路的分析(1)创建电路文本图:(3)20进制计数器的原理图:(4)原理图输出波形图:可见当LD信号为“1”是不管CLK信号是什么都不工作。

只要LD为“0”是才能正常工作。

文本原理图其功能表如下:输入输出MR P3 P2 P1 P0 Q3 Q2 Q1 Q01 ×××××××0 0 0 0× d c b a d c b a0 0×××××加计数0 110 1 1 ××××减计数实验接线图:(5)结束语利用MAXPLUS2仿真软件完成了20进制加法计数器原理图及波形仿真,仿真结果与预期相符,实现了20进制的加法。

同步四位二进制计数器

0010

0011

十进制数50对应的二进制数为0011 0010

实现从0000 0000到0011 0001的50进制计数器

2021/4/2

15

作业题

5-8 5-9 5-10

2021/4/2

16

2012710反馈信号的拾取可利用与非门拾取状态sn1可利用进位输出co拾取状态11112012710电路举例以十进制计数器为例201271010图52374ls161构成十进制计数器改变d0110利用进位输出co取状态1111实现十进制计数0110到1111201271011图524用74ls161构成从0开始计数的十进制计数器改变与非门的输入信号可以实现其它进制计数

2021/4/2

8

④ 电路举例(以十进制计数器为例)

十进制计数器的计数状态顺序表

2021/4/2

9

图5-23 74LS161构成十进制计数器

利用进位输出CO取状态1111 令D3 D2 D1 D0=0110 实现十进制计数 (0110到1111)

改变D 2021/4/2 3 D2 D1 D0的状态,可以实现其它进制计数。10

实现四位二进制加法计数

2021/4/2

6

(2)构成16以内的任意进制加法计数器: ① 设计思想:利用脉冲反馈法 用 S0 , S1 , S2… , SM…SN 表 示 输 入 0 , 1 ,

2,…,N个计数脉冲CP时计数器的状态。 SM可以为S0,但需小于SN。

对于异步置数:在输入第N个计数脉冲CP后,通 过控制电路,利用状态SN产生一个有效置数信号,送 给异步置数端,使计数器立刻返回到初始的预置数状 态SM,即实现了SM~SN-1计数。

对于同步置数:在输入第N-1个计数脉冲CP时, 利用状态SN-1产生一个有效置数信号,送给同步置数控 制端,等到输入第N个计数脉冲CP时,计数器返回到 初始2021的/4/2 预置数状态SM,从而实现SM~SN-1计数。 7

eda实验考试二十进制计数器

EDA考试实验报告姓名:班级:电子学号:112092题目:设计一个带计数使能、同步复位、带进位输出的增1二十进制计数器,结果由共阴极七段数码管显示。

一、实验目的1考察对计数器程序的掌握程度2考察对设计的程序进行编译、仿真以及下载到试验箱上进行验证的过程二、源程序Library ieeeUseieee.std_logic_1164.all;Useieee.std_logic_unsigned.all;entity counter isport(clk,clk1,clr,en:in std_logic;co:outstd_logic;ledout:outstd_logic_vector(6 downto 0);scanout:outstd_logic_vector(1 downto 0));end counter;architecturertl of counter issignalcnt:std_logic_vector(4 downto 0);signalscan:std_logic_vector(1 downto 0):="01";signalhex:integer range 0 to 9;signalgewei,shiwei:integer range 0 to 9; beginprocess(clk)beginif(clk'event and clk='1')thenifclr='1' thencnt<=(others=>'0');elsif en='1' thenifcnt="10011" thencnt<="00000";co<='1';elsecnt<=cnt+'1';co<='0';end if;end if;end if;end process;process(cnt)begincasecnt iswhen"00000"=>gewei<=0;shiwei<=0;when"00001"=>gewei<=1;shiwei<=0;when"00010"=>gewei<=2;shiwei<=0;when"00011"=>gewei<=3;shiwei<=0;when"00100"=>gewei<=4;shiwei<=0;when"00101"=>gewei<=5;shiwei<=0;when"00110"=>gewei<=6;shiwei<=0;when"00111"=>gewei<=7;shiwei<=0;when"01000"=>gewei<=8;shiwei<=0;when"01001"=>gewei<=9;shiwei<=0;when"01010"=>gewei<=0;shiwei<=1;when"01011"=>gewei<=1;shiwei<=1;when"01100"=>gewei<=2;shiwei<=1;when"01101"=>gewei<=3;shiwei<=1;when"01110"=>gewei<=4;shiwei<=1;when"01111"=>gewei<=5;shiwei<=1;when"10000"=>gewei<=6;shiwei<=1;when"10001"=>gewei<=7;shiwei<=1;when"10010"=>gewei<=8;shiwei<=1;when others=>gewei<=9;shiwei<=1;end case;end process;process(clk1)beginif(clk1'event and clk1='1')thenif(scan=”00” or scan=”11”)thenscan=”01”;elsescan<=not scan;end if;end if;end process;hex<=gewei when scan ="01" else shiwei;with hex selectledout<="0111111" when 0,"0000110" when 1,"1011011" when 2,"1001111" when 3,"1100110" when 4,"1101101" when 5,"1111101" when 6,"0000111" when 7,"1111111" when 8,"1101111" when others;scanout<=scan;endrtl;三、实验结果及分析仿真结果管脚配置实验分析:。

同步四位二进制计数器

2021/4/2

8

④ 电路举例(以十进制计数器为例)

十进制计数器的计数状态顺序表

2021/4/2

9

图5-23 74LS161构成十进制计数器

利用进位输出CO取状态1111 令D3 D2 D1 D0=0110 实现十进制计数 (0110到1111)

改变D 2021/4/2 3 D2 D1 D0的状态,可以实现其它进制计数。10

有进位时,高位计数功能T =1; 无进位时,高位保持功能T =0。

2021/4/2

13

用两片CT74LS161级联成16×16进制同步加法计数器

低位片

高位片

在计到1111以前,CO1=0,高位片保持原状态不变

在计到1111时,CO1=1,高位片在下一个CP加一 ② 再用脉冲反馈法

2021/4/2

14

状态 输出

图3-35 74LS161的外引线图CP输入图3-36 74LS161的逻并辑符行号 输入

表5-14 74LS161的功能表

异步清0功 能最优先

CP上升 沿有效

2021/4/2

同步并 行置数

CO= Q3 Q2 Q1 Q0 CTT

4

2021/4/2

图5-22 74LS161的时序图

5

2.应用举例 (1)同步二进制加法计数

对于同步置数:在输入第N-1个计数脉冲CP时, 利用状态SN-1产生一个有效置数信号,送给同步置数控 制端,等到输入第N个计数脉冲CP时,计数器返回到 初始2021的/4/2 预置数状态SM,从而实现SM~SN-1计数。 7

② 分析74LS161的置数功能:

③ 反馈信号的拾取 可利用与非门拾取状态SN或SN-1 可利用进位输出CO拾取状态1111

数字逻辑 同步计数器共38页文档

11、获得的成功越大,就越令人高兴 。野心 是使人 勤奋的 原因, 节制使 人枯萎 。 12、不问收获,只问耕耘。如同种树 ,先有 根茎, 再有枝 叶,尔 后花实 ,好好 劳动, 不要想 太多, 那样只 会使人 胆孝懒 惰,因 为不实 践,甚 至不接 触社会 ,难道 你是野 人。(名 言网) 13、不怕,不悔(虽然只有四个字,但 常看常 新。 14、我在心里默默地为每一个人祝福 。我爱 自己, 我用清 洁与节 制来珍 惜我的 身体, 我用智 慧和知 识充实 我的头 脑。 15、这世上的一切都借希望而完成。 农夫不 会播下 一粒玉 米,如 果他不 曾希望 它长成 种籽; 单身汉 不会娶 妻,如 果他不 曾希望 有小孩 ;商人 或手艺 人不会 工作, 如果他 不曾希 望因此 而有收 益。-- 马钉路 德。

6、最大的骄傲于最大的自卑都表示心灵的最软弱无力。——斯宾诺莎 7、自知之明是最难得的知识。——西班牙 8、勇气通往天堂,怯懦通往地狱。——塞内加 9、有时候读书是一种巧妙地避开思考的方法。——赫尔普斯 10、阅读一切好书如同和过去最杰出的人谈话。——笛卡儿

Thank Байду номын сангаасou

二进制计数器

图5-17 4位二进制同步加法计数器74LS161的逻辑符号

如表5-6所示为74LS161的功能表。

清零 RD 0 1 1 1 1

预置 LD × 0 1 1 1

使能

EP ET ××

××

0× ×0

1

1

表5-6 74LS161的功能表

J1 J2

K1 K2

Q0 Q0Q1

J3 K3 Q0Q1Q2

由于该电路的驱动方程规律性较强,只需用“观察法”就 可画出时序波形图或状态转换表(参见表5-4)。

表5-4 4位二进制同步加法计数器的状态转换表

计数脉冲序号 0 1 2 3 4 5 6

电路状态 Q3Q2Q1Q0 0000 0001 0010 0011 0100 0101 0110

如图5-11所示为JK触发器组成的4位异步二进制加法计数器的 电路结构。

图5-11 4位异步二进制加法计数器的电路结构

图5-11中,将JK触发器连接成T触发器(即 J K 1 )的 形式,最低位触发器 FF0的时钟脉冲输入端接计数脉冲CP,其 他触发器的时钟脉冲输入端接相邻低位触发器的Q端。

由于该电路的连线简单且规律性强,因此无须用前面介绍的 分析步骤进行分析,只需进行简单的观察与分析就可画出时序波 形图和状态转换图,这种分析方法称为“观察法”。

2)二进制同步减法计数器

如表5-5所示为4位二进制同步减法计数器的状态转换表。

计数脉冲序号

电路状态 Q3Q2Q1Q0

等效十进制数

0

0000

0

1

1111

15

2

1110

14

3